什么样的 TiN 结出什么样的 W?

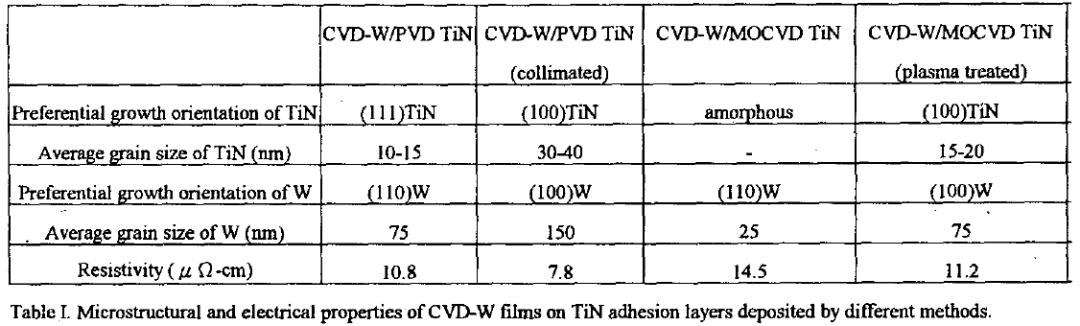

不同的 TiN 衬底,会得到什么样的 CVD-W 呢?研究发现,CVD-W 薄膜的生长取向与 TiN 底层的微观结构呈强相关性;CVD-W 的晶粒尺寸随底层 TiN 晶粒尺寸的增大而增大,其电阻率则随底层 TiN 晶粒尺寸的增大而降低。

与其他难熔金属相比,化学气相沉积钨(CVD-W) 具备优异的抗电迁移性能,在高深宽比接触孔与通孔结构中也能实现良好的台阶覆盖,因此已被广泛应用于超大规模集成电路(VLSI) 的多层金属化工艺中。但为了改善钨(W)与二氧化硅(SiO2)之间的粘附性能,必须引入一层金属粘合层。

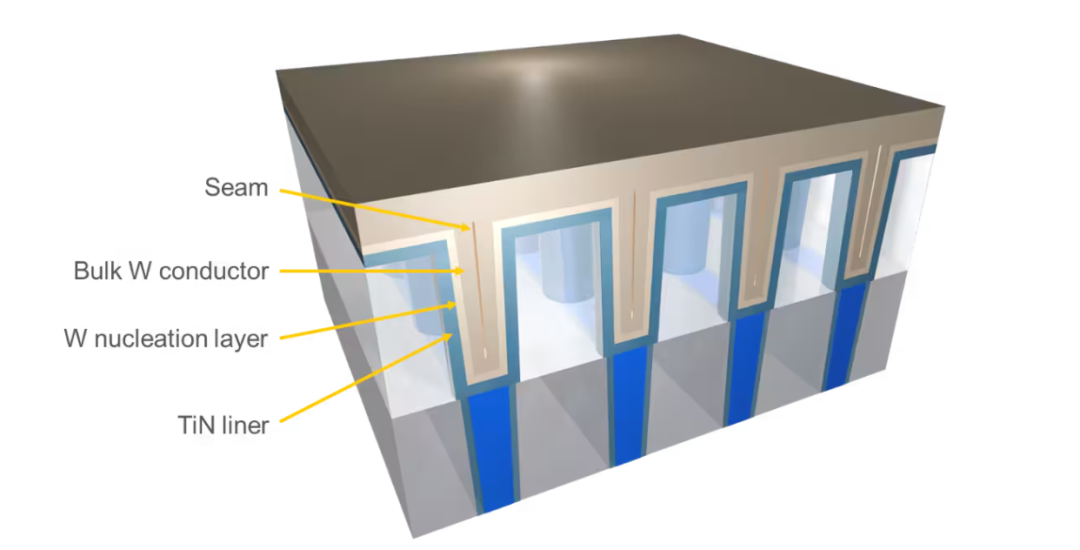

化学气相沉积(CVD)钨沉积工艺(来源:AMAT)

衬里阻挡层通常由氮化钛(TiN)制成,它能很好地附着在通孔侧壁上,防止分层和空洞等缺陷。由于钨不会自然生长在氮化钛表面,因此在钨本体填充前需沉积一层钨成核层。氮化钛衬里和钨成核层就像一个模具,为钨触点界定了空间(见图2)。尽管该模具占据了通孔的大部分空间,但由于其电阻远高于本体钨,它几乎不具备电子传导能力。

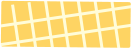

氮化钛(TiN)是超大规模集成电路制造工艺中极具实用价值的扩散阻挡层,同时也能满足改善 CVD-W 与 SiO2 绝缘层之间粘附性能的核心需求。为了提升传统物理气相沉积(PVD)制备的 TiN 在亚微米接触孔填充中的台阶覆盖能力,业界已开发出多种沉积工艺,例如准直物理气相沉积、化学气相沉积(CVD)制备 TiN 等。现有研究表明,TiN 薄膜的晶体取向由沉积工艺与薄膜厚度共同决定;而 TiN 粘附层的初始生长状态,会对后续沉积的 CVD-W 的微观结构与电学性能产生显著影响。针对具有不同择优生长取向的 TiN 粘附层,Properties of CVD-W Overgrowth on PVD and MOCVD TiN Layers 这篇文章系统探究了其上生长的 CVD-W 薄膜的微观结构与电学性能,并报道了相关研究结果。

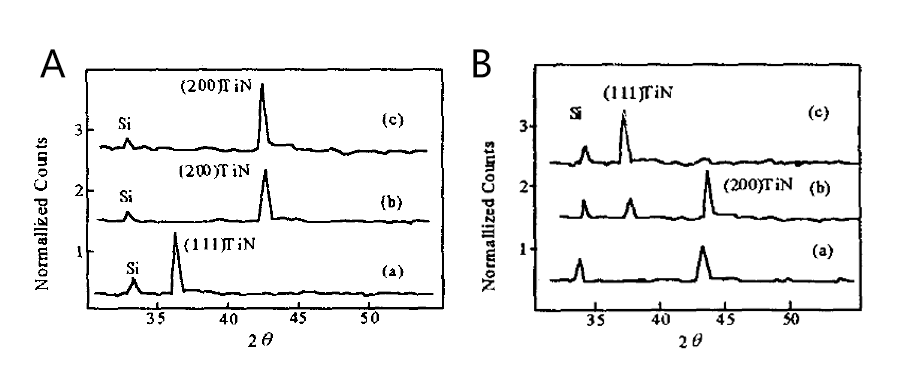

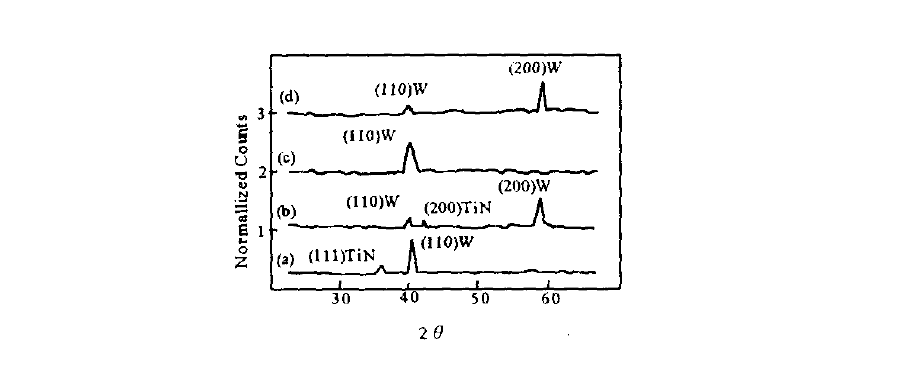

研究发现,传统物理气相沉积(PVD)制备的 TiN 薄膜,其择优生长取向随薄膜厚度发生规律性变化:对于超薄 TiN 样品,[001] 晶向的择优生长源于该晶面在所有晶面中具有最低的表面能;随着薄膜厚度增加,应变能成为主导因素,促使 TiN 转为 [111] 晶向择优生长。

对于准直 PVD 工艺制备的 TiN,仅观测到 [001] 晶向的择优生长,且该取向不随膜厚发生改变。研究认为,准直 PVD 沉积过程中的高功率工艺使 TiN 形成了大晶粒结构,进而抑制了其择优取向随膜厚的转变。

对于沉积态金属有机化学气相沉积(MOCVD)TiN 薄膜,由于样品中存在较高的碳污染,其晶体结构呈非晶态。采用间歇式原位等离子体处理可显著降低薄膜中的碳污染,经等离子体处理后的 MOCVD TiN 薄膜呈现 [001] 晶向择优生长;这一现象源于等离子体处理释放了薄膜内的应力,使表面能成为主导薄膜生长的核心因素。

研究发现,CVD-W 薄膜的生长取向与底层 TiN 的微观结构呈强相关性。在 (111) 晶向 TiN 与非晶态 TiN 上生长的 CVD-W,其择优生长取向为 (110) 晶面 ——(110) 晶面是体心立方(bcc)结构钨的最密排晶面,在上述 TiN 基底上具有最低的界面能。与之相反,在准直 PVD 或等离子体处理 MOCVD 工艺制备的 (100) 晶向 TiN 上,CVD-W 呈现 (100) 晶面择优生长;(100) 晶面钨与 (100) 晶面 TiN 之间的低晶格失配,显然是 (100) 晶向钨在 (100) 晶向 TiN 基底上定向生长的主导因素。

CVD-W 的晶粒尺寸随底层 TiN 晶粒尺寸的增大而增大,其电阻率则随底层 TiN 晶粒尺寸的增大而降低。在高功率准直溅射制备的 TiN 基底上,钨薄膜的电阻率达到最低值。钨薄膜电阻率与晶粒尺寸的这一关联规律,可通过钨薄膜中电子的平均自由程约为 40 nm 这一特性得到合理解释。

来源:Properties of CVD-W Overgrowth on PVD and MOCVD TiN Layers.

集成电路中的PVD技术路线——从long throw到IMP

二氯二氢硅(DCS)在半导体工艺中的应用

Merck KGaA | 如何进行钼 (Mo) 的 ALD?

MIT Open Course | 什么是化学气相沉积?

MIT Open Course | 什么是物理气相沉积?

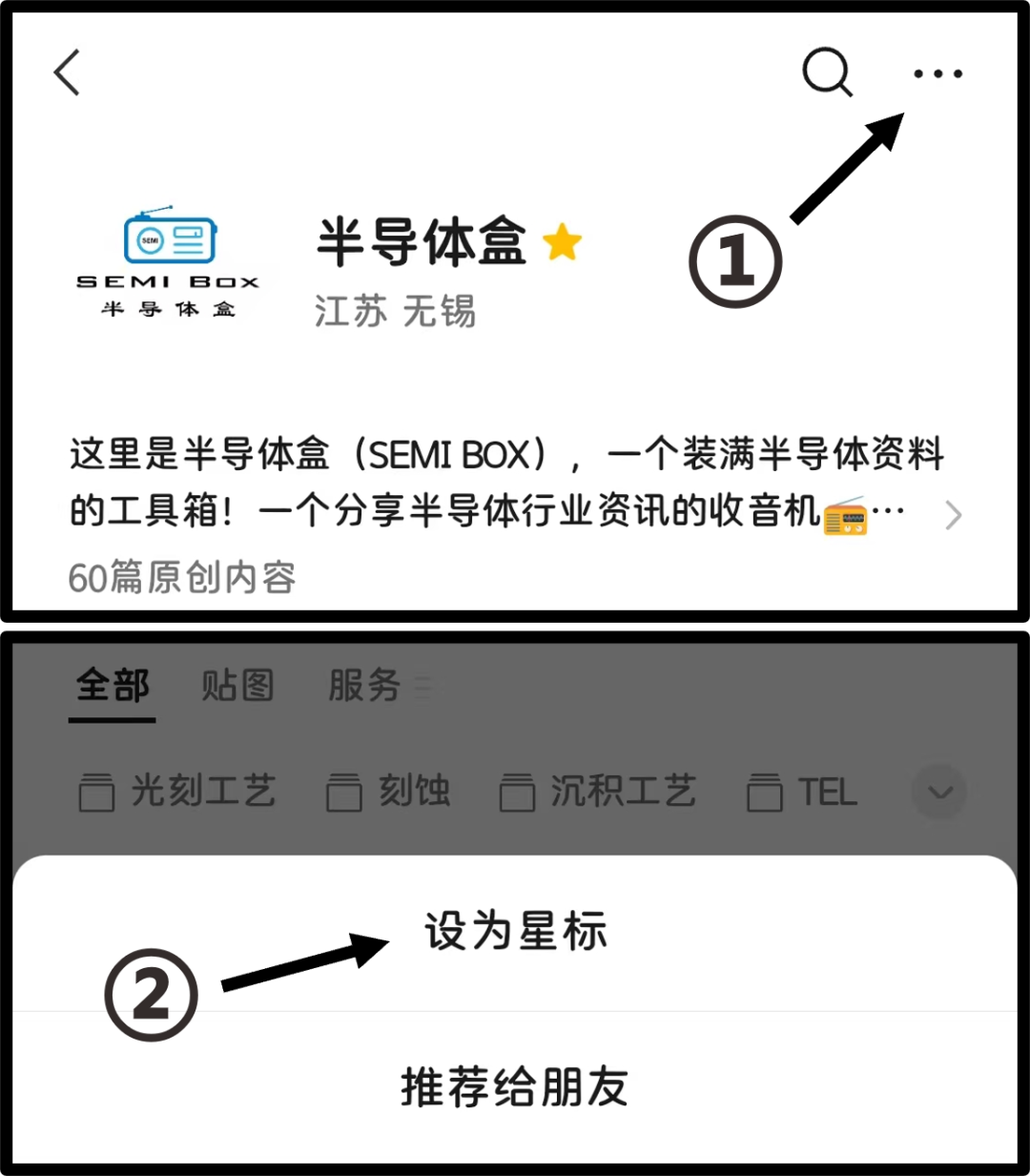

↓设置星标,精彩不错过↓

↓扫一扫,总一款适合你↓

本文仅作行业信息分享、技术交流,不涉及任何涉密内容。

欢迎关注本公众号,获取更多半导体设备、工艺、产业动态。

如有疏漏、内容建议,欢迎留言交流。