如何给芯片做 CT ?

编译自 The X-Ray Tech That Reveals Chip Designs,侵删。

在烤制蛋糕时,我们很难判断蛋糕内部是否达到了理想状态。微电子芯片领域亦是如此,且风险要高出许多:工程师该如何确认芯片内部的实际设计完全契合研发初衷?半导体设计企业要怎样判定自身的知识产权是否遭到窃取?更令人担忧的是,人们该如何确保芯片中没有被暗中植入终止开关或其他硬件木马?

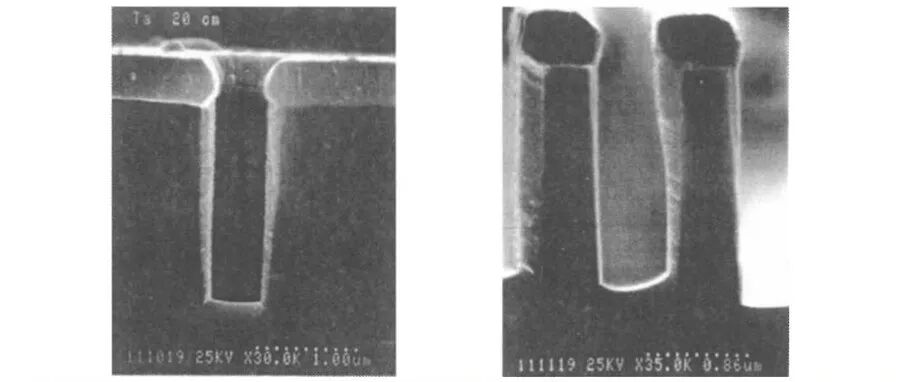

如今,这类探测操作需要逐层打磨剥离芯片的多层结构,再借助电子显微镜进行观测。该方式进度缓慢,且属于破坏性检测,因此很难满足各方的使用需求。

两位作者中,Levi 专注于半导体领域研究,Aeppli 则深耕 X 射线相关方向。在深入思考这一难题后,我们萌生了利用 X 射线对芯片进行无损成像的想法。这需要突破医用 X 光扫描仪的现有分辨率限制,但我们明确判断,所需的超高分辨率完全能够实现。至此,我们所命名的 “芯片扫描” 项目正式诞生。

数年之后,我们终于实现了在不损毁芯片的前提下,绘制出即便最先进、结构最复杂处理器的完整互联架构。目前,这套流程耗时超过一天,但未来数年内的技术优化,将有望把整块芯片的架构测绘时长缩短至数小时内。

我们的第一项技术——叠衍射X射线计算机断层扫描技术,率先在一块22纳米英特尔处理器的局部区域完成测试,成功构建出芯片互连结构的精细三维影像。南加州大学同步辐射光源芯片扫描研究团队

这项名为叠层衍射X射线分层成像(ptychographic X-ray laminography)的技术,需要依托全球顶尖的高能 X 射线光源设备。而巧合的是,这类尖端设施大多毗邻高端芯片设计研发的核心区域。因此,随着该技术的普及应用,任何芯片缺陷、故障隐患以及恶意篡改手段都将无处遁形。

确定研发该技术路线后,我们的首要任务是摸清当前前沿X射线技术的实际能力上限。相关测试在瑞士 Paul Scherrer Institute 完成,团队成员 Aeppli 就职于该机构。研究所内建有瑞士光源同步辐射装置,这也是目前全球已建成的 15 座超高亮度相干 X 射线光源之一。

相干 X 射线与医院、牙科诊所使用的普通X射线存在本质区别,原理类似于激光笔高度定向的光束,与白炽灯向四面八方发散的光线之间的差异。瑞士光源及同类装置的工作原理为:先将电子加速至接近光速,再通过磁场偏转电子运动轨迹,进而激发产生高相干性的X射线光子束。

为验证瑞士光源的实际应用效果,我们组建的跨学科团队从当地门店花费约 50 美元购入一块英特尔奔腾 G3260 处理器,拆除外壳封装以裸露内部硅片。这款中央处理器采用 22 nm 互补金属氧化物半导体鳍式场效应晶体管工艺制造。

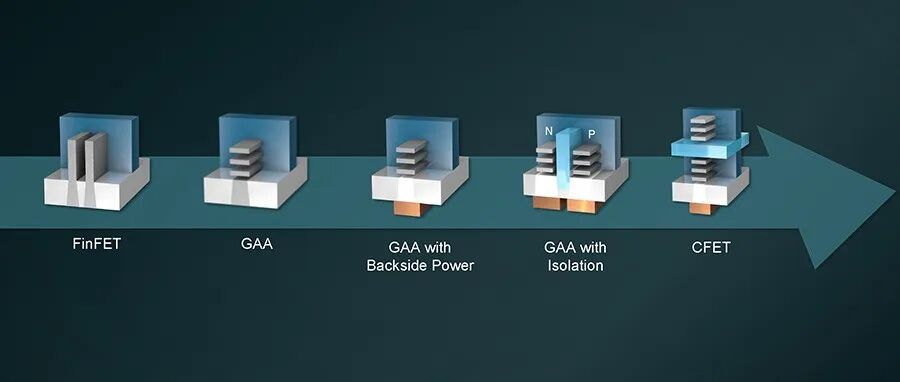

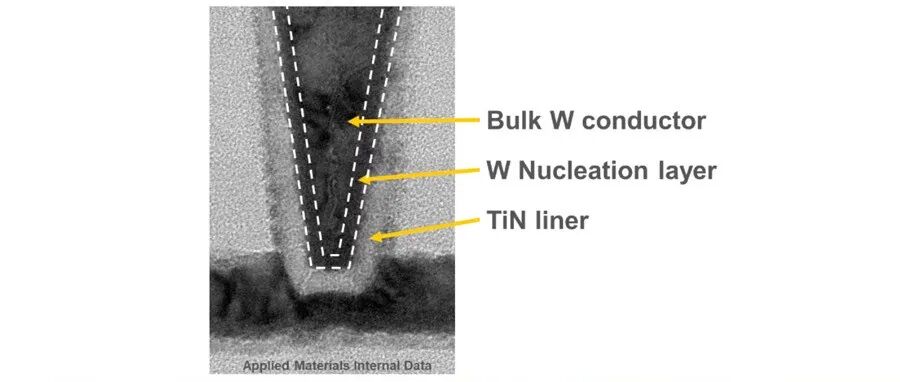

与所有同类芯片一样,G3260 处理器的晶体管由硅制成,但依靠金属互连线路的排布将晶体管连接起来,进而形成电路。在现代处理器中,互连线路的堆叠层数超过15 层,从上方俯瞰,其布局如同城市的街道网格地图。更贴近硅基底的底层线路结构极其精密,目前最先进的芯片中,底层线路的间距仅为nm级别。沿着互连线路层层向上,线路结构会变得愈发稀疏、尺寸更大,直至最顶层,顶层的电接触焊盘负责将芯片与封装外壳连通。

我们的检测工作,首先从 G3260 芯片上切割出一个 10 微米宽的柱状样本。采用这种破坏性操作,是为了大幅简化检测流程。10 微米的尺寸小于同步辐射光源光子半数的穿透深度,因此借助如此细小的样本,我们能够捕捉到足量穿过柱状样本的光子,从而解析其内部结构。

研究人员将样本放置在机械载物台上,使其可围绕柱状轴心旋转,随后从样本侧面发射一束相干 X 射线。样本旋转的同时,利用多组宽度为 2 微米、相互重叠的光斑对其进行扫描照射。

在每一处照射点位,相干X射线穿过芯片错综复杂的多层铜互连线路时会发生衍射,进而在探测器上投射出衍射图样,所有图样会被储存,用于后续数据分析处理。这些采集到的投影数据,包含了X射线穿透路径上材料的完整信息,可依托这些信息还原出物体的三维结构。该检测技术被称为叠衍射X射线计算机断层扫描(PXCT)。叠衍射成像技术,是一种依托光线穿透物体产生的干涉图样,通过算法运算重构物体影像的技术。

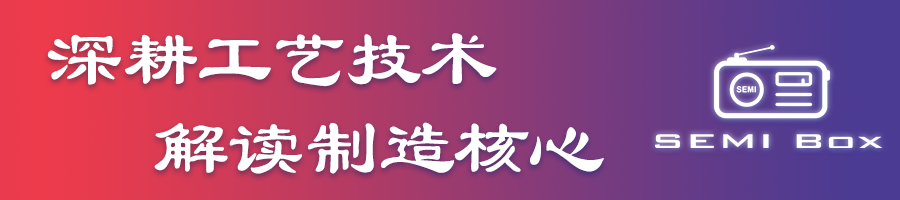

PXCT 的底层原理相对简单,与光的狭缝衍射原理相似。大家或许还记得基础物理课程中的知识:将一束相干光透过狭缝照射到远处平面上,会形成一种名为夫琅禾费衍射的图样。该图样由明暗相间的条纹构成,条纹间距与光的波长和狭缝宽度的比值成正比。

一些较为简单的X射线衍射效应,足以揭示关键信息,从而解析出纳米级结构。从狭缝【左上】发射X射线,可在探测器【上方蓝色区域】投射出经典的夫琅禾费衍射图样。将狭缝替换为两个点状物体【中左位置】,且二者间距小于狭缝宽度,便会投射出截然不同的图样【中间红色区域】。若将点状物体置于狭缝内部,两种干涉图样会相互叠加融合【下方深紫色区域】。微调狭缝内点状物体的位置【左下】,即可生成全新的组合干涉图样【浅紫色区域】。多组此类干涉图样结合分析,便能确定X射线传播路径中物体的分布位置。

倘若不再让光线穿过狭缝,而是照射在两个间距极小、尺寸微小近乎质点的物体上,便会形成截然不同的图样。无论这两个物体处于光束中的哪个位置,只要彼此间距保持不变,即便改变摆放位置,生成的图样也不会发生变化。

单独依靠上述两种现象,都无法还原芯片内部错综复杂的互连线路结构。但将二者结合,便能理解其工作原理。将两个微小物体放置在狭缝内部,最终形成的干涉图样会同时受到狭缝与物体的双重衍射作用,进而反映出狭缝宽度、物体间距以及物体与狭缝相对位置的相关信息。轻微移动两个质点,干涉图样就会随之偏移,而正是借助这种偏移,我们能够精准计算出物体在狭缝内的具体位置。

所有实际待测样本都可视为无数质点的集合,这些质点会形成复杂的X射线散射图样。通过分析这类图样,就能推断出质点在二维空间中的排布方式。若在光束中旋转样本,结合该原理还可实现物体的三维结构测绘,这一过程被称作断层重建。

实验过程中,必须做好设备布设,采集充足数据,才能以目标分辨率完成结构测绘。分辨率由 X 射线波长、探测器尺寸以及多项其他参数共同决定。我们依托瑞士同步辐射光源开展初期检测实验时,采用波长 0.21 nm 的X射线,需将探测器放置在距离样本约 7 米的位置,才能达到 13 nm 的目标分辨率。

2017年3月,研究团队发布了英特尔奔腾 G3260 处理器内部铜互连线路的高清三维成像结果,以此验证了PXCT技术可应用于集成电路的无损检测成像。这些图像清晰展现了这款互补金属氧化物半导体集成电路中,电路互连线路的三维形态与复杂结构,同时还捕捉到诸多关键细节,例如层间金属连接的缺陷、铜线路与周边二氧化硅绝缘介质接触面的粗糙程度等。

仅从此次原理验证实验就能看出,该技术在失效分析、设计验证与质量检测领域具备巨大应用潜力。为此,研究团队利用PXCT技术,对采用其他企业工艺制造的同款尺寸芯片切片样本开展检测。重建生成的三维影像细节独一无二,如同集成电路的专属“指纹”,同时还能充分反映芯片的制造工艺特征。

初期的成功让我们倍受鼓舞。但我们清楚,还能做得更好:研发全新类型的 X 射线显微镜,并结合芯片设计与制造信息,探索更高效的图像重构优化方案。我们将这项新技术命名为 PyXL,即叠层衍射 X 射线断层成像技术的缩写。

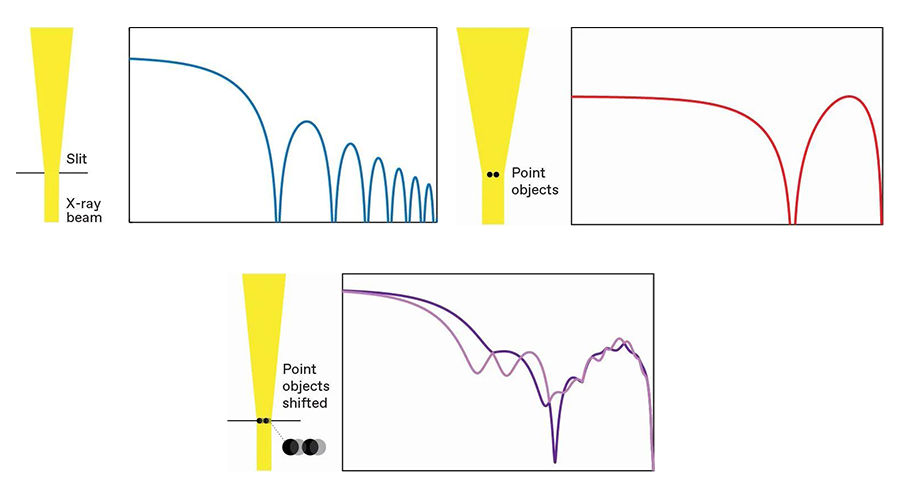

在侧视角度下,这块【橙色】芯片厚度过大,X光无法穿透。但将芯片倾斜一定角度(见中心θ角位置),其横截面厚度便会缩减至X光可穿透范围。承载芯片的机械载台(未展示)会带动样品在X光光束内绕Z轴旋转,进而在探测器上投射出干涉图样,依托该图样即可重建芯片的互连结构。

首要难题是,X 射线的穿透深度仅约 30 微米,如何完成整块 10 毫米宽芯片的扫描。我们先将芯片相对射线束倾斜一定角度,以此突破限制。随后,围绕垂直于芯片平面的轴线旋转样品,同时以光栅扫描的方式横向移动样品,最终让射线束能够覆盖芯片的全部区域。

在整个扫描过程中,穿透芯片的X射线会被集成电路内部的材料散射,进而形成衍射图样。与叠层衍射计算机断层扫描技术原理一致,重叠照射区域产生的衍射图样,会包含X射线穿透路径的冗余信息。再通过成像算法,推演与所有实测衍射图样匹配度最高的结构模型,依托该模型,我们就能完整重构出整块芯片的三维内部结构。

毋庸置疑,研发一款新型显微镜需要攻克诸多难题。设备需具备稳定的机械结构,搭载高精度位移平台与位置检测模块;同时还要精准记录射线束对芯片各个区域的照射方式,以及实时生成的衍射图样。为解决上述各类实际问题,一支由 14 名工程师和物理学家组成的团队协同攻坚。此外,受 PyXL 独特成像结构的限制,我们还需研发全新的数据解析算法。研发过程艰辛繁杂,但在 2018 年末,我们成功实现了16 nm 集成电路的探测分析,并于 2019 年 10 月正式发表相关研究成果。

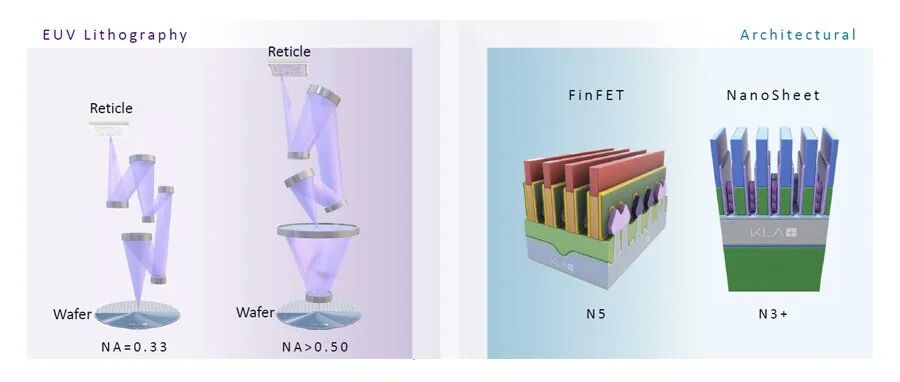

如今顶尖处理器的互连线路间距可窄至 30 nm,而我们的技术至少在理论上能够对小于 2 nm 的结构进行成像。

我们这款全新的X射线检测技术——叠层衍射X射线层析成像技术,能够在不损坏芯片的前提下,解析完整芯片的互连结构,甚至可观测至最微小的元器件结构。

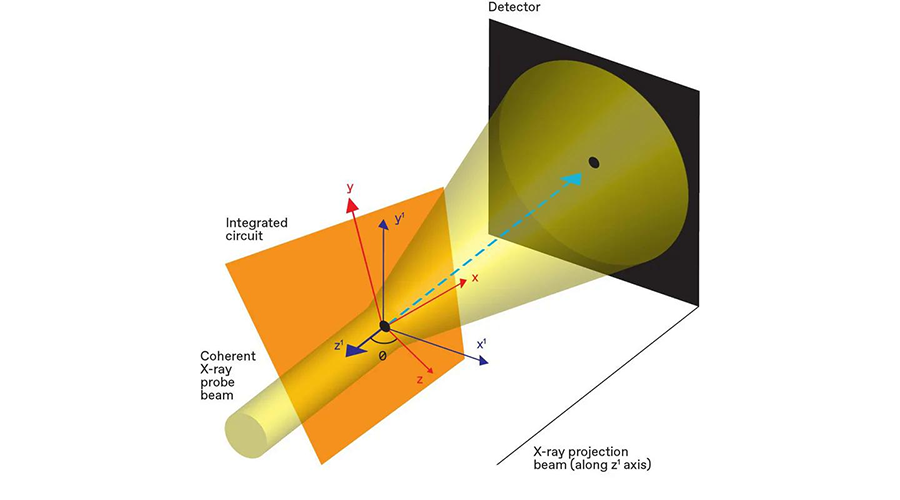

在本次实验中,我们借助 PyXL 实现了对互连线路各层级的虚拟剥离,清晰呈现出线路构成的电路结构。作为初步测试,我们在距离硅基底最近的互连层设计文件中人为植入一处微小缺陷。将该改版层级设计与芯片的PyXL重构模型进行对比后,这一缺陷立刻显现。

借助该技术,我们可以轻松发现芯片设计文件与实际量产芯片之间存在的(人为刻意制造的)差异。南加州大学空间激光研究中心芯片扫描团队

理论层面,即便针对顶尖工艺厂房生产的集成电路,仅需数日时间,便可通过 PyXL 获取其完整性的有效检测数据。当前尖端处理器的互连线路间距仅有数十纳米,而我们的技术至少在原理上,能够解析出尺寸小于 2 nm 的微观结构影像。

但提升分辨率确实会耗费更长时间。尽管我们研发的硬件具备以最高分辨率完整扫描1.2厘米×1.2厘米区域的能力,但若全程采用该模式扫描并不具备实际可行性。针对目标感兴趣区域放大扫描,才是更高效的时间利用方式。在初步实验中,对边长 0.3 毫米的芯片方形区域开展 500 nm 低分辨率扫描,耗时长达 30 小时;而仅扫描宽度40微米的极小芯片区域、采用 19 nm 高分辨率模式时,耗时更是达到 60 小时。

成像速率从根本上受限于瑞士同步辐射光源(SLS)可提供的X射线通量。不过,其他科研机构拥有更高的X射线通量,同时业内也在研发新技术,用以提升X射线光源的亮度——该指标综合涵盖光子产生数量、光束截面积以及光束发散速率三大要素。例如,瑞典隆德的马克斯四世实验室率先实现了将光源亮度提升两个数量级的技术突破。借助新型X射线光学器件,亮度还能再提升一至两个数量级。多项技术优化相结合,未来有望将整体通量提升一万倍。

依托更高的通量,我们有望以短于当前 19 nm 分辨率扫描的耗时,实现 2 nm 的超高分辨率成像。届时,这套系统还能在 30 小时内,以 250 nm 分辨率完成一平方厘米集成电路的全域扫描,该尺寸与苹果M1处理器大致相当。

除此之外,还有多种方式可同步提升成像速度与分辨率,例如进一步稳定探测光束、优化算法,使其适配集成电路的设计规则,同时修正因过量X射线照射引发的器件形变问题。

目前,仅通过观测集成电路的互连线路布局,我们就能获取大量核心信息;而随着技术持续迭代升级,未来将有望实现全维度解析,完整探明芯片的全部细节,包括各类基底材料。以16 nm工艺节点为例,相关材料包含铜、铝、钨以及硅化物复合材料。我们甚至能够精准测量硅晶格的局部应变,这类应变源于高端芯片器件多层堆叠的制造工艺。

当下,铜互连工艺已逐渐逼近技术瓶颈,材料成分检测的重要性愈发凸显。在现代互补金属氧化物半导体电路中,铜互连结构极易发生电迁移现象:电流会导致铜原子错位偏移,进而在电路结构内部形成空洞缺陷。为解决该问题,技术人员会在互连线路外层包覆阻隔层材料。但阻隔层厚度过高,会大幅压缩铜线路的布线空间,造成线路电阻过高。因此,钴、钌等新型替代材料正成为行业研发热点。由于这类新型互连线路尺寸极其微小,我们必须突破 10 nm 以下的分辨率门槛,才能完成精准区分与检测。

各项技术的落地具备充分可行性。将光子X射线层析成像技术与X射线衍射成像技术,应用于硬件电路与生物脑组织的连接组解析,已成为全球科研人员推动新型、升级型X射线光源建设的核心依据之一。与此同时,我们位于加利福尼亚与瑞士的实验室,正持续迭代优化硬件设备与配套软件。在不久的将来,若你对新款中央处理器的品质存疑,或是想要了解竞品芯片的内部构造,便能借助该技术完成芯片内部结构的全景漫游式解析,精准核验每一处结构是否合规完好。

PVD | 长程溅射如何提高侧壁覆盖率?

来,让 Applied Materials 告诉我们,先进制程该怎么做?

Applied Materials,疯狂上新!

WF6 制备 CVD W !

KLA | 深度学习,强化 EUV 工艺检测!

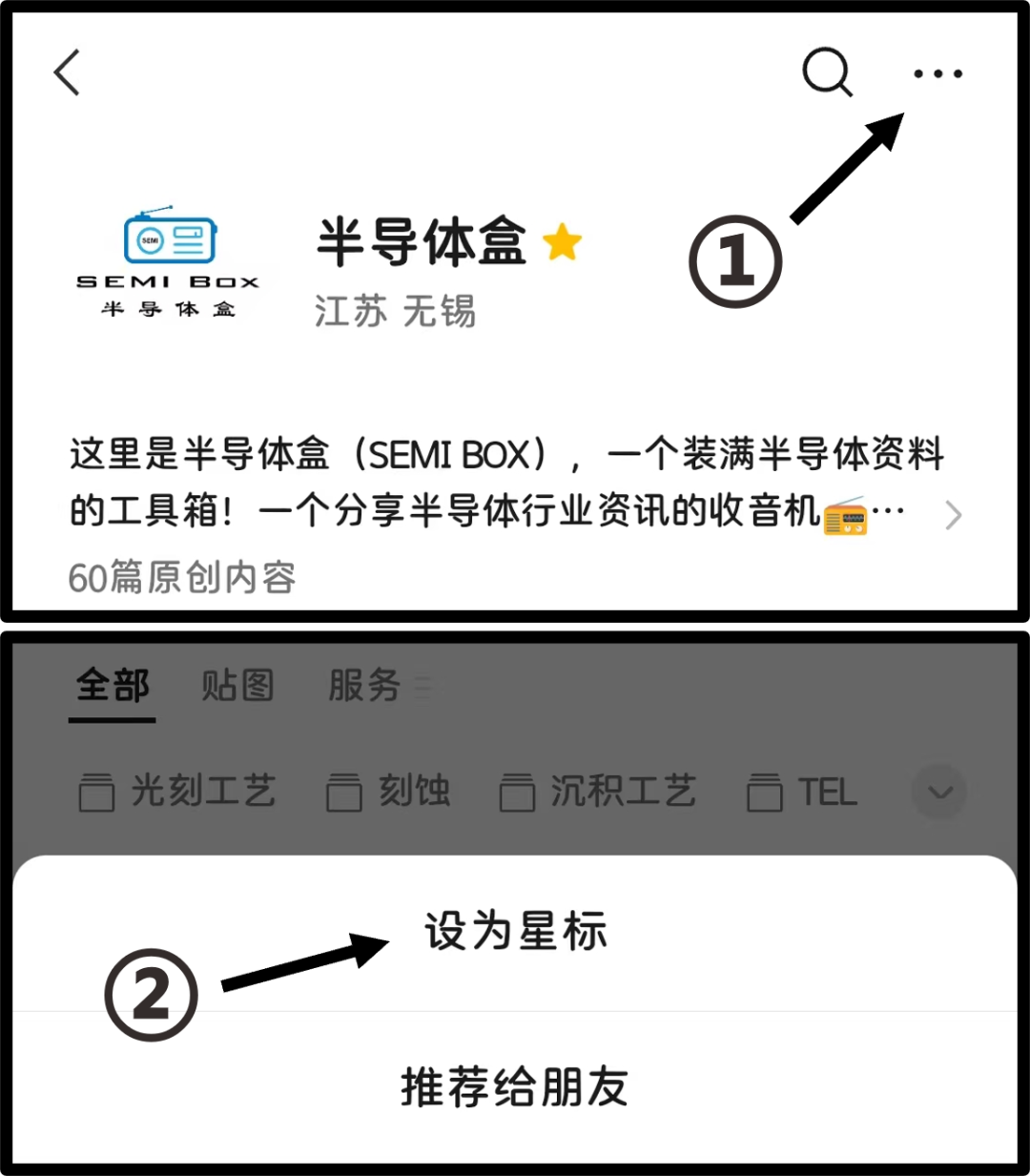

↓设置星标,精彩不错过↓

↓扫一扫,总一款适合你↓

欢迎关注本公众号,获取更多半导体设备、工艺、产业动态