3D 结构下的器件需要怎样的沉积刻蚀工艺?

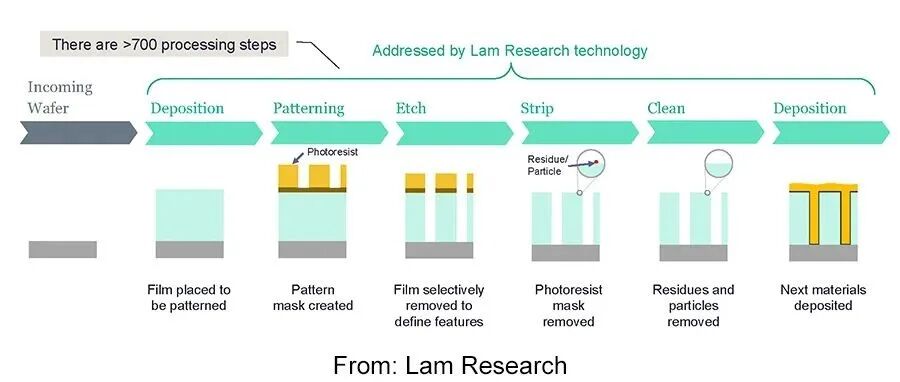

来源:Lam Research,Vahid Vahedi

从 NAND、逻辑芯片、DRAM 到先进封装,一切都在走向 3D 化。3D 时代需要更深的刻蚀与更精准的沉积,才能打造更高、更紧凑的器件结构。

人工智能是半导体行业有史以来最强劲的需求驱动力,其发展速度远超五年前的预期。AI 正以空前规模推动超大规模数据中心的算力需求,同时让智能手机、汽车与工业系统实现端侧实时推理。整个行业正迈入3D 架构主导的半导体新时代。

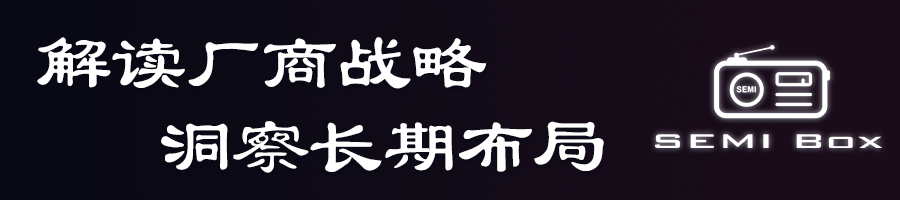

随着器件转向 3D 结构,沉积与刻蚀强度预计将提升约一倍。需求提升的同时,工程师需要构建更高、更复杂、特征尺寸更小的结构。这些挑战正在重塑 3D 时代器件微缩所需的制造要求与技术能力。

什么是 “3D”?

在探讨垂直化带来的挑战前,我们先明确 “3D” 的含义:NAND 与 DRAM 指存储单元的垂直堆叠;逻辑芯片指 3D 晶体管架构。

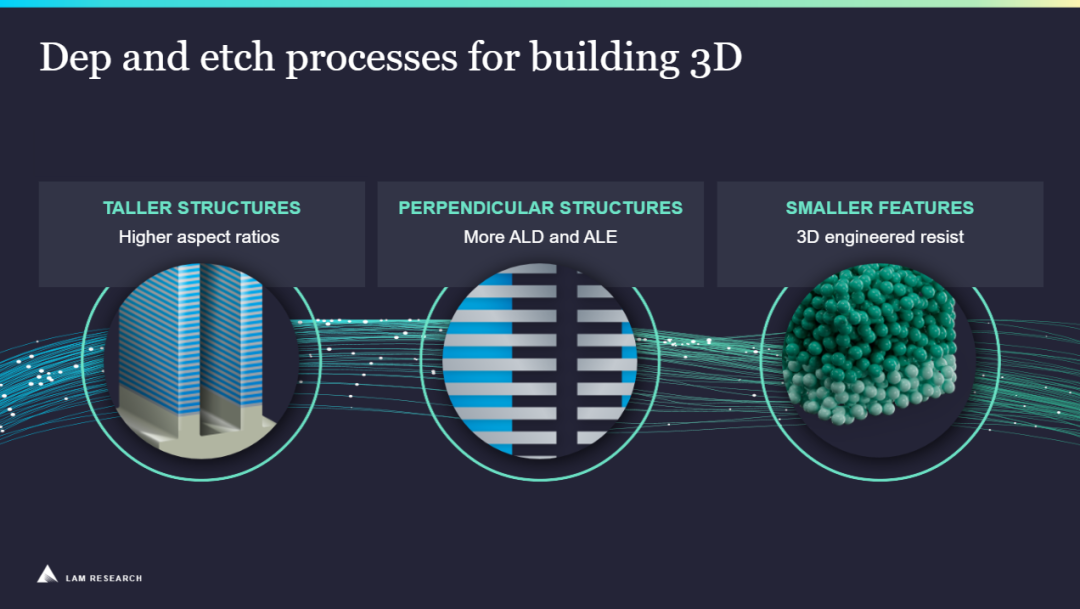

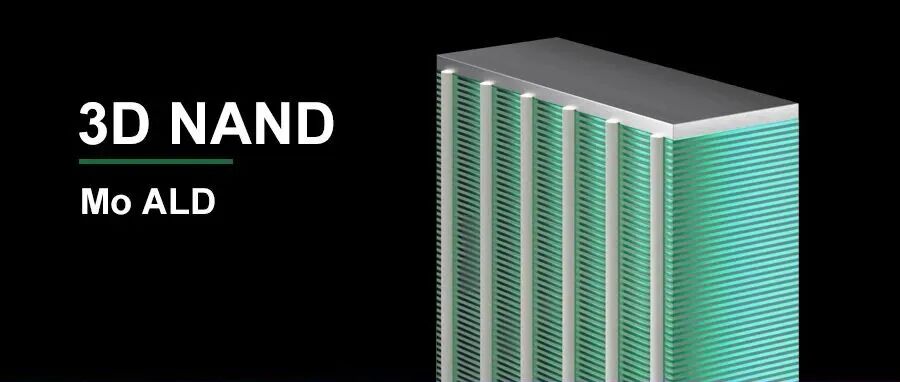

NAND:3D NAND 已量产十余年,仍在持续演进。当前厂商已量产接近300 层的堆叠结构,并已着手开发1000 层架构。

DRAM:长期以来 DRAM 一直是平面结构,如今正从6F² 向 4F²演进,这是迈向全 3D DRAM 的关键一步。该转型需要:

高深宽比(HAR)刻蚀形成沟道

原子层沉积(ALD)进行填充

铜电镀实现 CMOS 晶圆与背面阵列键合

随着字线持续微缩,电阻上升推动钼等新型沉积材料的应用。当 DRAM 走向 3D,存储单元将旋转 90 度垂直堆叠。高带宽内存(HBM)就是 3D 转型的典型案例:通过垂直堆叠多颗 DRAM 裸片并以高密度垂直互联连接,HBM 在紧凑尺寸内实现更高带宽,成为 AI 系统的核心存储技术。

逻辑芯片正进入 3D 转型期,从FinFET演进到环绕栅极(GAA),未来将进一步走向互补场效应管(CFET) 架构。GAA 依赖专用原子层工艺,包括逐层原子层刻蚀(ALE)与原子层沉积(ALD)形成侧墙。随着 3D 器件更高、更小,这些工艺要求持续提升。为缓解布线拥堵、提升性能,供电网络可转移至晶圆背面,进一步增加沉积与刻蚀需求。

先进封装正迎来爆发式增长,需要对堆叠小芯片进行异质集成,并采用创新的横向刻蚀与沉积技术。晶圆键合需要新增背面沉积步骤以平坦化晶圆、保证对准精度;同时需要边缘沉积步骤,避免晶圆边缘厚度差异产生空隙。

3D 转型的三大核心挑战

构建更高深宽比的更高结构

实现垂直 / 横向的垂直加工

定义更小的器件特征尺寸

更高的结构

3D 最直观的表现就是器件 “变高”,而高度提升意味着深宽比大幅增加。

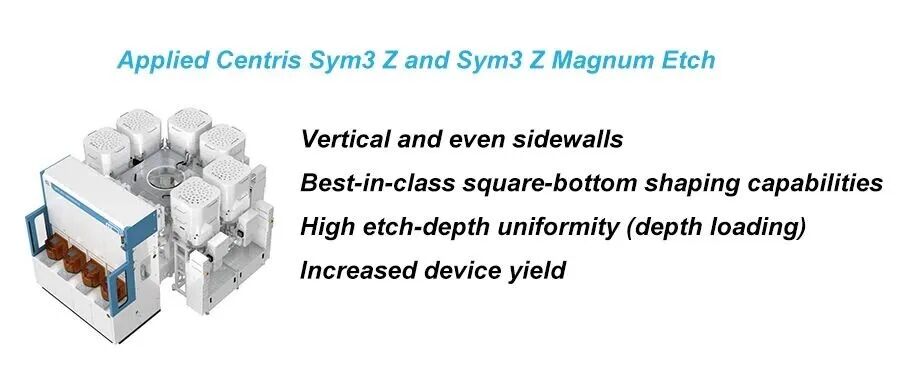

3D NAND 需对极垂直的沟道进行无缺陷刻蚀,当前深宽比约 50:1

未来 NAND 将迈向 100:1,3D DRAM 最终达到 200:1,允许倾斜度低于 0.07 度

转向 3D DRAM 后,垂直精度要求将达到极致:10 微米堆叠的轮廓倾斜必须小于0.1 度。目前尚无满足此类深宽比的大规模量产方案,设备商、材料商与芯片厂需协同开发。

刻蚀越深,速度通常越慢。针对 3D NAND,Lam采用低温刻蚀—— 看似反常,却能加速介质层刻蚀。低温下形成物理吸附层,将反应剂输送至特征结构底部,提升表面覆盖率、加速刻蚀且畸变极小。低温刻蚀速度约为传统工艺的 2.5 倍,传统工艺耗时可达一小时。

基于 ALD/ALE 的垂直加工

3D 架构需要更多刻蚀与沉积:既要向深处加工,还要 90 度横向加工,即垂直刻蚀与沉积。传统 2D 刻蚀中离子无法实现 90 度转向,因此不再适用。逐层均匀、可重复地实现横向加工,需要大幅强化原子层沉积(ALD)与原子层刻蚀(ALE) 能力。

多数 ALD/ALE 技术已量产,但仍需持续创新并保持精度与质量,包括引入新材料与新工艺,这为设备与材料商的深度合作创造了机会。

借助 EUV 实现更小特征尺寸

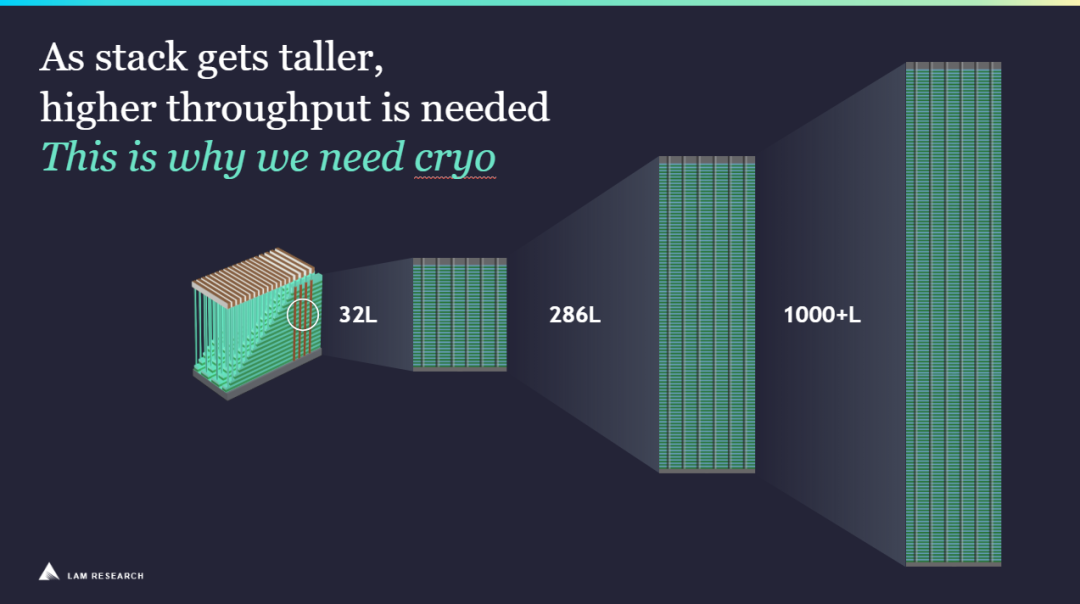

定义 3D 微缩所需的最小特征(如逻辑 GAA 器件),极紫外(EUV)光刻必不可少。金属氧化物光刻胶因其更高的 EUV 敏感度正进入量产,但剂量与尺寸微缩带来新挑战:低剂量易产生针孔缺陷,更薄的光刻胶层易残留杂质。

为应对 3D 微缩挑战,Lam 将光刻胶 3D 化:逐层梯度改性,在关键位置增加吸收剂以拓宽工艺窗口。该方案需要新型前驱体与生态系统支持。Lam 与 ASML 已有十年合作,正与其及材料商共同完善生态;去年 Lam 还与 JSR 签署协议,加速金属氧化物光刻胶落地。

沉积与刻蚀一直是半导体制造的基础,如今在 3D 时代,其作用愈发关键。这些工艺正在塑造支撑人工智能的器件结构 —— 通过全行业紧密协作,将 AI 的愿景转化为硅基现实。

听,Lam Research 在讲未来的刻蚀!

Lam Research | ALTUS® Halo Mo ALD 沉积系统

Applied Materials | 如何设计一台埃米级制程的等离子体刻蚀设备?

TEL | 无等离子体刻蚀在 GAA 器件工艺中的应用

↓设置星标,精彩不错过↓

↓扫一扫,总一款适合你↓

欢迎关注本公众号,获取更多半导体设备、工艺、产业动态