小小铜互连,拿下!

发布时间:2026-05-07来源:半导体盒

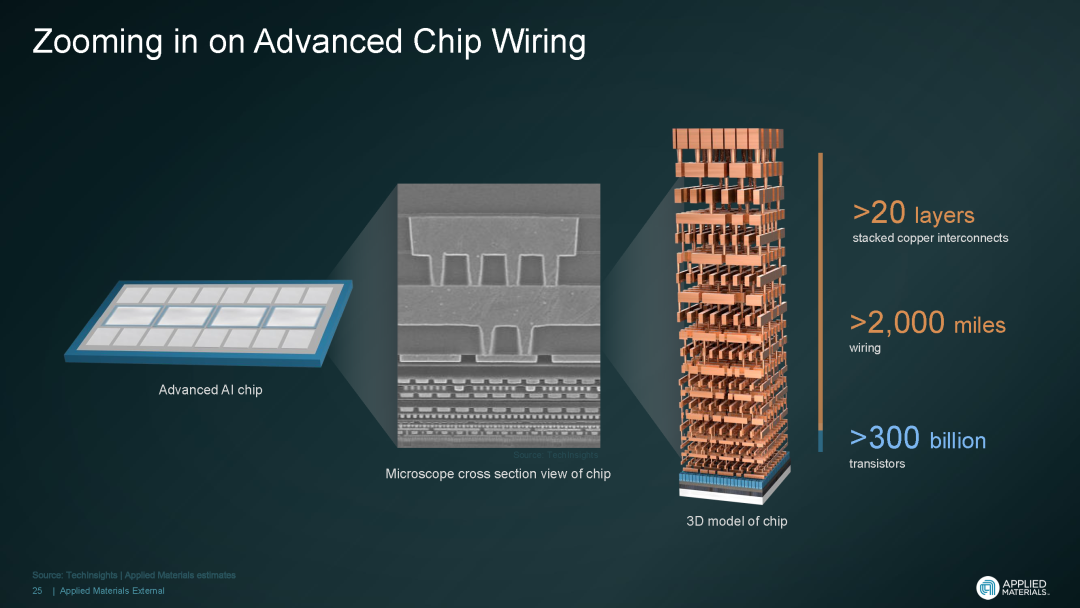

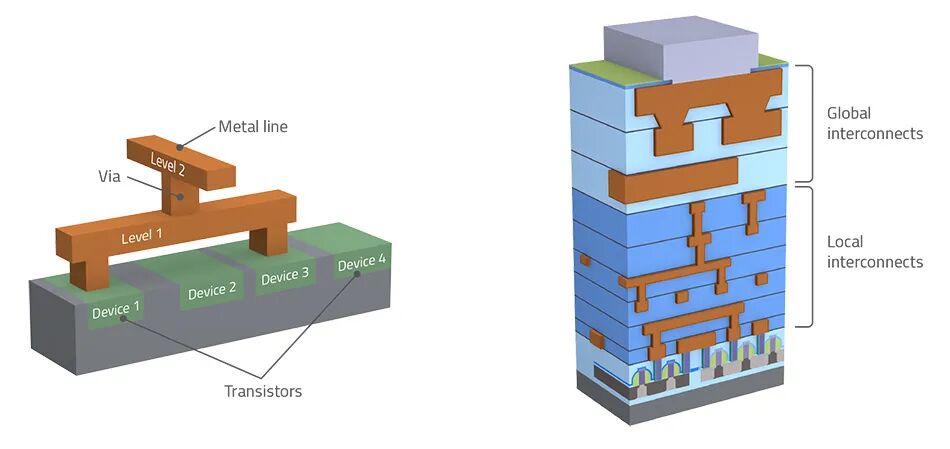

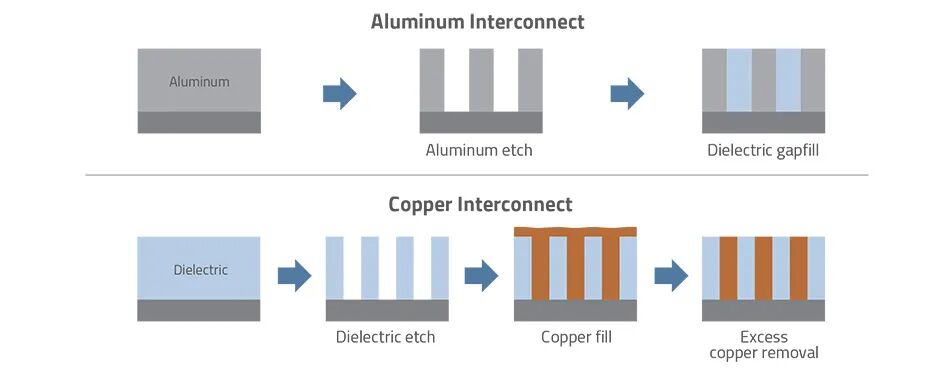

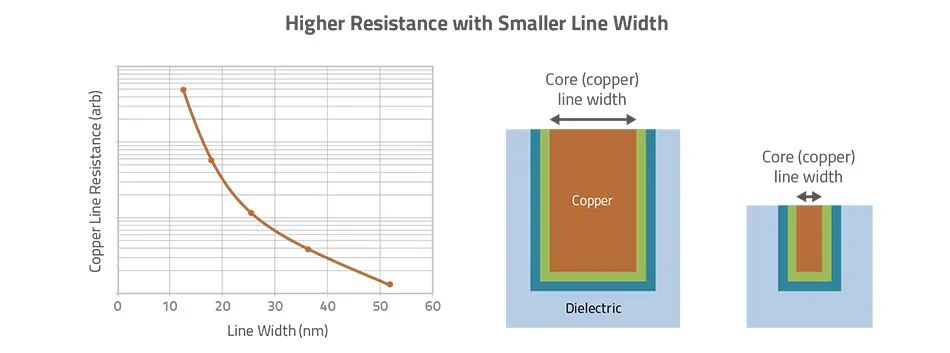

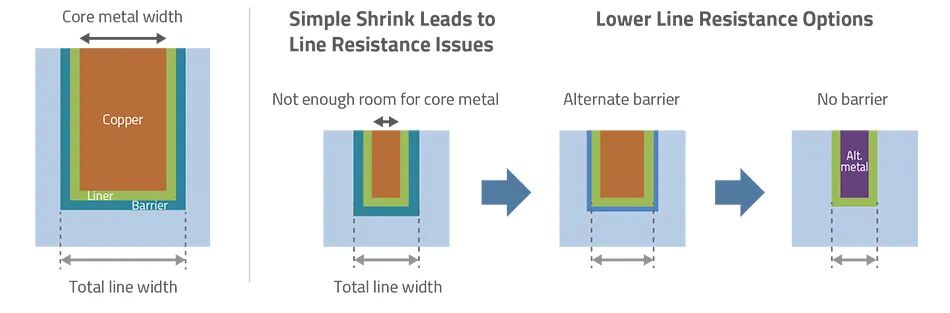

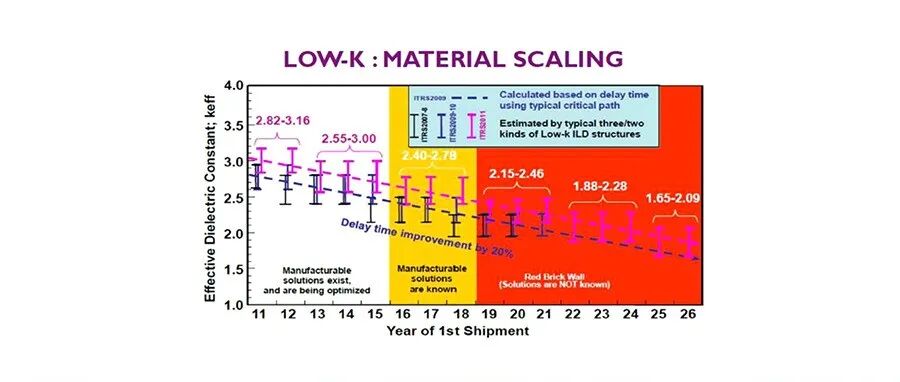

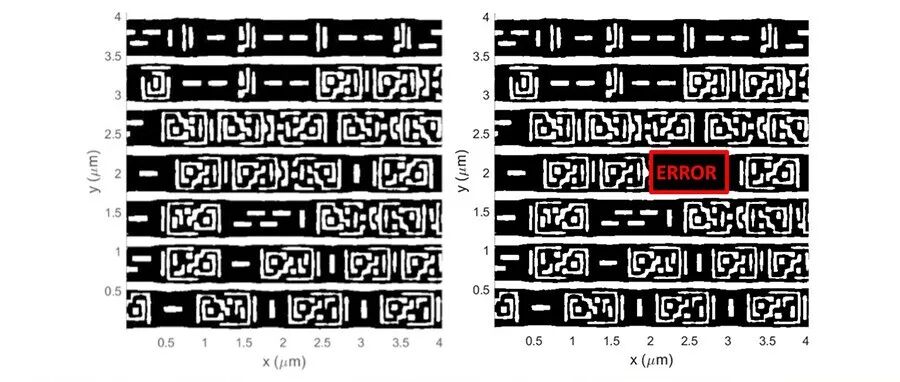

来源:Lam Research-Tech Brief: An Introduction to Interconnects;前段时间,我们在 Applied Materials logic 大师课里了解了最前沿的金属互连,那么金属互连工艺是怎么一步步发展的呢?我们常听闻,先进芯片内部集成数十亿个晶体管 —— 这固然是震撼人心的事实,但你是否了解:一枚指甲盖大小的大规模集成芯片,其多层堆叠结构中,互连 “导线” 总长可达约 30 英里。这类导线如同高速路网与传输管道,负责传导电子、连接晶体管及各类元器件,保障芯片整体正常运作。就好比跑车行驶速度会受高速路拥堵程度影响,芯片的性能强弱,也取决于信号与电力在这些超微型导线中的传输效率。事实上,随着芯片制程尺寸持续微缩,互连结构已然成为当前顶尖先进芯片的运行速度瓶颈。接下来,我们就详细了解一下互连技术。芯片制造的前段制程(front-end-of-line,FEOL)中,晶圆上会完成晶体管、电容等独立元器件的制备。而在后段制程(back-end-of-line,BEOL),需将各类元器件相互连通,实现信号、电源与接地的分配。芯片表面空间有限,无法通过单层布线完成全部连接,因此芯片厂商会搭建多层垂直互连结构。结构简单的集成电路仅有少数几层金属布线,而复杂高端集成电路的布线层数可达十层及以上。紧贴晶体管的互连线路尺寸极小,需适配密集排布的微型元器件,这类底层线路被称作局部互连(Local interconnects),特点是细而短。全局互连(Global interconnects) 位于上层结构,负责芯片不同电路模块之间的信号传输,通常更粗、更长,线路间距也更大。不同互连层之间的连接结构称为通孔(Vias),实现信号与电力的跨层传输。左侧为芯片剖面结构图,移除所有结构后仅保留用于集成电路连接的金属线路:2 层金属线路位于上方,通过垂直通孔与 1 层金属线路相连;1 层金属线路再经由两个通孔,与芯片底层的器件晶体管导通。右侧为完整集成电路结构示意图,全局互连堆叠于局部互连上方。数十年来,铝互连一直是行业通用标准。传统工艺会先沉积铝金属层,再通过光刻刻蚀完成线路图形化,最后沉积绝缘介质隔离导电线路。20 世纪 90 年代末,芯片行业全面改用铜互连。铜的导电性能优于铝,原理类似铜底厨具比全铝厨具导热更快。高导电铜线路大幅提升了集成电路整体性能,同时铜线路可做得更精细,适配晶体管尺寸微缩的发展趋势,且耐用性、稳定性更强。但铜互连的制备工艺复杂度大幅提升,行业为此研发了全新制造体系。铜互连工艺流程:首先沉积二氧化硅等绝缘介质材料,刻蚀形成沟槽;再利用化学电镀工艺向沟槽内填充铜金属;最后去除多余表层铜材,打磨平整,为后续制程提供平整基底。铝互连流程:铝层沉积 → 铝刻蚀 → 介质间隙填充铜互连流程:介质沉积 → 介质刻蚀 → 铜金属填充 → 多余铜材去除 长期以来,晶体管尺寸不断大幅缩小,互连线路也必须同步微缩。如今,传统铜互连工艺在制程迭代中遭遇核心阻碍,也就是 RC 挑战。电阻(Resistance, R):表征电流通过材料横截面的难易程度,由材料原子排列方式与间距决定。电容(Capacitance, C):表征材料储存电荷的能力。芯片运行速度与 RC 值成反比,RC 乘积越低,芯片运行速率越快,因此降低 RC 是打造高速芯片的核心目标。线路电阻越高,载流能力越弱,芯片运行速度随之下降。高电阻会阻碍电子流动,延长晶体管栅极达到开启阈值电压的充电时间。虽然制程微缩持续优化晶体管运行速度,但互连线路的高阻问题,会拖慢晶体管间的电子传输,抵消制程升级带来的性能增益。线路宽度越小,铜互连电阻呈指数级飙升;宽幅铜芯线路电阻更低,窄幅铜芯线路电阻显著升高。左侧配有一张图表,纵轴为铜线电阻(任意单位),横轴为线宽(纳米),取值范围 0 至 60 nm。曲线在约 12 nm 处处于图表高位,随后向右下方急剧下降,在线宽约 52 nm 处降至图表低位。右侧图示展示了绝缘介质中宽铜芯与窄铜芯的结构差异。电容大小取决于金属线路外围的绝缘介质材料,以及线路之间的间距。电容过高会拖慢信号传输速度,还会引发串扰(cross talk) 问题。单条线路的电压信号波动,干扰相邻线路,最终导致芯片故障。除优化线路间距外,低 k 介质材料的研发有效降低了电容。现阶段主流介质材料介电常数 k 值约为 2.5,而纯二氧化硅 k 值高达 4.2。业界虽有多种降 k 技术方案,但介电常数越低,超低 k 介质薄膜脆性越强,大幅增加量产制造难度。为突破制程限制、解决 RC 难题,行业聚焦金属材料与薄膜结构优化,持续探索技术路线,延长铜互连的使用寿命。标准铜互连线路为多层复合结构:氮化钽阻挡层(防止金属扩散至介质)+ 钽阻挡衬垫层(liner,增强薄膜结合力)+ 铜籽晶层(引导电镀填铜)+ 核心导电铜层。当前研发的重点是探索优化阻挡层、衬垫层与籽晶层结构,降低整体电阻,压缩薄膜厚度,为核心铜导线预留更多空间,适配微缩制程。- 减薄高阻阻挡层与衬垫层,但薄膜减薄存在物理极限,为保障绝缘与稳定性,单层薄膜最小厚度需维持 1.5–2 nm,沟槽两侧复合薄膜总厚度可达 3–4 nm,进一步缩减空间有限。

- 自成型阻挡层:可与铜线路周边介质自发反应成型,省去传统厚阻挡层,扩充铜线路有效截面积;

- 替代金属衬垫:钴、钌等新型材料逐步替代钽材质,与铜籽晶层结合性更佳,可实现超薄共形镀膜,杜绝线路空洞缺陷;目前,无空洞超细沟槽填铜技术已实现量产应用。

Lam Research | ALTUS® Halo Mo ALD 沉积系统

然而,在 5 nm 制程节点附近,传统铜材料将难以适配极致微缩的布线需求。未来超微缩线路,需要淘汰铜材料,采用无阻挡层新型导电金属作为替代。除金属材料升级外,介质材料革新同样是研发重点。行业终极目标是无限压低介电常数,理想极限为 k=1(空气介质)。气隙(air gaps) 技术已完成技术验证,但制备工艺复杂、生产成本高昂,难以大规模量产落地。综上,互连技术的迭代升级,将围绕新型金属材料、电路架构创新、制造工艺革新三大方向推进,持续支撑芯片向更小制程、更高运算速度发展。

↓设置星标,精彩不错过↓

本文仅作行业信息分享、技术交流,不涉及任何涉密内容欢迎关注本公众号,获取更多半导体设备、工艺、产业动态

转载说明:本文系转载内容,版权归原作者及原出处所有。转载目的在于传递更多行业信息,文章观点仅代表原作者本人,与本平台立场无关。若涉及作品版权问题,请原作者或相关权利人及时与本平台联系,我们将在第一时间核实后移除相关内容。