保真度突破99.86%!硅基自旋量子比特迎来“始终在线”并行操控新时代

在量子计算迈向实用化的征程中,硅基自旋量子比特凭借与现代半导体工艺完美兼容、器件尺寸微小、可在1开尔文以上温度工作等独特优势,成为规模化量子芯片最具潜力的技术路线之一。而在这一赛道上,仅依靠交换相互作用实现全域量子操控的交换型自旋量子比特,更是凭借无需复杂磁场调控、纯电控操作的特性,备受学术界与产业界关注。

4月3日,美国HRL实验室与加利福尼亚大学洛杉矶分校联合团队在《Nature Communications》期刊上发表题为"Demonstration of an always-on exchange-only spin qubit"(全时开启、仅交换相互作用自旋量子比特的实验演示)的研究论文。Joseph D. Broz为本论文第一作者兼通讯作者,Jason R. Petta 为共同通讯作者。

本研究在硅/硅锗异质结的三角形量子点阵列上,首次成功实现始终在线交换型(AEON)自旋量子比特的高精度量子操控,通过盲随机化基准测试测得单量子比特克利福德门平均保真度高达99.86%,泄漏错误率仅0.015%,一举突破传统交换型量子比特的操控效率与保真度瓶颈,为高速、低噪、可扩展的硅基量子计算芯片提供了全新架构方案。

研究背景:传统交换型量子比特的瓶颈与破局方向

要理解这项突破的重要性,我们需要先回到硅基自旋量子比特的核心逻辑。

量子点是通过电场在半导体中制造的纳米尺度“陷阱”,可以精准捕获单个电子,电子的自旋向上与向下状态分别对应量子比特的|0⟩与|1⟩,这便是自旋量子比特的基本原理。但早期单自旋量子比特面临一个棘手难题:精准操控单个电子自旋,要么需要设计复杂的局域磁场,要么依赖强自旋轨道耦合材料,大幅增加了器件设计与制备难度,成为规模化扩展的阻碍。

为解决这一问题,科学家提出了交换型(EO)自旋量子比特:将一个量子比特信息编码在三个电子的集体自旋态中,完全依靠电子间的交换相互作用实现量子门操控,彻底摆脱对磁场调控的依赖,仅通过电压即可完成所有操作,与传统CMOS芯片的电控逻辑高度契合。

在过去近二十年的研究中,传统交换型量子比特采用串行脉冲操控模式:任意时刻只激活一对电子间的交换耦合,通过依次切换不同交换作用,组合出所需的量子门操作。这种方式简单易校准,但代价极为明显—— 量子门深度过大,单量子比特门最多需要4个交换脉冲,双量子比特纠缠门甚至需要28个脉冲。更长的脉冲序列意味着量子比特暴露在环境噪声中的时间更久,电荷噪声、核自旋噪声等干扰会显著降低操控保真度,同时也限制了量子计算的运行速度。

此外,串行操控还存在泄漏误差问题:量子信息容易从编码的量子比特子空间逃逸到高能级非计算子空间,导致信息丢失,这也是制约交换型量子比特走向容错量子计算的关键障碍。

面对这些瓶颈,理论物理学家早在2016年就提出了始终在线交换型(AEON)量子比特的构想:放弃串行操控,改为同时激活两组交换耦合,用并行交换脉冲构建量子门。理论预测,这种全新架构可将单量子比特门脉冲数压缩至2个以内,双量子比特门仅需1个脉冲,同时通过诱导能量隙天然抑制泄漏误差,还能在双最优点工作点实现对电荷噪声的一阶不敏感,堪称交换型量子比特的“进化版”。

但理论构想落地面临巨大实验挑战:同时调控两组非对易交换作用,需要精准控制电压波形的时序与幅度,校准难度呈指数级上升;如何在三角形量子点阵列中实现稳定的双交换并行操控,如何抑制并行脉冲带来的相干误差,都是亟待攻克的实验难题。而此次发表的研究,正是全球首次完成AEON量子比特的全维度实验验证,填补了从理论到实践的关键空白。

理论核心:AEON量子比特的并行操控与抗噪原理

AEON量子比特与传统交换型量子比特,本质上共享相同的三电子集体自旋编码方式,核心区别在于操控模式。

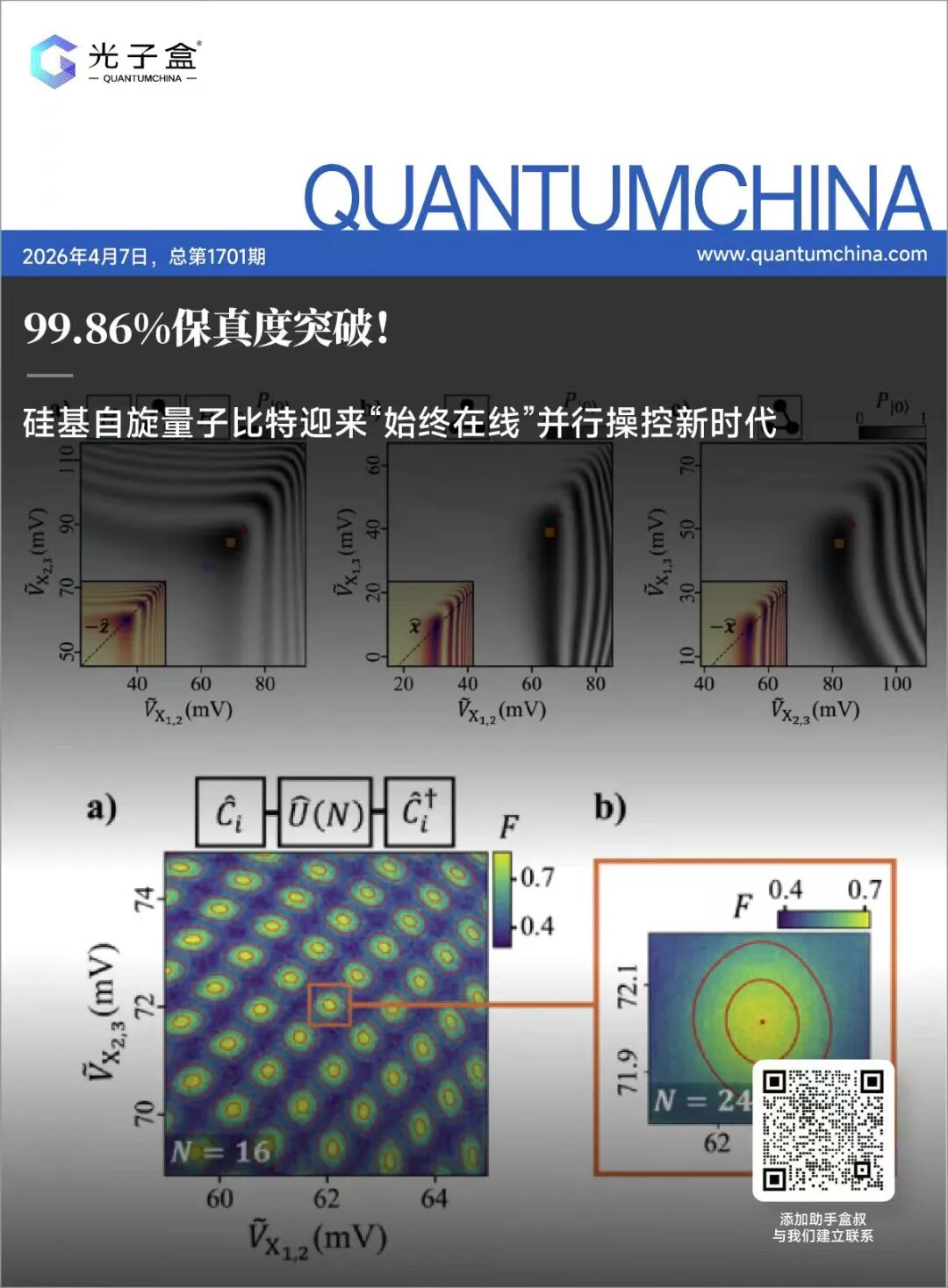

传统交换型量子比特采用“1J操控”:任意时刻只有一组交换作用生效,量子态绕固定轴旋转;而AEON 量子比特采用“2J操控”:同时激活两组交换耦合,量子态可在布洛赫球面的xz平面内绕任意轴旋转,仅需12个并行脉冲即可实现任意单量子比特门,量子门深度大幅降低,从根源上减少噪声积累时间。

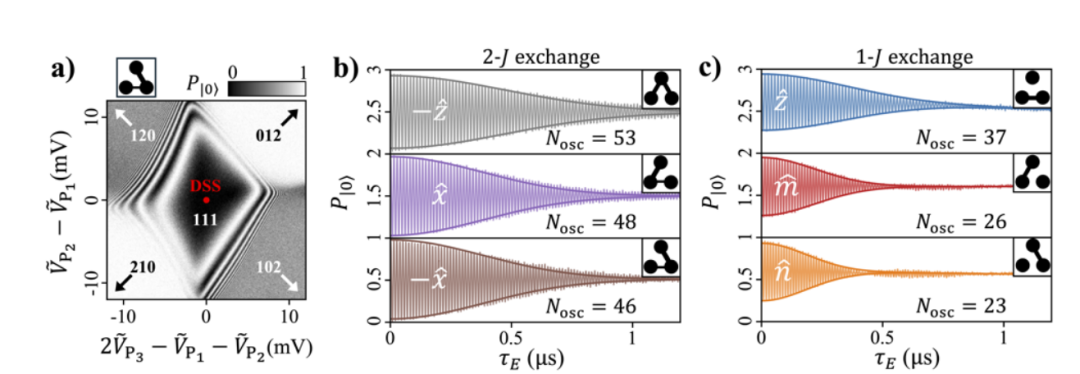

图:AEON量子比特的相干控制。

抗噪性能是AEON量子比特的另一大核心优势。研究团队选择在双最优点(DSS) 工作,这一特殊偏置点下,交换作用对三个量子点化学势的涨落呈现一阶不敏感,直接削弱了电荷噪声对量子相干性的破坏。同时,并行交换作用会在量子比特子空间与泄漏子空间之间形成显著能量隙,让量子信息难以逃逸,天然实现泄漏保护,无需额外的动态解耦脉冲,进一步简化操控序列。

简单来说,AEON量子比特通过“并行操控+双最优点+能量隙抑制泄漏” 三重机制,同时解决了传统交换型量子比特的三大痛点:门深度大、电荷噪声敏感、泄漏误差高,为高保真、高速率量子操控奠定了理论基础。

实验方案:三角形量子点芯片与精准校准体系

为实现AEON量子比特的稳定操控,研究团队搭建了一套精密的实验体系,从器件制备、操控设计到校准测试,每一步都突破了传统方案的局限。

(一)器件设计:三角形三量子点芯片

实验核心器件是基于同位素纯化硅28/硅锗异质

结的三角形三量子点器件,采用刻蚀栅电极工艺制备。同位素纯化可大幅降低硅29核自旋带来的噪声,是提升自旋量子比特相干时间的关键技术。器件上集成了多组电极:柱塞栅用于调控量子点化学势,确保每个量子点精准捕获单个电子;交换栅用于控制相邻量子点间的隧穿耦合,即交换作用强度;此外还有电子注入电极与电荷传感电极,用于量子态初始化与读取。

团队创新性采用虚拟栅技术,通过补偿矩阵消除物理电极间的串扰,实现对量子点化学势与交换耦合的独立精准调控,避免了不同栅电压间的相互干扰,这是稳定实现双交换并行操控的前提。

(二)量子态操控:并行交换脉冲实现全域控制

量子态初始化采用泡利自旋阻塞技术,将量子比特制备到|0⟩基态;读取环节通过电荷传感器将量子自旋态转化为可测量的电荷信号,实现高保真度状态读出。

核心操控环节,团队摒弃传统串行脉冲,施加两组同时生效的交换脉冲,通过调控脉冲幅度与duration,实现量子态绕任意轴的旋转。实验验证,即便未实现极致的时序精准控制,并行交换操控仍能精准描述量子态演化,证明了AEON架构的实验鲁棒性。

(三)创新校准:双参数同步优化方案

并行操控的最大难点是同时校准旋转轴与旋转角两个参数。传统校准方法仅适用于单参数调控,无法满足需求。为此,团队设计了一套复合脉冲序列校准方法:构建对旋转轴与旋转角误差同时敏感的复合序列,通过序列放大误差信号,再结合二维电压扫描与峰值追踪,实现双参数同步优化。

这套方法具备海森堡标度特性,校准精度随序列长度提升,单量子比特门校准时间仅需约5分钟,兼顾了精度与效率,为多量子比特系统的规模化校准提供了可行方案。

(四)性能评估:盲随机化基准测试

为客观评估量子门保真度,团队采用盲随机化基准测试(BRB),这是量子计算领域公认的无偏性能评估方法,可排除态制备、测量误差的干扰,精准提取量子门本征保真度。通过完整克利福德门集的随机化测试,得到平均门保真度与泄漏误差率,确保结果真实可靠。

实验结果:99.86%超高保真与泄漏误差减半

经过系统实验测试,AEON量子比特交出了一份惊艳的答卷,多项指标超越传统交换型量子比特。

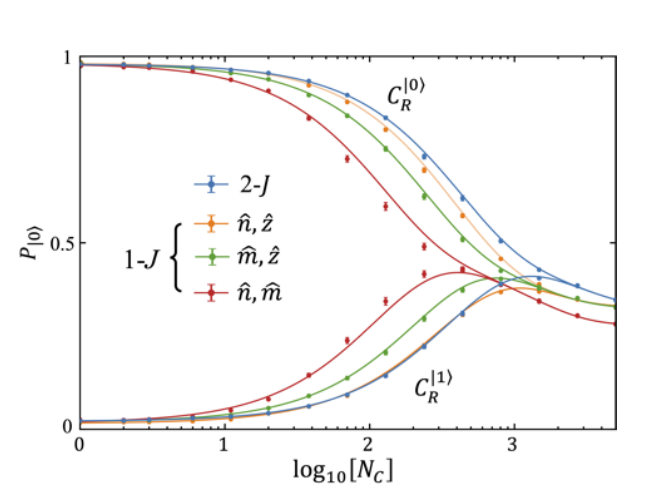

(一)量子门保真度突破 99.86%

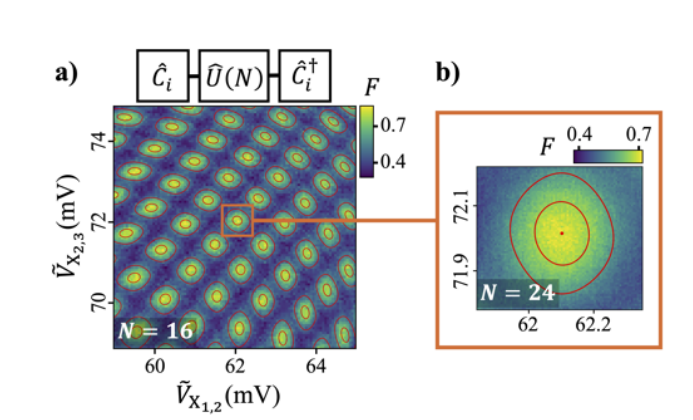

图:盲随机基准测试

盲随机化基准测试结果显示,AEON量子比特的单量子比特克利福德门平均保真度达到99.86%,小幅超越同器件上传统串行操控的最佳结果99.84%,达到国际硅基自旋量子比特的顶尖水平。这一保真度已接近容错量子计算对单量子比特门的基本要求,证明AEON架构具备实用化潜力。

(二)泄漏误差率降低50%

并行交换带来的能量隙效应显著抑制泄漏误差,AEON量子比特的单克利福德门泄漏误差仅0.015%,约为传统串行操控0.029%的一半,泄漏保护效果得到直接实验验证,大幅提升了量子信息的稳定性。

(三)相干振荡性能更优

量子相干振荡实验显示,在双最优点工作的并行交换操控,其相干振荡衰减前的周期数显著多于传统串行操控,证明并行模式对电荷噪声的敏感度更低,相干保持能力更强,为更长时间的量子计算提供了支撑。

(四) 门深度大幅压缩

AEON量子比特的单量子比特克利福德门平均仅需1.9个交换脉冲,而传统方案需要2.7个,脉冲数量减少约30%。更短的门深度意味着更快的操控速度、更少的噪声积累,为实现高速量子计算奠定基础。

研究团队也分析了当前误差的主要来源:并行交换的非对易性导致的瞬态响应差异、脉冲校准imperfect等相干误差,是限制保真度进一步提升的关键。未来通过最优控制脉冲整形技术,可有效抑制此类误差,将保真度推向99.9%以上的容错阈值。

开启硅基量子计算新范式

这项首次实现AEON量子比特全维度操控的研究,不仅是交换型自旋量子比特的里程碑突破,更为硅基规模化量子计算开辟了全新技术路径,其核心价值体现在三个层面:

(一)架构革新:重构交换型量子比特操控逻辑

AEON架构彻底改变了交换型量子比特的串行操控范式,用并行交换实现“高速、低噪、低泄漏”三重优势,解决了长期制约该领域的核心瓶颈,证明了交换型量子比特可通过操控模式创新实现性能跃升,为后续器件设计提供了全新思路。

(二)技术兼容:延续硅基芯片工业化优势

实验基于同位素纯化硅/硅锗异质结与标准半导体工艺制备,保留了硅基量子比特与CMOS工艺兼容、可大规模量产、器件尺寸小的核心优势,无需颠覆性工艺革新即可实现技术迭代,具备极强的产业化落地潜力。

(三)扩展潜力:支撑高效双比特门与多量子比特系统

理论预测,AEON架构可将双量子比特纠缠门的脉冲数从28个压缩至1个,操控效率提升一个数量级。下一步,研究团队将实现两个AEON量子比特的高精度纠缠,构建双量子比特逻辑门;同时探索三交换并行操控,实现泄漏保护的恒等门,进一步提升idle状态下的量子信息稳定性。

更具前景的是,并行交换机制可直接用于实现原生i-Toffoli门,这是容错量子计算与多量子比特逻辑运算的关键元件,无需复杂脉冲合成即可实现三量子比特操控,大幅简化量子计算电路,为通用量子处理器设计提供全新方案。

结语

从单自旋量子比特到交换型量子比特,再到如今的始终在线交换型量子比特,硅基自旋量子计算正沿着“简化操控、提升保真、兼容工艺” 的路径稳步前行。99.86%的超高保真度、减半的泄漏误差、大幅压缩的门深度,AEON量子比特用实验数据证明了并行交换架构的巨大优势。

随着脉冲整形、多量子比特耦合、规模化校准等技术的持续突破,基于AEON架构的硅基量子芯片,有望在未来35年实现从单量子比特到多量子比特处理器的跨越,成为容错量子计算的核心载体。这场始于硅材料的量子革命,正从实验室走向工业化,一步步兑现量子计算的无限可能。

https://www.nature.com/articles/s41467-026-70943