Nature系列重磅!超导量子纠错锁死核心瓶颈,容错逻辑门迎来关键跃迁!

量子计算凭借并行处理与指数级存储能力,被视为下一代计算革命的核心载体。但量子态极度脆弱,环境噪声、操控误差、退相干等问题,让物理量子比特的错误率始终居高不下,直接制约了实用化量子计算机的落地。量子纠错技术通过将多个物理量子比特编码为逻辑量子比特,实现错误的检测与修正,是通往大规模容错量子计算的必经之路。

4月10日,悉尼大学、伦敦大学学院、IBM Quantum联合团队在《Nature Communications》期刊上发表题为"Characterising the failure mechanisms of error-corrected quantum logic gates"(纠错量子逻辑门失效机制的表征)的研究论文。Robin Harper为论文第一作者,Stephen D. Bartlett为论文通讯作者。

该研究基于IBM Heron系列156比特超导量子处理器,以重六角码为实验载体,首次系统刻画了纠错量子逻辑门的失效机制,精准定位测量噪声为当前逻辑门性能的核心瓶颈,并通过电路革新大幅提升逻辑量子比特的存储与运算保真度,为容错量子计算硬件优化与协议设计提供了关键实验依据。

研究背景:容错量子计算的核心矛盾与现实困境

构建实用化量子计算机,必须同时解决两大核心问题:一是量子信息的稳定存储,即逻辑量子比特在纠错循环中保持状态不被破坏;二是高保真逻辑门操作,即在纠错保护下完成可靠的量子运算。这两大功能高度依赖量子纠错过程中的环中测量,这类测量不仅能提取错误征兆数据,还能驱动格点手术等容错逻辑门的执行,是容错架构的核心组件。

但环中测量本身会引入新的噪声:测量过程中的量子比特弛豫、测量赋值错误、测量后复位操作的误差,都会累积形成逻辑错误。更关键的是,容错设计中常通过重复测量提升可靠性,但重复测量会延长量子信息存储时间,加剧退相干误差,形成“测量可靠性”与“存储时长”的核心trade-off。

此前,量子纠错研究多聚焦逻辑量子比特的存储性能,对逻辑门操作的失效机制缺乏系统实验刻画,难以定位硬件噪声的关键瓶颈。而这项研究首次在同一超导平台上,同时完成逻辑存储与逻辑门稳定性的benchmark,完整揭示了容错逻辑运算的失效根源,填补了领域空白。

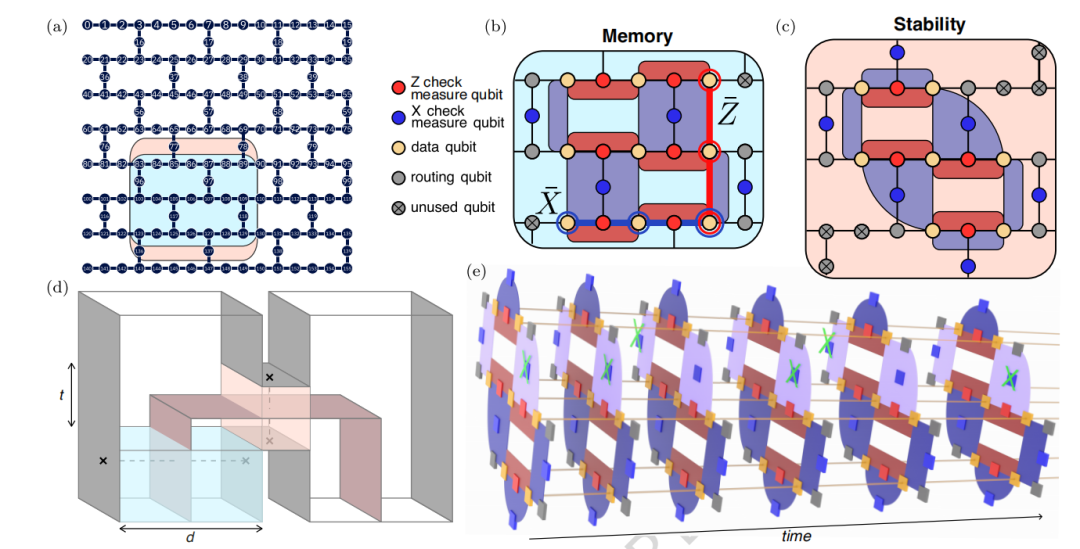

理论基础:重六角码与容错逻辑门的实验框架

研究团队选择重六角码作为核心纠错码,这是一种适配IBM超导量子处理器重六边形布局的子系统码,具备硬件友好、可扩展性强的优势。团队在IBM Heron系列Marrakesh处理器上部署码距d=3的重六角码,该处理器支持环中测量与保真度超99%的双比特门,为高精度容错实验提供了硬件支撑。

研究设计两大核心实验,分别对应容错计算的两大核心能力:

存储实验:量化逻辑量子比特在多轮征兆提取中的错误率,评估量子存储器的稳定性;

稳定性实验:模拟格点手术逻辑门的执行过程,测试逻辑门在重复测量下的失效概率,作为容错逻辑门性能的直接代理指标。

为解析噪声影响,团队构建了完整的电路级噪声模型,涵盖单/双比特去极化噪声、测量与复位错误、量子比特空闲弛豫噪声等所有关键噪声源,通过数值模拟与实验数据对照,精准定位每种噪声对逻辑性能的影响权重。

实验方案:两大创新突破,重构征兆提取电路

实验分为三大核心模块:首先是传统方案与改进方案的对比测试,分别运行原征兆提取电路与新型并行电路,量化电路优化对逻辑保真度的提升幅度;其次是双范式对照实验,同步开展记忆实验与稳定实验,分别测试不同测量轮次下的逻辑错误率,揭示权衡规律;最后是噪声参数扫描实验,通过仿真调控单类噪声强度,定位影响逻辑性能的核心因素。

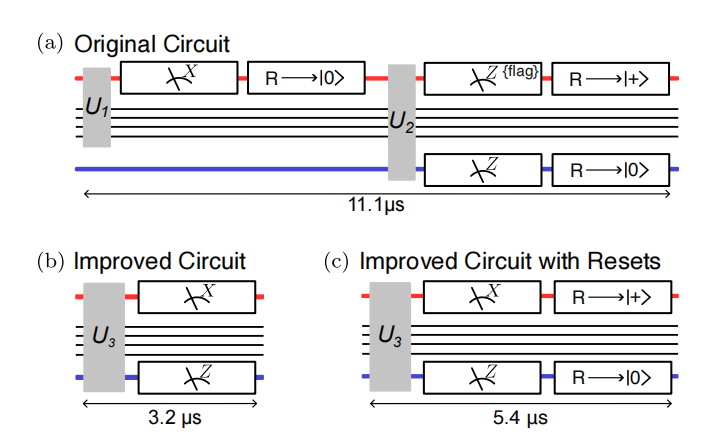

现有重六角码实现方案存在明显缺陷:X型与Z型校验分两轮测量,且每轮测量后需复位辅助比特,导致电路深度大、运行时间长,空闲误差急剧累积。针对这一问题,团队提出两项颠覆性电路革新:

并行征兆提取,大幅压缩电路深度

传统方案需分两步完成X、Z校验测量,总耗时达11.1微秒。新方案通过借鉴表面码读出思路,利用次近邻CNOT门,实现X、Z型校验同步测量,无需标记比特即可规避钩状错误,将单轮征兆提取时间压缩至3.2微秒,速度提升近3倍,显著减少数据量子比特的空闲弛豫误差。

取消测量后复位,用经典泡利框架更新替代硬件复位

测量后复位是传统纠错电路的标配,但复位操作本身会引入噪声且耗时。团队采用经典泡利框架更新技术,在软件层面跟踪量子比特状态,完全取消硬件复位步骤,进一步缩短电路时长,同时避免复位误差。这种修改仅需调整解码器的检测结构,将连续测量对比改为间隔一轮对比,不损失解码性能。

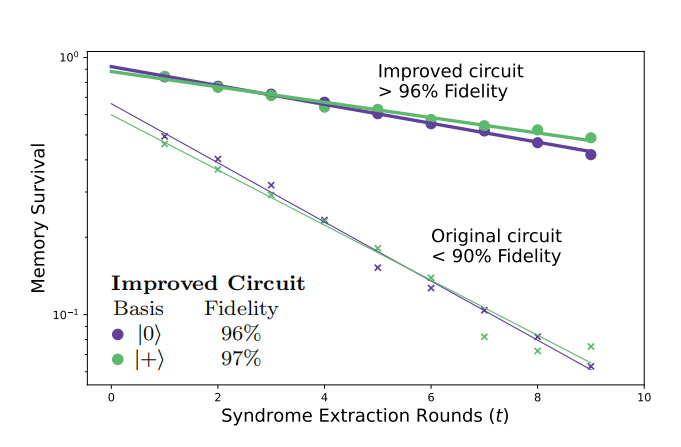

这两项创新结合,让重六角码的单轮征兆提取保真度从不足90%提升至96%以上,逻辑量子比特的生存概率实现质的飞跃,为后续逻辑门实验奠定基础。

实验结果:存储与逻辑门性能双提升,锁定核心噪声瓶颈

(一)存储实验:逻辑存储错误率显著降低

团队对比传统电路与优化电路的存储性能,结果显示:优化后的并行征兆提取+无复位方案,让逻辑量子比特在| 0⟩与|+⟩初始态下的单轮生存概率均突破96%,远优于传统方案的不足90%。建模分析证实,测量期间的量子比特弛豫是逻辑保真度损失的主要来源,而新电路通过缩短测量时间,从根源上抑制了这类误差。

(二)稳定性实验:逻辑门失效机制清晰呈现

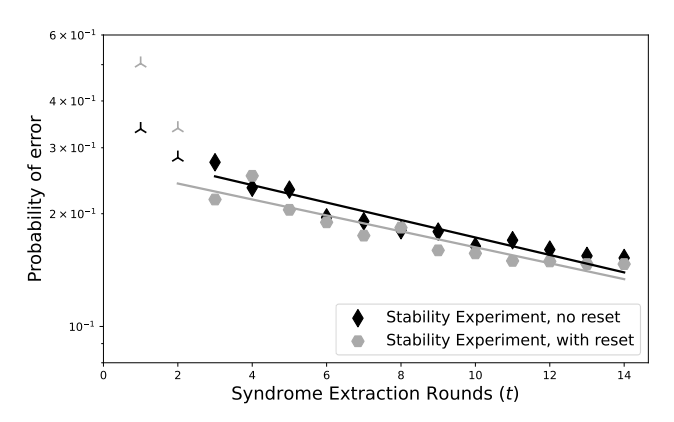

稳定性实验直接模拟格点手术逻辑门的执行,逻辑门失效源于连续多轮未被检测的测量错误。实验发现,随着测量轮数增加,逻辑门失效概率呈指数下降,证明系统工作在纠错阈值以下,符合容错设计预期。

团队对比带复位与无复位两种电路,发现两者性能差异极小。原因在于Marrakesh处理器采用测量+条件X门的复位方式,复位误差与测量误差相当,增加复位虽提升时间码距,但也引入额外噪声,两者效果相互抵消。这一结论为后续纠错电路设计提供重要指导:现有复位技术无法提升性能,优先取消复位以缩短时长。

(三)噪声仿真:测量噪声主导逻辑门性能

团队通过Stim仿真系统,独立调控单比特错误、双比特错误、测量噪声、空闲噪声、复位噪声等参数,量化其对存储与稳定性实验的影响。结果明确:

降低测量噪声对逻辑门稳定性的提升效果最显著,同时也能改善存储性能;空闲噪声与双比特噪声对两者均有影响,但效果弱于测量噪声;复位噪声仅对带复位电路有轻微影响,对存储性能几乎无作用。

仿真与实验一致证实,当前容错逻辑门的性能瓶颈,是环中测量噪声,而非门操作误差或退相干噪声。

研究核心成果与科学意义

这项发表于《Nature Communications》的研究,实现了容错量子计算领域的多项关键突破,核心成果可概括为四点:

首次系统刻画纠错逻辑门失效机制在同一超导平台上同步完成存储与稳定性实验,完整揭示了测量噪声、空闲误差、复位操作对容错逻辑运算的影响路径,明确逻辑门失效主导逻辑存储失效,为领域提供了完整的实验认知框架。

重六角码电路革新,性能大幅跃升提出并行征兆提取+无复位的优化电路,将单轮逻辑保真度从不足 90%提升至96%以上,证实缩短环中测量时长是抑制逻辑错误的关键手段,为硬件高效纠错提供可复用方案。

澄清复位操作的实用价值实验证明当前硬件复位技术无性能增益,反而增加电路耗时,建议后续容错电路优先取消复位,采用经典泡利框架更新,简化硬件设计、降低噪声累积。

精准定位硬件优化核心方向通过仿真与实验锁定测量噪声为当前核心瓶颈,指出未来提升容错逻辑性能的关键:降低环中测量错误率、缩短测量耗时、优化测量器件精度,为量子处理器迭代指明路径。

迈向大规模容错量子计算

当前,量子计算正从NISQ时代迈向容错时代,单纯增加比特数量已无法满足需求,提升逻辑保真度成为核心命题。这项研究不仅是重六角码的性能突破,更搭建了一套容错逻辑门性能benchmark与噪声解析的标准化流程,可直接推广至表面码、颜色码等主流纠错码,适用于超导、离子阱等多种量子平台。这项研究以清晰的实验证据告诉我们:纠错逻辑门的性能瓶颈不在门控本身,而在测量环节;量子记忆的损耗不在编码,而在空闲等待。这一认知将重构容错量子硬件的研发路径。

未来,基于该成果的优化方向清晰可见:一是研发更快、更准的中途测量技术,将测量时间压缩至比特相干时间的极小比例,从根源抑制空闲错误;二是将并行征兆提取、无复位测量等方案推广至更大码距、更多拓扑码,支撑更高深度的容错逻辑;三是结合新型解码算法与噪声自适应校准,进一步挖掘逻辑性能潜力。

从量子纠错的基础理论,到硬件电路的工程优化,再到失效机制的系统解析,这项研究完整展现了“理论—实验—优化”的全链条创新。随着测量技术、纠错协议、硬件工艺的持续进步,大规模容错量子计算机的落地,正从科学构想逐步走向现实。

https://www.nature.com/articles/s41467-026-71773-6