25家机构押注,欧洲半导体自旋量子比特芯片产线正式启动

量子计算圈子里有个长期存在的尴尬,论文发了一篇又一篇,实验室里的量子比特性能一再刷新纪录,但一旦要问“能不能量产”,话题就容易陷入沉默。

欧洲这次想正面回答这个问题。

本月初(2026年4月3日),由世界领先的纳米技术研究机构 imec 牵头协调的SPINS量子中试线(Semiconductor Pilot line for Industrial Quantum NanoSystems)正式宣布启动。

项目总预算5000万欧元(折合约4.01亿人民币),资金来自欧盟芯片联合事业(Chips JU)及各成员国政府的联合投入。

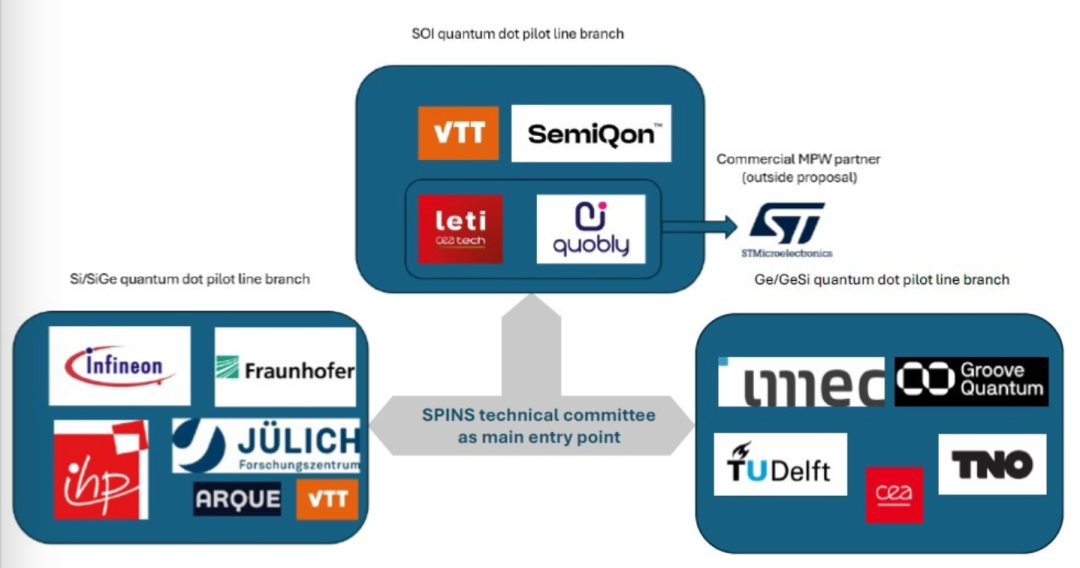

参与方涵盖25家欧洲科研机构、企业和高校,包括弗劳恩霍夫研究所、VTT技术研究中心、CEA-Leti公司、英飞凌、意法半导体以及代尔夫特理工大学等。

SPINS是欧盟《芯片法案》框架下设立的六条量子中试线之一,专注方向是半导体自旋量子比特。

图|SPINS量子中试线(来源:imec)

量子芯片研究领域并不缺成果,imec在300毫米工艺平台上制备的硅量子点自旋量子比特实现了创纪录的保真度,还在硅MOS量子点器件中引入了EUV光刻技术。但单个实验室做出来和能稳定量产、让外部企业上手用,是两回事。

SPINS要解决的核心问题,是在研究成果和可制造的量子处理器之间架一条路。

imec SPINS项目协调人Kristiaan De Greve解释了这件事的难度所在:量子比特对环境噪声极度敏感,稳定运行需要极其可控的环境和精密的制造流程,这既需要顶级半导体洁净室基础设施的精度,也需要能针对这些敏感器件持续调整工艺的研发能力。

imec做复杂半导体制造已经超过40年,通过整合欧洲联盟伙伴的专业知识,目标是加快高成熟度半导体量子比特的研发,推动在欧洲本土制造更大规模的量子系统。

SPINS同时推进三种半导体量子比特技术平台:Si/SiGe(硅/硅锗异质结构)、Ge/GeSi(锗/锗硅)和SOI(绝缘体上硅)。

三条路并行,一方面是因为目前哪条平台最终能胜出尚无定论,另一方面是各家合作机构在不同方向上的积累不同,分头推进也更有效率。

在分工上,imec主导Ge/GeSi平台在300毫米晶圆上的工艺探索。

CEA-Leti与Quobly、STMicroelectronics合作,负责推进与代工厂兼容的FD-SOI工艺,并主导量子工艺设计套件(PDK)开发和多项目晶圆(MPW)流片执行。

德国方向由弗劳恩霍夫IPMS研究所、IHP、英飞凌、Siltronic共同承担Si/SiGe技术的器件制造,Fraunhofer IPMS在德累斯顿的洁净室负责需要超越光学极限的高分辨率量子比特图形化加工。

图|SPINS量子中试线参与成员(来源:imec)

SPINS的另一个明确目标是降低生态准入门槛。

通过建立标准化的量子PDK和MPW机制,初创公司和中小企业可以在不自建昂贵制造基础设施的情况下,把自己的量子芯片设计放到工业级300毫米产线上验证。

这个逻辑和传统半导体行业的Fabless模式有几分相似,让设计方专注设计,制造能力由共享平台承接。

对于欧洲量子产业来说,这一点并不是锦上添花,而是能不能形成真正产业生态的关键。量子硬件创业公司普遍体量不大,独立建设和运维一条量子芯片生产线在经济上几乎不可行。中试线的意义,就是给这些公司一个进得去的门。

SPINS并非孤立项目,而是欧盟《芯片法案》下六条量子中试线中的一条。其余五条覆盖了当前主流的量子硬件技术路线:光子量子比特(P4Q,荷兰特文特大学主导)、离子阱(CHAMP-ION,奥地利SAL主导)、超导量子比特(SUPREME,芬兰VTT主导)、金刚石量子芯片(DIREQT,意大利CNR主导)以及中性原子(Q PLANET,法国Pasqal主导)。

从六条中试线并行推进的格局来看,欧洲并没有像某些企业那样赌某一种量子技术路线最终获胜,而是选择全线覆盖。这种策略成本更高,但在技术路径尚未收敛的阶段,也是规避押错路线风险的方式。

引用:

[1]https://www.imec-int.com/en/press/semiconductor-based-quantum-pilot-line-spins-launched-eu-support

[2]https://quantumcomputingreport.com/european-consortium-launches-spins-pilot-line-to-industrialize-semiconductor-quantum-chips/

联系与爆料: Qtumist_info@163.com

延 伸 阅 读