不止领跑!中性原子把量子纠错效率拉到极限

量子计算的终极梦想,是用数百万到数万亿次可靠操作,破解分子模拟、密码分析、优化问题等经典计算机无法企及的难题。但这一切的前提,是攻克量子纠错,将脆弱、易受干扰的物理量子比特,转化为能长期稳定运行的逻辑量子比特。

长期以来,主流方案的瓶颈清晰而残酷:表面码架构中,每1个逻辑量子比特需要上千个物理量子比特,庞大的硬件规模让实用化遥遥无期;量子低密度奇偶校验码(qLDPC)的编码率长期停留在1/10 到1/100,意味着要实现有意义的计算,需要数十万甚至上百万物理量子比特,远超当前技术的承载能力。

2026年4月,QuEra联合哈佛、MIT团队的一项突破,改写了这一局面:他们在中性原子平台上实现了超过1/2的超高编码率,以仅约2:1的物理-逻辑量子比特比,将每个校正周期的逻辑错误率可降至约10⁻¹³的Teraquop阈值——这正是大型量子算法所需的保真度门槛。这不仅是一次理论突破,更是为中性原子平台铺就了通往实用量子计算的清晰路径。

从1/100到1/2:量子纠错的效率革命

要理解这次突破的革命性意义,首先需要明确量子纠错领域长期存在的核心困局。

量子纠错的本质,是通过“冗余编码”来保护量子信息。但传统的量子纠错方案,始终无法突破“高冗余、低效率”的瓶颈。在主流的表面码架构中,每一个逻辑量子比特的实现,都需要上千个物理量子比特作为冗余支撑,这种庞大的硬件需求,让构建实用规模的量子计算机变得异常艰难。

而另一种被寄予厚望的方案——量子低密度奇偶校验码(qLDPC),虽然理论上具备更高的效率,但长期以来,其编码率始终停留在1/10到1/100之间,这意味着,要实现一个有实际计算价值的逻辑量子比特,需要数十甚至上百个物理量子比特,即便如此,其纠错性能也难以满足大型量子算法的需求。

更值得注意的是,经典LDPC码的编码率可达到90%以上,接近香农极限,这也让量子领域的研究者们始终坚信,qLDPC码具备突破效率瓶颈的潜力。但量子叠加态的脆弱性、量子操作的不可克隆性,以及硬件平台的交互限制,都让高编码率qLDPC码的实现面临重重阻碍。

转机出现在2025年,东京科学大学的Kenta Kasai团队提出了一种新型qLDPC码构造。首次从数学上证明了1/2编码率的量子纠错码是可实现的,这一理论突破,直接打破了长期以来困扰量子纠错领域的“效率天花板”。

Kasai团队的核心创新,是用仿射置换矩阵替代了传统qLDPC码中的循环置换矩阵,这种数学结构的调整,不仅突破了此前编码率的数学限制,还能在保证纠错能力的前提下,大幅降低编码和译码的复杂度。但理论突破与硬件实现之间,始终存在一道巨大的鸿沟:如何在真实的量子硬件平台上,实现这种超高编码率的qLDPC码?如何让代码的结构与硬件的特性相适配,避免出现“理论可行、实践无效”的尴尬?

QuEra、哈佛与MIT的联合团队,正是瞄准了这一核心问题,通过硬件与代码的协同设计,让Kasai的理论突破落地为可验证、可复用的实用成果。

硬件-代码协同设计:为中性原子量身定制的超高速纠错码

(一)为什么它能承载超高编码率?

QuEra之所以能在这场突破中脱颖而出,核心在于其选择的中性原子量子平台,恰好与超高编码率qLDPC码的需求形成了完美契合。

与超导量子比特、离子阱量子比特等传统平台不同,中性原子量子平台具有三大独特优势,为高编码率纠错码的实现提供了坚实的硬件基础。

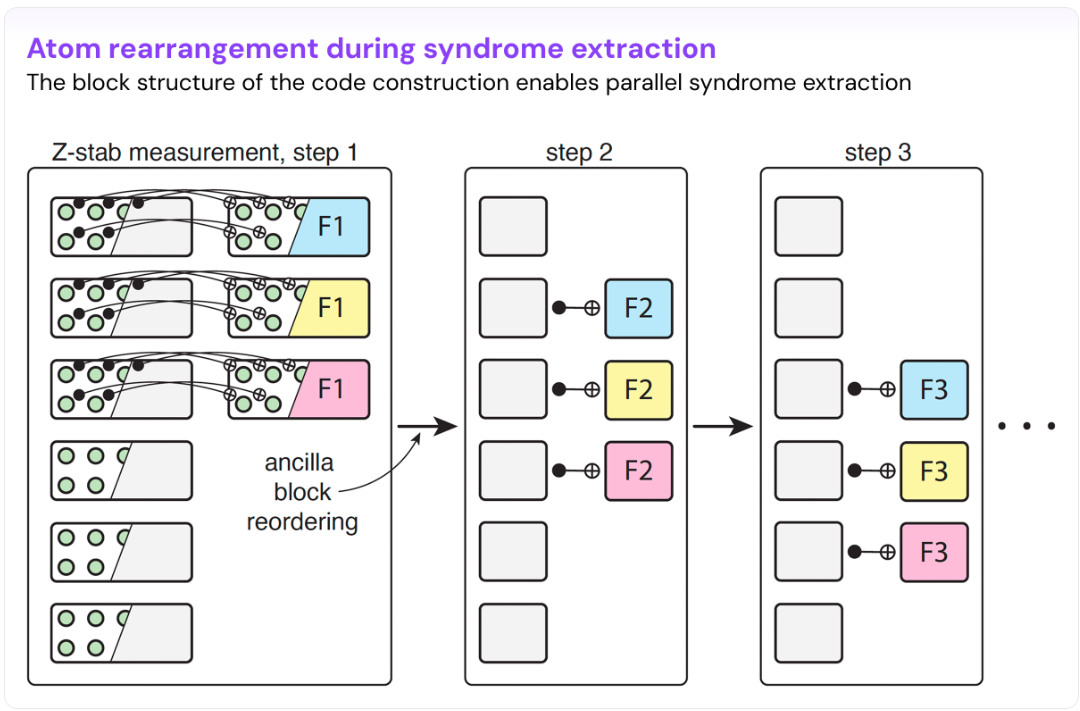

首先是可重构连接性,通过光镊(AOD)技术,研究团队可以灵活操控原子的位置和排列,让量子比特之间的交互不再受限于固定布线,能够根据qLDPC码的校验需求,随时调整原子的连接方式,这正是实现复杂校验结构的关键。其次是高度并行操作能力,AOD的行列结构支持大规模原子同时进行移动和操作,而qLDPC码的核心优势之一就是并行校验——能够同时对多个物理量子比特的状态进行校验,这种硬件与代码的并行特性,让纠错操作的效率大幅提升。最后是长相干时间,中性原子的相干时间远高于超导量子比特,能够为复杂的纠错过程提供充足的时间窗口,避免在纠错过程中因量子态衰减而产生新的错误。

(二)让代码与硬件“双向奔赴”

但仅仅具备硬件优势还不够,要实现超高编码率qLDPC码的实用化,必须让代码与硬件进行“双向奔赴”的协同设计——既不能让代码脱离硬件的实际能力,也不能让硬件的潜力被不合理的代码结构所束缚。

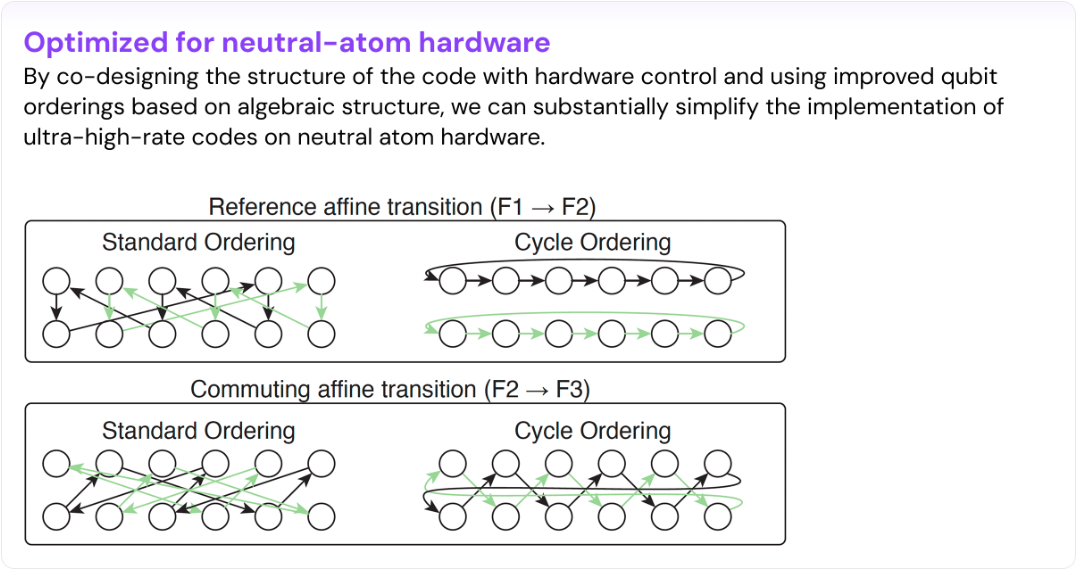

图:针对中性原子硬件优化

QuEra联合团队的核心创新,正是围绕这种协同设计展开,解决了从理论到实践的两大核心难题。第一个难题是如何让代码结构适配硬件的操作特性,降低原子移动的复杂度和操作深度。传统qLDPC码的校验矩阵结构,会导致原子需要进行复杂的移动才能完成校验操作,不仅操作难度大,还会增加量子态的衰减风险,降低纠错效率。为了解决这一问题,团队通过优化代码的校验矩阵结构,将原子的移动简化为固定深度的循环移位操作。以团队公布的n=1152、k=580的代码实例为例,原子被排列在3×32的网格中,每次综合征测量仅需一次水平移动和一次垂直移动,操作深度被压缩到常数级别,这不仅大幅降低了操作难度,还减少了量子态在操作过程中的衰减,为实现低逻辑错误率奠定了基础。

第二个难题是如何在保证纠错性能的前提下,放松代码的结构约束,实现实用规模的代码实例。Kasai的原始理论构造中,强调了“girth-8”(周长为8)的高约束条件,这种条件能够有效降低错误传播的概率,但在真实硬件的中等物理错误率下,这种高约束条件会大幅限制代码的规模,难以实现实用化。团队通过大量的模拟和实验发现,“girth-6”的代码在中等物理错误率场景下,同样能够实现优异的纠错性能,而这种约束条件的放松,大幅释放了代码搜索的自由度,让团队能够找到n=1000左右的实用规模代码实例——这正是第一代实用量子算法所需的硬件规模,也是连接实验室研究与实际应用的关键一步。这种“实用优先”的设计思路,让超高编码率qLDPC码摆脱了理论的束缚,真正具备了落地应用的可能。

硬核性能数据:万亿次操作仅1次错误,实用化的里程碑

任何科技突破的价值,最终都需要用硬核的性能数据来证明。

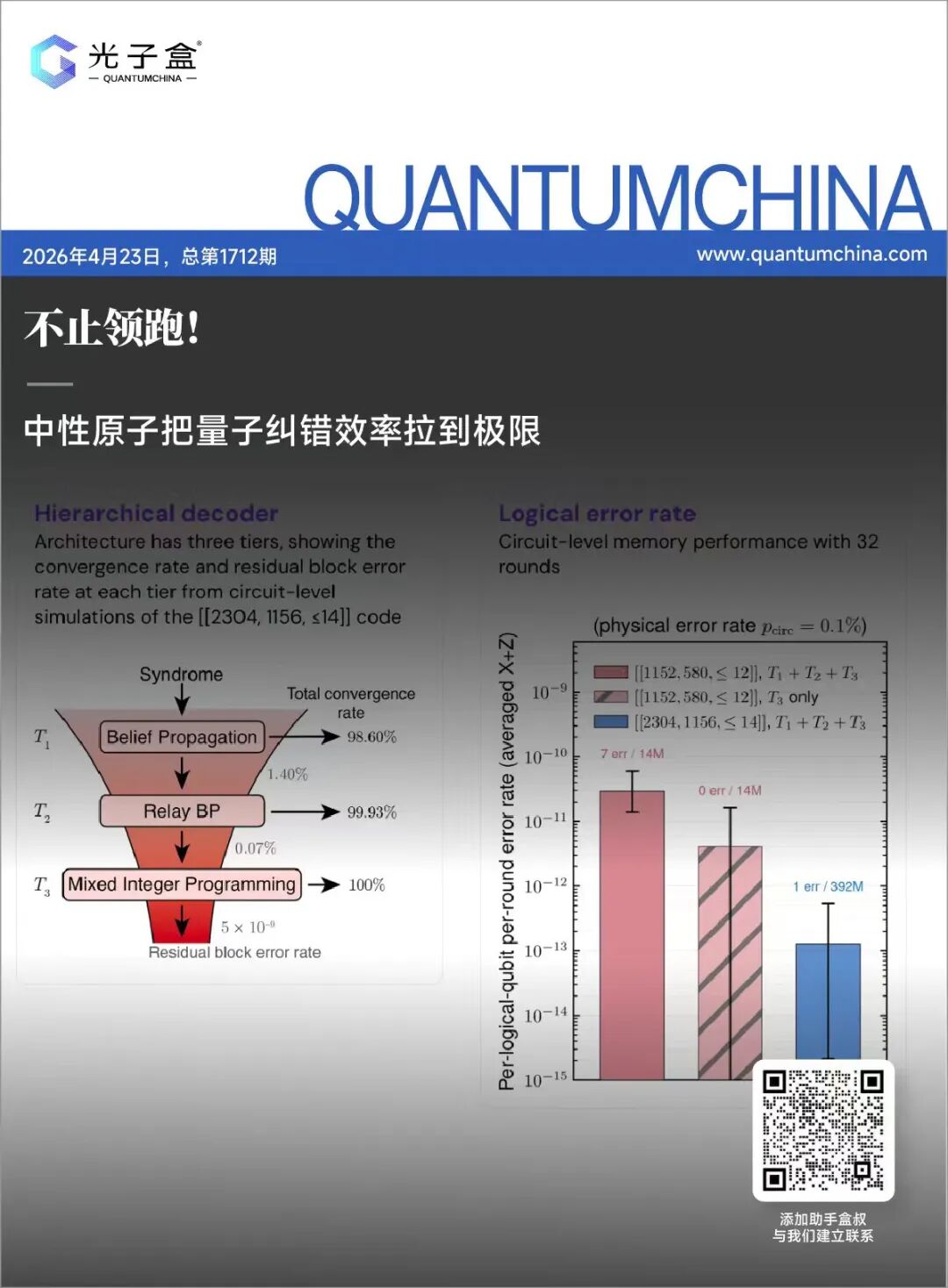

首先是编码率的突破,团队公布的两组核心代码实例,编码率均超过了1/2:其中一组代码使用1152个物理量子比特,编码出580个逻辑量子比特,编码率达到0.503;另一组代码使用2304个物理量子比特,编码出1156个逻辑量子比特,编码率达到0.502。这意味着,每2个物理量子比特就能编码1个逻辑量子比特,相比传统方案中每10个甚至100个物理量子比特才能编码1个逻辑量子比特的效率,硬件规模直接减少了数十倍。

这种效率的提升,不仅大幅降低了实用量子计算机的硬件成本,更让原本需要数百万物理量子比特才能实现的性能,现在只需数万物理量子比特即可达成,彻底打破了硬件规模的瓶颈。

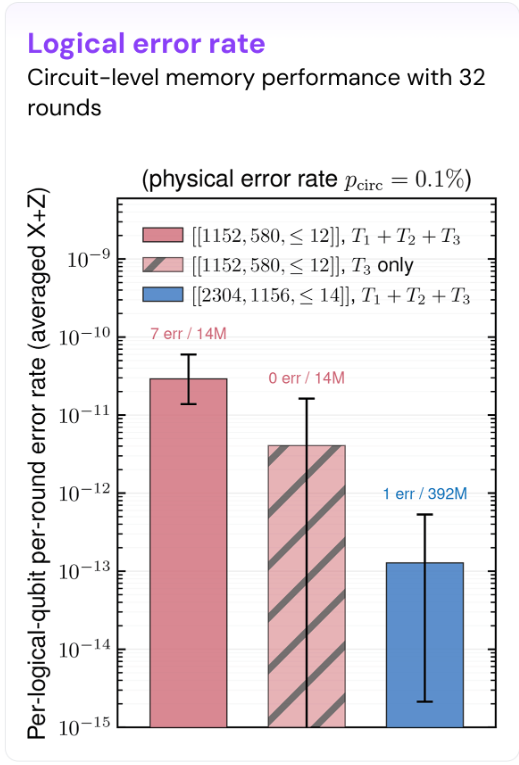

更重要的是,这次突破实现了逻辑错误率的大幅降低,触及了实用量子计算所需的“Teraquop”阈值。在物理错误率p=0.1%(对应99.9%的物理门保真度,中性原子平台正快速逼近这一指标)的电路级噪声模拟中,团队实现了1.3×10-13的每逻辑每轮错误率,这一数据恰好达到了大型量子算法所需的保真度门槛。这意味着,中性原子平台已经具备了支撑实用量子计算的核心能力。对于量子计算的实用化而言,逻辑错误率的突破远比硬件规模的扩大更为关键——只有实现了低逻辑错误率,才能保证量子算法的可靠运行,才能让量子计算真正发挥其优势。

验证的严谨性:为什么这一结果值得信赖?

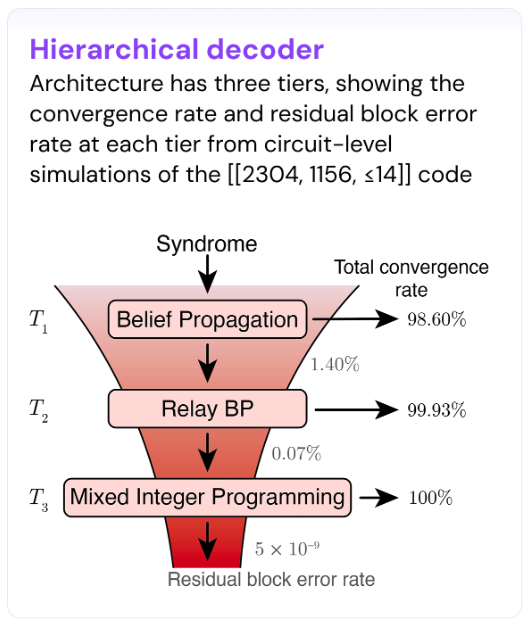

值得强调的是,这次突破的成果并非通过理论估算得出,而是经过了严谨的模拟验证,其可信度得到了行业内的广泛认可。量子纠错的模拟验证,向来存在“速度与精度的两难”:如果采用简化的噪声模型,虽然能够快速完成模拟,但结果缺乏说服力,无法反映真实硬件的运行情况;如果采用复杂的电路级噪声模型,虽然能够保证精度,但模拟速度极慢,难以验证低错误率场景。为了解决这一难题,QuEra联合团队设计了一种分层解码器架构,在速度与精度之间找到了最优解。

图:分层解码器

这种架构分为三层:第一层是快速信念传播(BP)解码器,能够处理绝大多数常见的错误场景,速度快、效率高,为模拟提供了基础;第二层是中继BP解码器,专门处理标准BP解码器无法收敛的边缘错误情况,确保纠错的全面性;第三层是整数规划解码器,用于处理剩余的极端错误模式,避免出现错误遗漏。

这种分层架构的优势在于,既保留了信念传播解码器的速度优势,又通过后两层解码器弥补了精度不足的问题,实现了“近BP的速度+高精度的解码能力”。团队通过数百万次的采样模拟,直接输出了目标低错误率场景的结果,而非通过高错误率数据进行外推估算,这让最终的逻辑错误率数据具备了极高的可信度。

不止于纠错:中性原子平台的容错生态正在成型

这次超高编码率qLDPC码的突破,并非孤立事件,而是中性原子平台在量子纠错领域持续突破的又一里程碑:

2024年,QuEra与哈佛团队在448原子阵列上实现了低于容错阈值的逻辑量子比特;

2025年,团队提出横向算法容错(AFT)框架,将纠错带来的运行开销降低了数个数量级;

2026年,这次超高编码率qLDPC码的突破,让硬件规模的瓶颈彻底松动。

中性原子平台的优势正在形成闭环:可重构连接性、并行操作能力、长相干时间,支撑了从代码构造、纠错实现到解码优化的全链条创新,让它成为当前容错量子计算最具竞争力的路线之一。

当编码率从1/100 跃升至 1/2,量子纠错的硬件需求不再是 “天文数字”。对于正在制定量子计算战略的政府、企业和研究机构而言,这一结果意味着:一台实用型量子计算机的物理规模,可能远小于此前的预期。

这一突破不仅会影响基础设施布局和技术路线选择,更将加速量子计算从实验室走向实用化的进程。而QuEra的中性原子平台,正站在这一浪潮的中心,为容错量子计算铺就了一条清晰、可行的道路。未来的挑战依然存在,但方向已经明确:在代码、硬件与算法的协同演进中,中性原子平台正在一步步将量子计算的梦想,变为触手可及的现实。

[1]https://arxiv.org/pdf/2604.16209

[2]https://www.quera.com/blog-posts/quantum-error-correction-at-record-efficiency-why-neutral-atoms-are-leading-the-way

[3]https://thequantuminsider.com/2026/04/21/quera-led-study-points-to-ultra-high-rate-quantum-error-correction-moving-closer-to-practical-hardware/