三星与SK海力士在DRAM制造中采用EUV及高NA EUV的路线图

近年来,随着DRAM制程节点不断微缩,光刻工艺的精度和成本成为各大厂商竞争的关键。在众多存储器制造商中,韩国三星和SK海力士率先将极紫外(EUV)光刻技术引入DRAM生产,并积极布局下一代高数值孔径(High-NA)EUV技术。本文将梳理这两家厂商的技术路线与时间节点,并分析其在成本与工艺稳定性之间的权衡。

三星:率先采用EUV的DRAM玩家

依托在晶圆代工业务中积累的丰富经验,三星成为全球第一家将EUV光刻用于DRAM量产的厂商。早在1x nm节点,三星就将EUV光刻作为测试载体进行前期验证。到了2020年,三星在1z nm DRAM中正式启用EUV技术——尽管当时仅用于一个关键层(1 layer)。这一谨慎的导入策略,既降低了工艺风险,也为后续扩展EUV使用层数奠定了基础。

SK海力士跟进:专用产线建成

紧随三星之后,SK海力士也在积极推动EUV的落地。2021年2月,SK海力士宣布完成了首条配备EUV光刻设备的DRAM生产线。基于这条产线,该公司计划在2021年下半年开始生产1a nm DRAM。至此,两大韩国存储器巨头均将EUV纳入了主流制造流程。

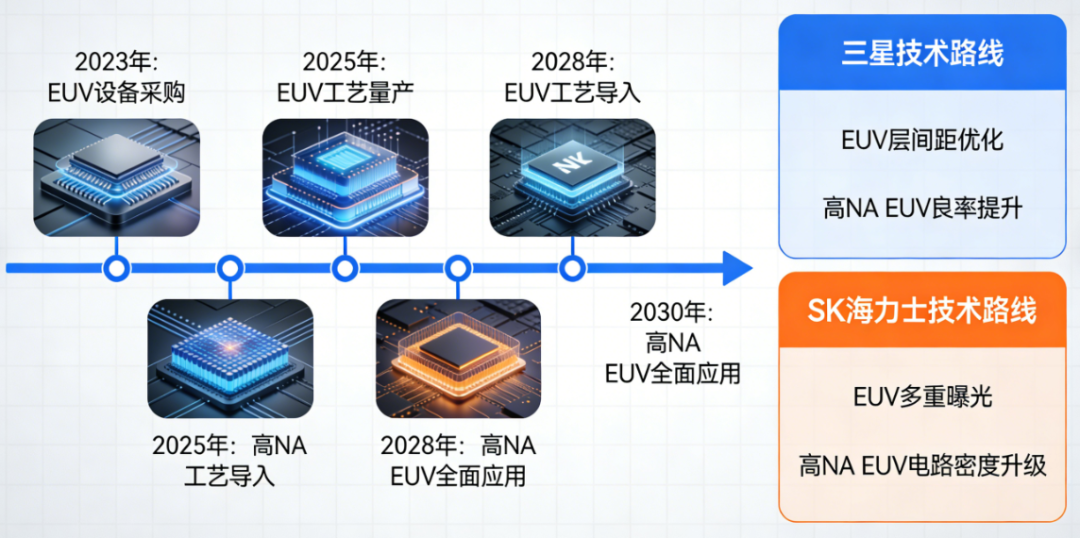

下一代High-NA EUV路线图

EUV光刻的下一代演进方向是High-NA(数值孔径从0.33提高到0.55)EUV,它能够实现更小的特征尺寸,减少多重图形化的次数。三星和SK海力士均已将High-NA EUV列入各自的开发路线图。

根据公开信息,预计在未来3至4年内(即约2025-2026年),两家公司将开始生产采用High-NA EUV技术的DRAM样品,并着手准备大规模量产。不过,真正实现量产可能要到2026年之后,对应节点大约在10nm以下级别(如s10nm或更先进节点)。

成本压力下的替代方案:自对准多重图形化

EUV设备极其昂贵,每台售价高达上亿欧元,且折旧成本高昂。为了在不完全依赖EUV的情况下保持竞争力,部分DRAM厂商(尤其是一些未能及早获得EUV产能的厂商)长期采用自对准多重图形化(Self-Aligned Multiple Patterning, SAMP)技术。这种方法通过多次沉积、刻蚀和侧墙工艺,用传统深紫外(DUV)光刻实现接近EUV的分辨率,使得位单元尺寸可以做到非常接近韩国竞争对手(三星、SK海力士)的水平。

然而,随着DRAM节点推进到10nm级别及以下,多重图形化的工艺步骤呈指数级增加。层与层之间的套刻误差、边缘放置误差(EPE)以及缺陷控制变得极其困难,生产稳定性面临严峻挑战。这也正是三星和SK海力士宁可承受高昂的设备成本,也要加速导入EUV乃至High-NA EUV的根本原因——在极致微缩的节点上,多重图形化的物理极限和良率瓶颈已难以突破。

总结

三星于2020年在1z nm DRAM中首次引入EUV,SK海力士则在2021年建成专用EUV产线并用于1a nm DRAM。两家韩国厂商均已规划在2026年后采用High-NA EUV实现更先进节点的量产。与此同时,虽然自对准多重图形化技术曾帮助部分厂商在成本上获得竞争优势,但随着节点微缩,其工艺稳定性和良率问题日益凸显,EUV正成为高密度DRAM制造的必然选择。