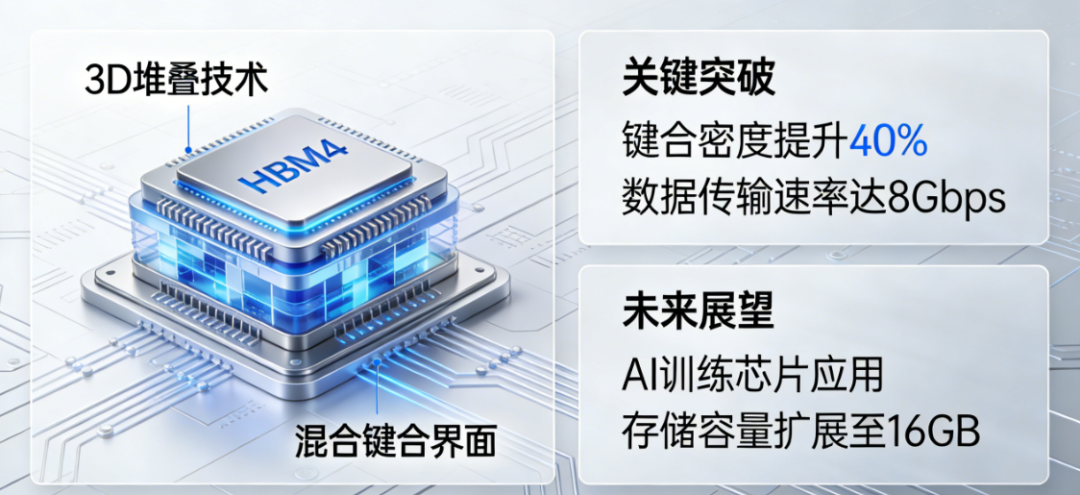

混合键合技术:HBM4世代的关键突破与未来展望

随着人工智能、高性能计算(HPC)和图形处理需求的爆发式增长,高带宽存储器(HBM)已成为先进封装领域不可或缺的核心组件。然而,在当前的HBM世代(如HBM3、HBM3E)中,一项被广泛看好的互连技术——混合键合(Hybrid Bonding)——尚未得到实际应用。本文将从技术现状、驱动因素及产业布局三个维度,解析混合键合为何是HBM4世代不可或缺的关键技术。

一、现状:混合键合尚未用于现有HBM

截至目前,三星、SK海力士和美光三大HBM制造商所量产的HBM产品(包括HBM3及HBM3E)仍沿用基于微凸块(Microbump)的热压键合(TCB)工艺。该工艺通过在DRAM芯片间堆叠时使用微小焊料凸块实现电气连接,技术成熟且良率可控。

混合键合之所以尚未被采用,主要源于两大工程挑战:

工艺兼容性:混合键合要求芯片表面极度平坦、洁净,且需精确控制铜焊盘凹陷与键合压力,对现有HBM生产线改造成本高。 热预算与翘曲:多层DRAM堆叠(如12层)会产生显著的机械应力和热翘曲,混合键合对堆叠后的整体形变更为敏感。

二、驱动力:为何HBM4必须引入混合键合?

尽管存在技术障碍,但未来三年内混合键合将成为HBM制造的核心工艺。原因可归纳为三个“必须”:

1. 带宽与功耗必须持续优化

混合键合通过无凸块直接铜-铜键合,可大幅缩短互连间距(从40μm降至10μm以下),显著降低寄生电容和电阻。这意味着:

信号传输速度提升,I/O数据速率可突破10Gbps以上; 单位比特功耗降低30%~50%,这对动辄数百瓦的AI加速器至关重要。

2. HBM堆叠厚度必须最小化

目前12层HBM3堆叠厚度已接近800μm。若沿用微凸块技术堆叠16层DRAM,总厚度将超过1.1mm,超出JEDEC标准封装厚度限制。混合键合去除了凸块及底部填充层,使单层互连高度从20~30μm锐减至5μm以下,16层堆叠总厚度可控制在700μm以内,与现有12层产品相当。

3. 16层堆叠(16Hi)成为刚需

HBM4规范将原生支持16层DRAM堆叠(即16Hi),以提供2TB/s以上的聚合带宽。但当前HBM3虽在标准上支持16Hi,却没有厂商实际量产——因为微凸块带来的应力累积和散热瓶颈无法满足16层产品的可靠性要求。混合键合凭借其均匀的压力分布和更高的导热系数,是唯一可行的工程解。

三、路线图:HBM4世代正式导入混合键合

根据行业公开信息,三大厂商的规划高度一致:

三星:HBM3P(即三星对HBM3E的命名)仍使用微凸块,但HBM4将全面转向混合键合。三星已展示基于铜混合键合的16层堆叠测试芯片。 SK海力士:明确宣布HBM4将引入混合键合技术,并与先进封装(如MR-MUF)结合,优先解决散热问题。 美光:其HBM3 Gen 2(即美光版HBM3E)继续沿用现有工艺,而下一代产品HBMNext(美光当前对HBM4的称呼)确定采用混合键合,目标实现16层堆叠。

四、技术挑战与产业影响

尽管方向明确,混合键合的大规模量产仍面临:

键合对准精度:16层堆叠要求每层对准误差小于0.5μm,需依赖先进的晶圆对准与检测设备。 修复与良率:传统微凸块可通过局部返修替换失效芯片,而混合键合后几乎无法无损拆分层叠,必须依赖“已知良好裸晶”(KGD)的极致筛选。

从产业格局看,率先攻克混合键合量产的厂商将获得显著先发优势。设备端,EV Group、BESI、SUSS MicroTec等公司的混合键合设备已进入HBM产线验证阶段;材料端,导电胶、临时键合胶等供应链也将随之重塑。

结语

混合键合并非一项“未来技术”,而是HBM从12层迈向16层、从1TB/s冲向2TB/s带宽的必经之路。虽然当前HBM3/HBM3E世代仍由成熟的微凸块统治,但自2025年下半年起,随着HBM4的量产启动,混合键合将正式从实验室走向生产线,成为下一代高带宽存储器的核心工艺基石。对于芯片设计、封装和系统集成工程师而言,提前理解其原理与局限,将是把握下一代AI计算性能瓶颈的关键。