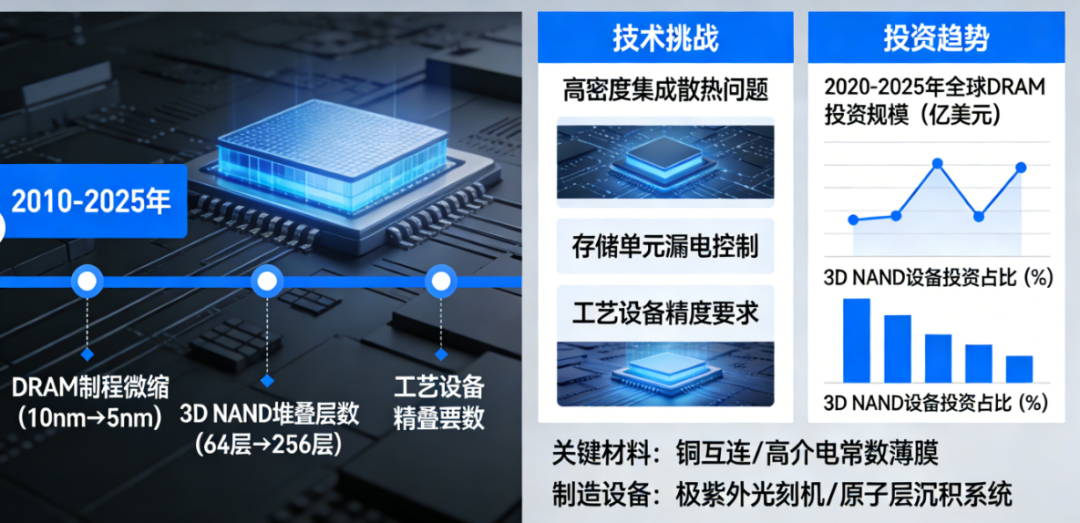

内存制造复杂性的演进:DRAM与3D NAND的技术挑战与投资趋势

随着每一代NAND和DRAM技术的更迭,半导体存储器的制造复杂性持续攀升。这不仅推动了对尖端晶圆设备(WFE)的巨额投入,也迫使厂商不断新建或扩建晶圆厂厂房(fab shell)。本文将从DRAM和3D NAND两条技术路线出发,分别剖析其核心制造难点、光刻与刻蚀工艺的演进,以及相应的资本支出方向。

一、DRAM:光刻收缩趋缓,多重图案化与EUV并行

DRAM的位密度增长正变得越来越昂贵,其根本原因在于光刻技术的物理极限日益逼近。随着制程节点从1x、1y、1z向1α、1β、1γ推进,传统193nm浸没式光刻(193i)已无法单次曝光满足最小半节距的要求。

1. 多重图案化成为节点迁移的“成本放大器”

每一代节点迁移都伴随着多重图案化(Multi-patterning)需求的增加。例如,自2x nm节点起,DRAM的活跃区(AA)和字线(WL)就需要采用自对准双重图案化(SADP)甚至四重图案化(SAQP)。这导致每片晶圆的光刻及刻蚀步骤数成倍增加,不仅直接拉长了工艺周期,还大幅提高了对洁净室空间的需求——因为更多设备需要并行布置,同时在线晶圆缓存(WIP)面积也必须扩大。

据业界估算,从1y nm到1α nm,DRAM的光刻层数增加了约15~20%,其中关键层的多重图案化步骤增加了30%以上。每增加一次图案化循环,就意味着额外的一次沉积、刻蚀和清洗,直接推高了单片的运营成本(COO)。

2. EUV介入:以设备投资换取工艺简化

为了突破多重图案化的复杂度瓶颈,领先DRAM厂商(如三星、SK海力士、美光)已开始在高节点引入极紫外(EUV)光刻。EUV的13.5nm波长可以单次曝光完成原本需要SADP或SAQP才能实现的图形,从而大幅削减工艺步骤和掩模数量。

然而,EUV并非“免费的解药”。一台高数值孔径(High-NA)EUV光刻机的单价已超过3亿美元,且配套的光刻胶、掩模防护膜(pellicle)、光源稳定性维护等成本也远高于193i系统。此外,EUV光刻机的输出功率和晶圆吞吐量仍需持续优化,导致其每小时的折旧成本极高。因此,采用EUV的DRAM晶圆厂必须保证极高的设备利用率(>85%)才能实现盈亏平衡。

二、3D NAND:不依赖先进EUV,但沉积与刻蚀是“深水区”

与DRAM截然不同,3D NAND的核心扩展逻辑并非缩小线宽,而是增加存储单元的堆叠层数。因此,它不需要昂贵的EUV光刻来解析极小尺寸,但其制造挑战集中在薄膜沉积和干法刻蚀两个领域。

1. 高深宽比(HAR)刻蚀:技术皇冠上的明珠

3D NAND的字线结构通过交替沉积氧化物(SiO₂)和氮化物(Si₃N₄)形成数十至上百层的介电堆叠,然后刻蚀出贯穿整个堆叠的沟道孔(Channel Hole)和栅线缝隙(Slit)。以当前200层以上的3D NAND为例,沟道孔的深宽比已超过60:1,甚至向80:1迈进。

这种超高深宽比的干法刻蚀需要极其精密的工艺控制:

刻蚀速率均匀性:从孔顶到底部,刻蚀速率必须高度一致,否则会导致底部未开穿或顶部过度刻蚀造成孔扭曲。 侧壁垂直度与粗糙度:任何侧壁弯曲或波纹都会影响后续多晶硅沟道层的沉积质量,进而引发存储单元阈值电压漂移。 选择性控制:刻蚀工艺必须对氧化物和氮化物具有接近1:1的选择比,同时对抗刻蚀掩模(非晶碳或多晶硅)保持足够高的选择性。

目前,只有少数供应商(如泛林半导体、东京电子)的专用HAR刻蚀机台能够满足量产要求,单台设备价格可达500~800万美元,且一条月产10万片的先进3D NAND产线需要数百台此类刻蚀设备。

2. 沉积工艺:从层数竞赛到薄膜应力管理

随着堆叠层数从128层向256层、300层以上演进,薄膜沉积面临两大难题:

周期时间:每增加一层氧化-氮化对,就需要额外一次沉积循环。如果沉积速率不提升,生产周期将线性增长。因此,厂商采用批量式(batch)或空间原子层沉积(SALD)技术来提高吞吐量。 薄膜应力累积:数百层交替膜的内应力叠加可能导致晶圆翘曲(warpage)甚至破片。需要通过调节沉积参数(如等离子体功率、前驱体比例)实现压应力和张应力的平衡。

三、资本支出趋势:设备与厂房的双重压力

无论是DRAM还是3D NAND,新制程节点的导入都迫使内存制造商在两个方面进行大规模投资:

前沿WFE设备:

DRAM侧:EUV光刻机、高精度多重图案化刻蚀/沉积设备、掩模检测系统。 3D NAND侧:HAR刻蚀机、高生产率ALD/CVD系统、低温沉积设备(用于金属字线替代工艺)。 新晶圆厂外壳(fab shell):

多重图案化和HAR刻蚀均大幅增加了每片晶圆的工艺步骤数(DRAM可能增加40%以上步骤,3D NAND增加60%以上),这要求更大的洁净室面积来容纳额外机台。 此外,EUV光刻机对震动、温度和颗粒控制极其敏感,需要专门设计的超洁净区域(每立方米颗粒数<1),进一步推高了土建与维护成本。

结语

总结而言,内存制造的复杂性增长呈现出两条截然不同的技术路径:DRAM依靠多重图案化与EUV的渐进式替代,在光刻领域进行昂贵的“阵地战”;而3D NAND则通过不断加高存储堆叠,在深宽比刻蚀和薄膜沉积的“极限运动”中寻求突破。无论哪条路线,都意味着更昂贵的设备、更庞大的晶圆厂以及更严苛的工艺控制。对于内存厂商而言,能否在技术复杂性和资本效率之间找到平衡点,将成为未来十年竞争格局的关键。