内存控制器在多核CPU性能扩展中的关键作用与DDR5时代的内存架构演进

一、引言

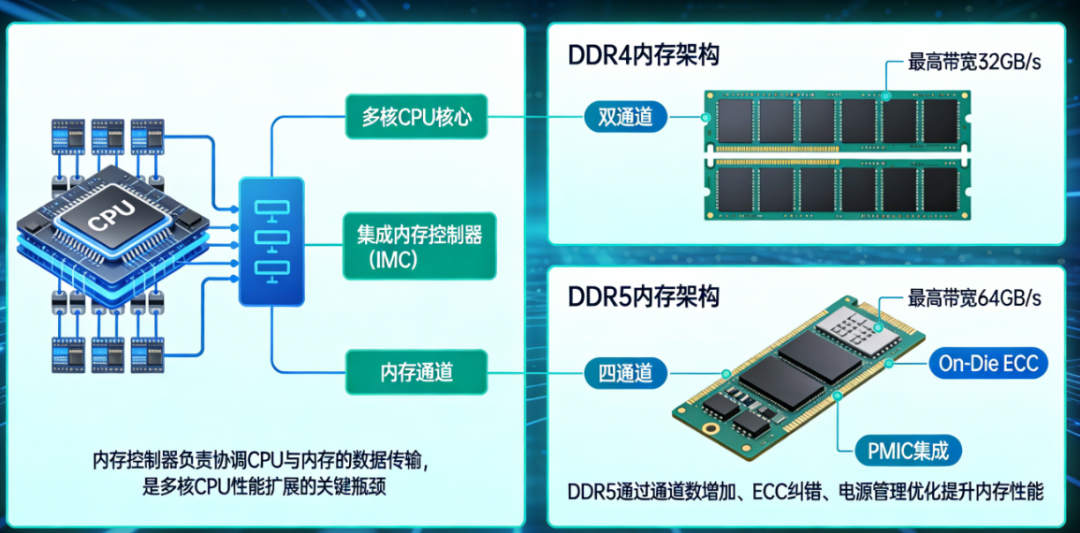

随着计算需求的持续攀升,多核处理器已成为现代计算体系的标准配置。然而,单纯增加核心数量并不能线性提升系统性能——内存子系统的瓶颈日益成为制约多核扩展的核心障碍。在这一背景下,内存控制器(Memory Controller) 作为CPU与DRAM之间的关键桥梁,在多核系统的性能扩展中扮演着不可替代的核心角色。与此同时,DDR5内存在2024年迎来加速渗透的关键拐点,成为推动内存性能跃升的主力技术。

二、多核系统中的内存瓶颈:控制器为何成为关键

在多核系统中,所有核心共享对主存的访问通道。传统统一内存访问架构(UMA)中,所有核心通过一条前端总线(FSB)连接至北桥芯片组,再由北桥访问RAM[reference:0]。访问动态随机存取存储器(DRAM)需要数百个CPU周期,而内存控制器通常只有一个端口,同一时刻只能有一个核心访问RAM[reference:1]。随着核心数量增加,多个核心争夺有限的内存带宽,系统将出现严重的“内存竞争”现象,导致性能停滞甚至下降。

具体而言,多核内存瓶颈主要体现在三个层面:

1. 单端口内存控制器的串行化访问:传统内存控制器每次仅能服务一个核心的内存请求,其余核心必须排队等待,使内存访问路径成为系统中最拥挤的“交通要道”。

2. 共享缓存的污染与驱逐:现代CPU使用静态随机存取存储器(SRAM)作为多级缓存以缓解内存延迟。然而,末级缓存(LLC)为所有核心共享。当一个核心加载大量数据时,可能“驱逐”其他核心仍需使用的数据,迫使这些数据从主存重新加载,大幅降低缓存命中率[reference:2]。

3. 缓存一致性协议的开销:在多核环境中,MESI协议(Modified-Exclusive-Shared-Invalid)等缓存一致性机制需要核心之间频繁“嗅探”缓存状态。若两个核心频繁读写同一变量,一次简单的缓存修改可能触发总线上的所有权请求,使原本高速的缓存操作降级为慢速的主存访问[reference:3]。

三、内存控制器架构的演进:从瓶颈到解决方案

3.1 分布式内存控制器:NUMA架构的兴起

解决多核内存瓶颈的核心思路之一是分布式内存控制器。研究表明,引入多个分布式内存控制器最符合多核处理器的内存需求,在大多数情况下,在处理器中集成内存控制器有助于显著提升性能[reference:4]。这一思想催生了非统一内存访问架构(NUMA):每个CPU集成自己的内存控制器,直接访问“本地”内存,不同CPU之间通过高速互联(如英特尔的QuickPath Interconnect或UltraPath Interconnect)实现缓存一致性的全局内存访问[reference:5]。

NUMA架构将原本单一的内存控制器“化整为零”,使每个核心或每组核心拥有更近的内存访问路径,有效降低了内存访问延迟,增强了多核系统的可扩展性。对于多插槽和多核心系统,分布式内存控制器成为性能扩展的基石。

3.2 片上互连拓扑的优化

除内存控制器本身外,CPU片上互连架构同样影响多核扩展能力。英特尔至强可扩展处理器采用的Mesh(网格)片上互连拓扑,将核心、缓存库、内存控制器和I/O控制器按行列组织,在每个交叉口通过交换开关连接[reference:6]。这种设计在内核、内存和I/O控制器之间提供低延迟和高带宽,确保可用的互连带宽能够随核心数量扩展。

3.3 新型内存控制器:从单纯扩展到“计算+存储”融合

近年来,内存控制器正从被动的数据传输通道向主动的智能节点演进。Marvell在2024年推出的Structera A是一款基于CXL Type-3的内存扩展控制器,革命性地将16个Arm Neoverse V2核心与CXL内存扩展功能集成于一体,打破了传统内存控制器仅专注于内存管理的局限,赋予芯片在计算与内存扩展方面的双重能力[reference:7]。该芯片支持四通道DDR5-6400内存,并内置LZ4压缩/解压缩功能,能够在芯片内部高效处理数据,减少数据传输带来的延迟与带宽消耗[reference:8]。这种“内存计算一体化”的趋势预示着未来芯片设计将更加注重计算与存储的紧密结合,从根本上减少数据搬运的开销。

四、DDR5:应对多核内存瓶颈的技术突破

4.1 DDR5的核心性能跃升

DDR5内存在多个维度上显著提升了内存系统的性能天花板。相较于DDR4,DDR5将每个DIMM的通道拆分为两个独立子通道,提升了并行访问能力;数据速率起步即为4800 MT/s,并持续向更高速率演进。以瑞萨电子(Renesas)发布的第六代DDR5寄存时钟驱动器(RCD)为例,其支持高达9600 MT/s的数据传输速率,旨在缩小先进处理器性能扩展与内存性能扩展之间的差距[reference:9][reference:10]。

4.2 MRDIMM:DDR5时代的带宽倍增技术

为进一步满足AI、高性能计算(HPC)等带宽饥渴型应用的需求,JEDEC开发了多路复用列双列直插内存模组(MRDIMM) 技术。MRDIMM能够实现每个周期128字节的数据传输,相当于标准DDR5 DIMM的64字节的两倍,可将每模组内存带宽大致翻倍[reference:11]。在英特尔至强6处理器上,MRDIMM为HPC工作负载提供高达2.3倍的性能提升,为AI推理提供2倍的性能提升[reference:12]。

MRDIMM通过在模组上使用缓冲区将两个列的数据合并,实现8800 MT/s以上的数据速率[reference:13]。其关键组件包括多路复用寄存时钟驱动器(MRCD)和多路复用数据缓冲器(MDB),每个MRDIMM 12800需要一颗MRCD和十颗MDB芯片,将内存通道进行多路复用[reference:14]。这一架构确保内存带宽的增长能够匹配CPU核心数量的扩展,最大化系统性能[reference:15]。

4.3 内存接口芯片:DDR5生态的关键支柱

DDR5时代的内存接口芯片市场高度集中,澜起科技(Montage Technology)、瑞萨(Renesas/IDT)和Rambus三家厂商主导市场。澜起科技作为全球DDR5内存接口芯片龙头,市场份额达46%[reference:16]。该公司已推出支持高达7200 MT/s的第四代DDR5内存驱动芯片,并积极布局MRCD/MDB、CXL内存控制器(MXC)等下一代产品[reference:17][reference:18]。

五、DDR5市场渗透:2024年迎来关键拐点

5.1 渗透率突破50%

根据TrendForce集邦咨询的存储器产业分析报告,DDR5正在经历加速渗透。2023年年底,DDR5渗透率约为25%至30%;预计2024年第三季度将突破50%[reference:19]。在服务器DRAM领域,DDR5预计将贡献2024年服务器DRAM位元出货量的40%,并于2025年进一步攀升至60%至65%[reference:20][reference:21]。与此同时,LPDDR5/5X在移动DRAM领域的位元出货量占比预计在2024年达到50%,2025年提升至60%[reference:22]。

5.2 主要云服务商的DDR5采用情况

主要云服务提供商(CSP)的DDR5采用率已呈现显著增长。截至2024年第二季度,AWS的DDR5使用比例达38%,Meta为33%,Google约为45%,而Azure为17%[reference:23]。传统服务器制造商如HPE和Dell的采用率分别为18%和约26%[reference:24]。这一分布反映出DDR5正在从高端云应用向主流服务器市场加速扩散。

5.3 驱动因素:AI与数据中心需求

DDR5渗透加速的核心驱动力来自AI数据中心和HPC应用对内存带宽和容量的迫切需求。2024年DRAM产业营收预计将达到907亿美元,同比增长75%[reference:25]。高带宽内存(HBM)、DDR5和LPDDR5/5X等高附加值产品的渗透共同拉高了产业平均价格[reference:26]。展望2025年,DRAM产业营收预计将进一步增长51%,达到1365亿美元[reference:27]。

六、展望与总结

内存控制器在多核CPU性能扩展中发挥着从“瓶颈”到“赋能者”的关键转变。分布式内存控制器、NUMA架构和片上互连优化为多核扩展奠定了基础;DDR5及其衍生的MRDIMM等技术则从带宽和容量两个维度提供了突破性的解决方案;而CXL和“计算+存储”融合型内存控制器的出现,预示着内存子系统正从被动响应走向主动智能。

展望未来,随着DDR5渗透率在2024年突破50%关键门槛,并在2025年进一步扩大优势,内存子系统与多核处理器之间的“性能剪刀差”有望得到实质性缓解。内存控制器将持续演进,成为连接计算核心与存储世界的战略枢纽,为AI、HPC和超大规模数据中心提供更强大的性能支撑。

参考文献

[1] TrendForce集邦咨询. 2024年全球DRAM和NAND产业营收将分别增长75%和77%. 2024-07-22.[reference:28]

[2] 民生证券. 深度报告:DDR5加速渗透,新品驱动未来. 2024-03-10.[reference:29]

[3] IntervalZero. Why More Cores Don’t Always Mean Faster Performance. IAA.[reference:30]

[4] 英特尔. What Is Multiplexed Combined Rank DIMM (MCR DIMM) on Intel Xeon 6 Processors. 2026-02-25.[reference:31]

[5] 芝能智芯. 技术解析|Marvell Structera A 内存芯片. OFweek. 2024-12-17.[reference:32]

[6] Renesas. DDR5 Registered Clock Driver Breaks Glass Ceiling for Data Rates. All About Circuits. 2025-11-20.[reference:33]

[7] Rambus. DDR5 Multiplexed Registering Clock Driver (MRCD) and Multiplexed Data Buffer (MDB).[reference:34]

[8] TrendForce. Rising Average Prices, HBM and QLC to Fuel Memory Industry Revenue Growth. EE Times Asia. 2024-08-05.[reference:35]

[9] CSDN. 服务器与内存市场|2025预测动态早知道. 2024-10-10.[reference:36]

[10] IT168. 从CPU、内存和I/O深度理解IA架构服务器. 2010-08-17.[reference:37]