PAEMS:首个自主跨平台超导比特精确误差模型,剑指量子纠错解码专用ASIC芯片!

在量子计算走向容错化的过程中,超导量子处理器正站在一个微妙的十字路口。一边是IBM、Google等巨头不断刷新量子比特数量的纪录,另一边,却是量子纠错(QEC)这一核心命题始终未能完全突破实用化门槛。究其根本,还是我们的量子比特误差模型,太“理想化”了。

近日,电子科技大学王成教授团队联合国防科技大学、军事科学院等组成的研究团队在预印本平台arxiv发表题为“PAEMS:Precise and Adaptive Error Model for Superconducting Quantum Processors”(PAEMS:用于超导量子处理器的精确和自适应误差模型)的研究论文,何松桓为论文第一作者,王成教授为论文通讯作者。

本研究提出了一种名为PAEMS的精确且自适应的量子比特误差模型。该模型采用融合泄漏传播的逐比特分离框架,可捕获跨时空域的误差演化。基于重复码实验数据集,PAEMS通过端到端优化流程有效识别量子比特本征误差。在IBM量子处理器上的实验表明,该模型将时序、空序及时空误差相关性偏差分别降低19.5倍、9.3倍与5.2倍,性能超越所有现有工作。在IBM Brisbane、Sherbrooke、Torino、中国移动“五岳”与国盾“天衍”等多量子平台上,PAEMS精度较谷歌SI1000误差模型提升58%-73%。

可见,这不仅是一项技术的突破,更可能成为加速量子纠错(QEC)发展的关键“催化剂”。

研究背景

超导量子处理器凭借百至千级量子比特规模、二维平面互耦结构与成熟的量子-经典接口,成为量子纠错(QEC)与量子误差缓解(QEM)的主流平台。

近期该领域接连取得突破:逻辑量子比特克服规模化附加误差、谷歌超导量子处理器“Willow”实现阈值以下表面码存储、色码实现逻辑误差抑制规模化、超导量子处理器完成随机采样验证等。目前已发布千级以上超导量子比特的处理器,相关研究规划了迈向实用量子计算机的百万超导比特路线图。

然而,受量子比特非理想特性(如器件差异性、校准滞后、操控与读取保真度不足)制约,量子纠错仅在5-105比特小规模系统上得到验证,且统计数据不足。这就使得量子纠错解码器高度依赖由量子比特误差模型生成的合成数据,误差模型的精度与可靠性,直接决定了解码器在真实设备上的表现。

传统误差模型分为两类,各有致命缺陷:一类是经典去极化模型,复杂度低但精度极差,默认所有比特完全一样、误差随机独立,完全忽略真实硬件的时空相关性和泄漏效应,用它训练的译码器在真实硬件上精度直接下降15%-25%;另一类是相干密度矩阵模型,精度极高但复杂度呈指数增长,20比特以上就无法计算,完全不具备规模化价值。

谷歌推出的SI1000、SD6模型,是当前行业公认的标杆,被广泛用于量子纠错、量子模拟研究。但即便如此,它依然只区分单操作误差,忽略比特差异、时空变化和泄漏传播,无法还原真实硬件的误差行为。

基于此,全球量子计算领域都在期待一个“高精度+低复杂度+跨平台自适应”的误差模型——既能精准描述真实硬件误差,又能支撑百比特、千比特规模化模拟,PAEMS正是为解决这一痛点而生。

精确自适应量子比特误差模型

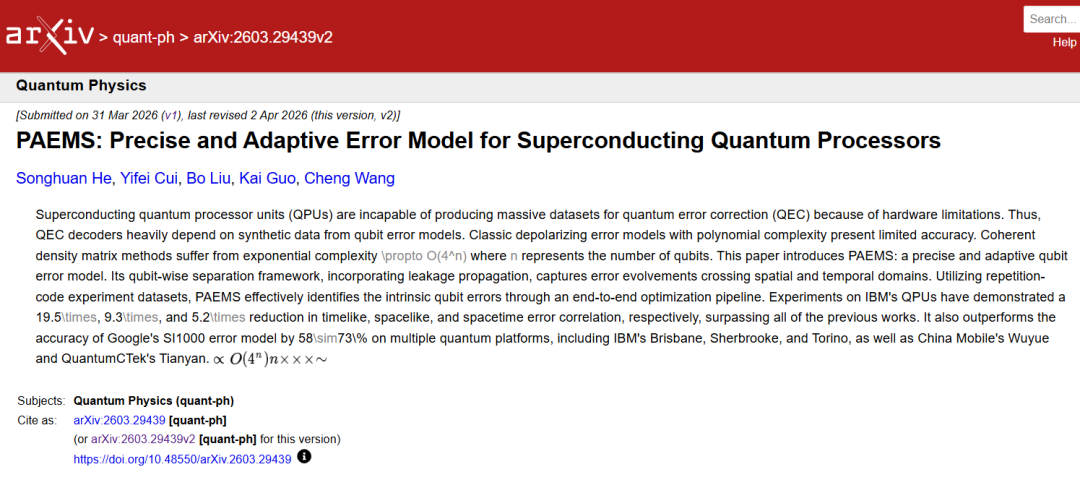

PAEMS模型全称为“精确自适应量子比特误差模型”,是面向超导量子处理器设计的电路级随机误差模型,其跳出传统模型“非精度即复杂度”的二元困境,提出了一套逐比特分离、融合泄漏传播、数据驱动优化的全新框架。

第一,采用逐量子比特分离框架,打破传统模型“全局平均、统一参数”的局限。PAEMS放弃了所有比特用同一套参数的粗暴做法,为每个量子比特、每个耦合器单独设置误差参数,精准刻画硬件固有的非均匀性。同时,它把退相干误差、门操作误差、态制备与测量误差分开建模,避免误差源重复计算,让每一个参数都对应真实的物理机制。

第二,首次在低复杂度模型中融入泄漏与渗流传播机制。超导量子比特是多能级系统,会“泄漏”到计算态之外,这种泄漏会跨轮次、跨比特传播,是传统模型完全忽略的关键误差。PAEMS专门引入泄漏概率和回渗概率,让泄漏误差在时空域中正常演化,第一次在O(n²)复杂度下实现了泄漏效应的精准模拟。

第三,端到端自适应训练,跨平台即插即用。PAEMS以硬件校准数据为初始值,用重复码实验数据集做优化,通过协方差矩阵自适应进化策略自动调整参数,不需要人工干预就能适配不同平台。这表明,它可以在IBM的超导处理器、中国移动的云端量子计算平台、国盾量子的硬件上快速部署,真正实现“一次建模,全平台通用”。

图:PAEMS量子比特误差模型框架

整套方法的最大亮点是平衡:精度追上密度矩阵模型,复杂度保持在传统随机泡利模型水平,同时具备前所未有的跨平台自适应能力,完美匹配量子纠错译码器的训练需求。

多平台验证

研究团队在国际主流与国产超导量子处理器上开展了系统性实验验证,包括IBM的Brisbane、Sherbrooke、Torino处理器,中国移动“五岳”量子计算平台,国盾量子“天衍”处理器,全面评估PAEMS的时空误差建模能力与跨平台适应性,实验结果极具说服力。

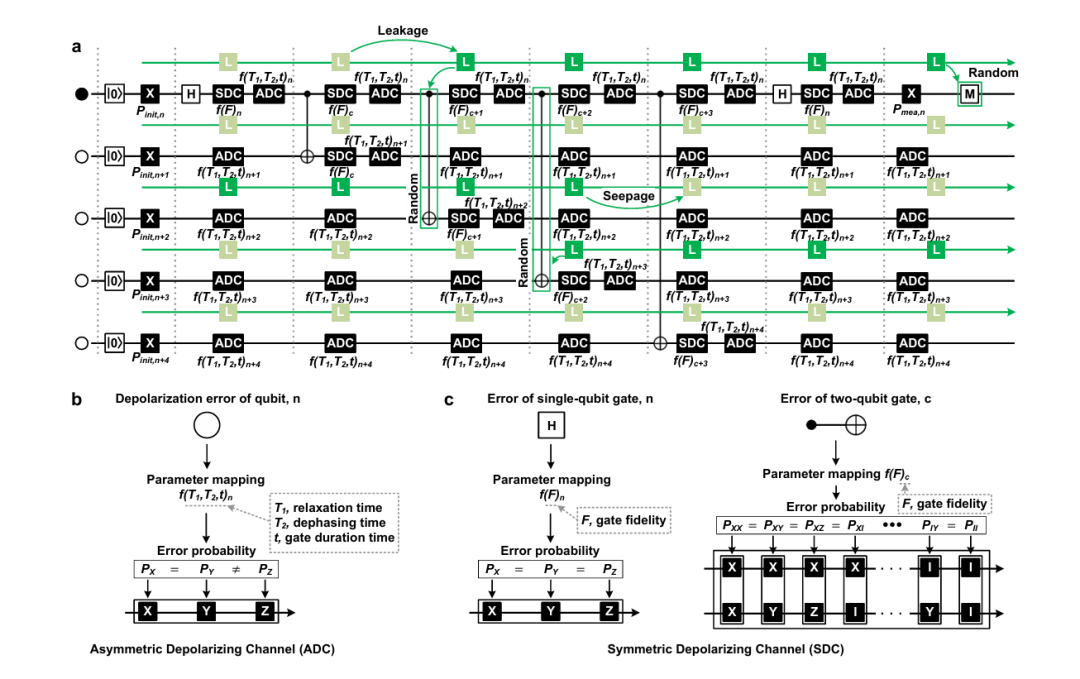

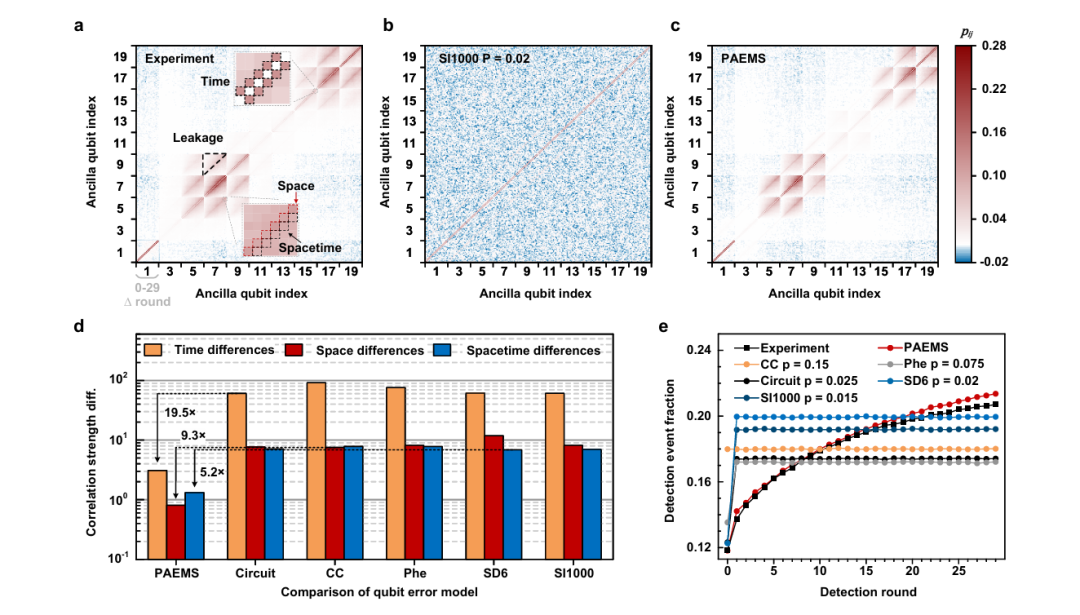

在最具说服力的“30轮重复码”实验中,PAEMS展现出压倒性优势:

-时序误差相关性偏差降低19.5倍;

-空序误差相关性偏差降低9.3倍;

-时空误差相关性偏差降低5.2倍。

图:包含21个量子比特和30个探测轮次的重复码实验

这表明,PAEMS对真实硬件误差的还原度,是传统模型的近20倍。谷歌SI1000模型模拟的误差高度均匀、没有泄漏效应,和实验数据差距极大;而PAEMS完美复现了比特差异、误差累积、泄漏相关等真实特征,检测事件占比的均方根误差仅3.4%。

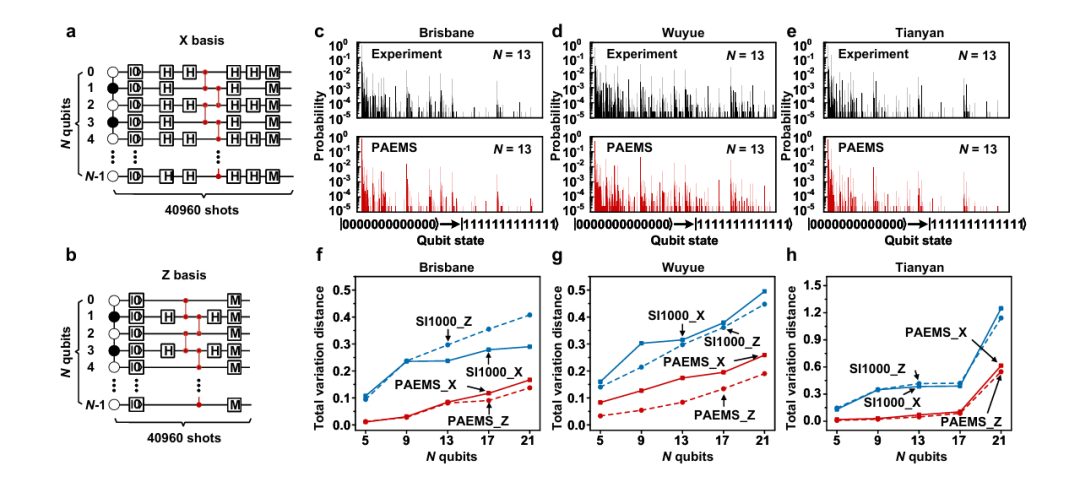

在跨平台自适应测试中,研究团队采用5-21比特单轮重复码,用总变差距离(TVD)衡量模型精度。结果显示,PAEMS在所有平台上的TVD较谷歌SI1000降低58%-73%:在IBM Brisbane上降低69.4%,中国移动“五岳”上降低58.1%,国盾量子“天衍”上降低68.9%。

图:使用单轮重复码的跨平台适应性

这组数据证明,PAEMS不是针对某一平台优化的“定制模型”,它够快速适配不同厂商、不同架构的硬件,无需大量人工调参即可保持高精度,具备极强的实用化部署能力。

两种路径的哲学碰撞

当我们将PAEMS的成就置于更广阔的视野下,一个重量级选手浮出水面,那就是英伟达(NVIDIA)。英伟达近年来凭借其在GPU和AI领域的绝对优势,高调进军量子领域,其近期也推出了全球首个开源量子人工智能模型系列——NVIDIA Ising。两者虽在技术路径上各有侧重,却共同指向了量子纠错这一关键战场,值得放在同一视野下加以审视。

PAEMS是一种面向超导量子处理器的精确、自适应误差模型,它直击当前量子纠错解码器训练的痛点——缺乏大规模、高保真的真实硬件数据集,故其重点不在“直接纠错”,而在于更真实地重建量子芯片上的噪声分布,为后续解码器训练和纠错策略提供高质量数据底座。

相比之下,NVIDIA Ising更接近产业化控制栈中的“AI执行层”。它瞄准了量子纠错与校准两大核心工程挑战。其“Ising Decoding”解码器利用神经网络,在接收到错误信号(即“症候群”)后,能比传统开源标准(pyMatching)快2.5倍、准3倍地推断出错误的类型和位置,并给出修正方案。而“Ising Calibration”则利用视觉语言模型,将过去需要数天的量子处理器校准工作自动化并缩短至数小时。

PAEMS的优势在于物理可解释性强、适配超导硬件细节、能够为不同平台生成更可信的误差样本;Ising的优势则在于开放模型生态、GPU加速、实时部署能力以及与CUDA-Q、NVQLink等英伟达软硬件体系的深度集成。

严格来说,PAEMS解决的是“误差如何被真实建模”,Ising解决的是“这些信息如何被AI高效用于校准和解码”。PAEMS所提供的更高仿真保真度,理论上可直接为Ising Decoding这类AI解码器提供更优质的训练数据,形成精准建模在前、智能解码在后的完整技术闭环。

因此,它们不是简单替代关系,更像是上下游互补。PAEMS夯实数据与物理建模基础,Ising推动AI校准、在线解码和系统级落地,共同勾勒出量子纠错从理论走向工程实践的完整图景。

从FPGA验证到ASIC专用:解码硬件正在进入专用化阶段

值得注意的是,在量子纠错解码硬件的实现路径上,国际上正逐渐形成“FPGA先行、ASIC接棒”的发展格局。

过去一年多,FPGA方案率先承担起实时解码验证与系统联调的角色。谷歌在2024年12月公布的Willow表面码实验中,已经展示了集成实时解码链路的低于阈值量子纠错;2025年12月,Riverlane在《Nature Communications》发表硬件解码工作,在FPGA上实现了面向表面码的Local Clustering Decoder,将单轮解码时间压到1微秒以内;IBM也在2025至2026年持续推进Relay-BP在AMD FPGA上的实时实现,表明FPGA正在成为当前量子纠错解码工程落地的主流验证平台。

与之相比,ASIC解码方案的公开案例虽然仍然较少,但其战略价值正在迅速上升。

2025年关于FPGA与ASIC量子纠错解码设计空间的系统研究表明,ASIC能够进一步降低延迟、提升能效,更适合未来大规模、持续在线的解码任务;与此同时,面向低温环境的Cryo-CMOS、超导数字电路等研究也在不断推进,目标正是把解码能力进一步推向靠近量子芯片的一侧,从而缓解带宽、功耗和系统时延压力。可以说,FPGA更适合当前算法快速迭代、平台适配和原型验证,而ASIC则代表着量子纠错解码走向高性能、低功耗和专用化部署的下一阶段。

在这一背景下,PAEMS的意义就不仅在于提升误差建模精度,更在于为未来解码硬件,特别是面向专用ASIC芯片的训练、验证和协同优化,提供更贴近真实超导量子处理器的高可信误差数据基础。

成果与展望

总之,PAEMS的提出,在量子纠错的软件栈中填补了一个长期被忽视的关键缺口。

从近期影响来看,PAEMS为AlphaQubit、GraphQEC等高性能神经网络解码器的训练提供了更高质量的合成数据来源,有望直接缩短“模拟-现实落差”,提升解码器在真实硬件上的部署性能。

从中期意义来看,PAEMS所建立的逐量子比特误差模型体系,本质上是一套量子处理器的“数字孪生框架。随着量子比特数量从数百迈向数千,这种精细化的设备建模能力将成为量子处理器设计、校准、优化的重要辅助工具,也为量子处理器的跨平台性能评估提供了统一的量化基准。

从长远展望来看,研究团队指出,当前版本尚未纳入相干误差和量子比特串扰等噪声机制,这是下一阶段的主要扩展方向。此外,研究团队计划将验证场景从重复码扩展至表面码和色码,并与主流QEC解码器开展联合基准测试。随着量子处理器规模持续扩张,能够精准刻画大规模量子比特阵列时空误差行为的自适应模型,将成为量子纠错工程化落地不可或缺的核心组件。

[1]https://arxiv.org/abs/2603.29439v2

[2]https://nvidianews.nvidia.com/news/nvidia-launches-ising-the-worlds-first-open-ai-models-to-accelerate-the-path-to-useful-quantum-computers

[3]https://www.nature.com/articles/s41586-024-08449-y

[4]https://www.nature.com/articles/s41467-025-66773-x

[5]https://www.ibm.com/quantum/blog/relay-bp-error-correction-decoder

[6]https://research.ibm.com/publications/improved-belief-propagation-is-sufficient-for-real-time-decoding-of-quantum-memory

[7]https://link.springer.com/article/10.1140/epjqt/s40507-025-00446-y

相关阅读

相关阅读