详解直接射频采样接收机架构:从模拟到全数字的终极突破

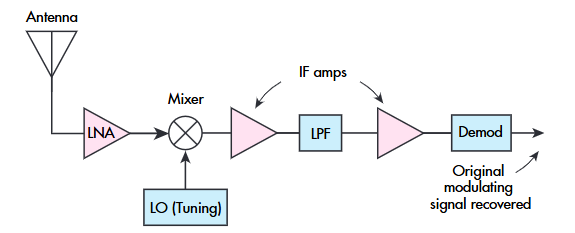

在正式展开架构讲解之前,我们先再梳理一下接收机的演进脉络,帮大家更清晰地理解射频采样接收机的定位和优势——毕竟,任何新技术的出现,都是为了解决传统技术的痛点。超外差接收机是早期射频通信的核心架构,它的核心逻辑是“分步降频”:先通过天线捕获空中的射频信号,再通过1-2次模拟混频,将高频射频信号转换为固定频率的中频信号,之后经过中频放大、滤波等模拟调理,最后通过模数转换器(ADC)将模拟中频信号转换为数字信号,交给数字模块处理。这种架构解决了“射频信号难以直接处理”的核心痛点,但代价也很明显:链路中包含混频器、本地振荡器(LO)、中频放大器等大量模拟器件,不仅导致电路板体积庞大、能耗偏高,还容易出现本振泄漏、混频干扰等问题,集成度很难提升,难以适配小型化、低功耗的应用场景,比如手机、便携式监测设备等。

超外差接收机架构

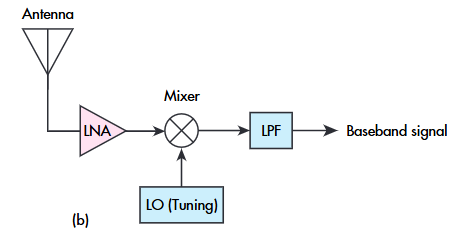

为了解决超外差接收机的痛点,零中频接收机应运而生。它最大的突破就是“取消中频环节”,直接通过模拟正交解调,将射频信号转换为基带信号,再通过ADC采样进入数字域处理。这种简化让射频电路的体积大幅缩小、能耗显著降低,集成度也得到了质的提升,完美适配了手机、智能穿戴等小型化设备的需求。但零中频接收机并没有彻底摆脱模拟链路的束缚,其模拟正交解调环节仍然存在固有缺陷:比如直流偏移(正交解调过程中产生的直流分量,会淹没有用的微弱基带信号)、I/Q通道不平衡(同相和正交两路信号的增益、相位存在差异,导致信号失真)、低频噪声干扰(模拟器件的低频噪声会叠加到基带信号中,影响信号质量),这些问题在高精度、高灵敏度的应用场景中(如雷达、卫星通信),会严重制约接收机的性能。

零中频接收机架构

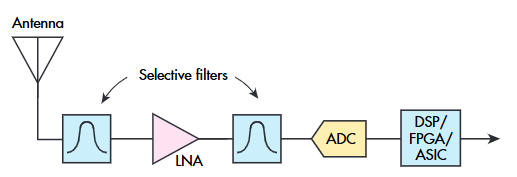

正是在这样的背景下,直接射频采样接收机(Direct RF Sampling Receiver,简称射频直采接收机)应运而生,它彻底跳出了“模拟下变频”的传统思维定式,提出了“数字化尽早”的核心设计理念——这也是它与超外差、零中频接收机最本质的区别。简单来说,射频采样接收机不再需要任何模拟混频、模拟正交解调环节,而是利用高性能的射频模数转换器(RF ADC),直接对经过前端简单调理的射频信号进行采样、量化,将模拟射频信号直接转换为数字信号,后续所有的信号处理流程,包括频率转换、滤波、解调、干扰抑制、信号提纯等,全部在数字域通过可编程逻辑器件完成。这种全数字架构,既保留了零中频接收机“链路简化、体积小、能耗低”的优势,又彻底克服了模拟链路的固有缺陷,同时还具备更高的灵活性、可扩展性和性能上限,成为射频通信领域从模拟向全数字转型的核心标杆。

这里需要特别纠正一个常见误区:很多朋友认为“射频采样就是直接对空中的射频信号进行采样”,其实不然。空中的射频信号强度极弱,通常只有微伏级甚至纳伏级,而且混杂着大量的带外干扰、电磁噪声,直接对这样的信号进行采样,会导致采样精度极低,甚至无法捕捉到有用信号。因此,射频采样接收机并非完全没有模拟环节,而是保留了必要的“射频前端预处理模块”,这个模块的核心作用是对天线捕获的微弱射频信号进行调理,提升信号质量,为后续的RF ADC采样奠定基础——其核心区别在于,前端预处理仅负责“信号调理”,不进行任何频率转换,所有频率转换和信号提纯工作,全部交给数字域完成。

射频直采收机架构

从整体架构来看,射频采样接收机主要由三大核心模块协同组成,分别是:射频前端预处理模块、射频采样核心模块(RF ADC)、数字信号处理模块。这三大模块相互依存、缺一不可,共同完成从射频信号接收、调理,到模拟转数字,再到数字信号优化处理的全流程。下面,我们分别对这三大模块进行详细拆解,讲解每个模块的组成、工作原理、核心器件和设计要点,让大家对射频采样接收机的架构有更直观、深入的理解。

No.1 射频前端预处理模块:采样质量的“第一道防线”

射频前端预处理模块是射频采样接收机的“信号入口”,其性能直接决定了后续RF ADC采样的质量,进而影响整个接收机的灵敏度、抗干扰能力和信号保真度。如果前端预处理不到位,有用信号被噪声或干扰淹没,即便后续的RF ADC性能再强、数字处理算法再先进,也无法还原出有用信号。简单来说,这个模块的核心任务就是“给RF ADC提供干净、稳定、幅度合适的射频信号”。

射频前端预处理模块的组成并不复杂,主要包括天线接口、阻抗匹配网络、低噪声放大器(LNA)、射频带通滤波器(RF BPF),部分高端场景还会增加可变增益放大器(VGA)、直流阻断电路和抗干扰电路,下面我们逐一讲解每个组件的作用、核心参数和设计要点。

1.1 天线接口与阻抗匹配网络

天线是射频信号的“捕获器”,负责将空中的电磁波转换为微弱的模拟射频电流信号,而天线接口则是天线与接收机前端的连接桥梁,通常采用SMA、N型等射频专用连接器,核心要求是“低损耗、高匹配”。射频系统的标准阻抗通常为50Ω,若天线接口与前端电路的阻抗不匹配,会导致信号反射,不仅会造成信号损耗,还会引入干扰,影响后续信号调理和采样效果。

阻抗匹配网络通常位于天线接口与低噪声放大器之间,核心作用是实现天线与LNA输入阻抗的精准匹配,减少信号反射,最大限度地将天线捕获的射频信号传输到LNA。常见的阻抗匹配方式包括:串联/并联电阻、电容、电感组成的无源匹配网络,以及微带线匹配结构(适用于高频场景)。在实际设计中,需要根据天线的阻抗特性、LNA的输入阻抗,结合接收机的目标工作频段,通过ADS、HFSS等射频仿真工具进行优化,确保在目标频段内的匹配度满足要求,通常要求反射系数(S11)<-15dB,确保信号传输效率最大化。

此外,部分场景下还会在天线接口后增加直流阻断电容,用于隔离天线与前端电路之间的直流分量,避免直流信号损坏LNA等敏感器件,同时防止直流分量叠加到射频信号中,影响后续的信号调理和采样精度。

1.2 射频带通滤波器(RF BPF):干扰信号的“过滤器”

天线捕获的射频信号中,除了我们需要的有用信号外,还包含大量的带外干扰信号——比如其他通信系统的射频信号、工业设备产生的电磁干扰、环境中的杂散噪声等,这些干扰信号如果进入后续的RF ADC,会导致采样失真,影响数字信号处理的效果,甚至会直接淹没有用信号。因此,需要通过射频带通滤波器(RF BPF)对信号进行滤波,只允许目标频段内的有用信号通过,滤除带外的干扰和噪声。

对于射频采样接收机而言,带通滤波器的设计有两个核心要点:一是带宽匹配,滤波器的通带需要严格匹配接收机的目标工作频段,通带内的插入损耗尽可能小(通常要求插入损耗<1dB),确保有用信号能够顺利通过,不会产生过多损耗;二是阻带衰减足够大(通常要求阻带衰减≥40dB),能够有效抑制带外干扰,尤其是靠近通带的干扰信号,避免其进入ADC后影响采样精度。

常见的射频带通滤波器包括声表面波滤波器(SAW)、体声波滤波器(BAW)、微带线滤波器等,不同类型的滤波器适用于不同的场景:SAW滤波器成本低、体积小,适合中低频段(如2GHz以下)的应用,比如手机通信、便携式监测设备;BAW滤波器的高频特性更好、阻带衰减更大,适合高频段(如2GHz以上)和高性能场景,比如5G毫米波、雷达系统;微带线滤波器则适合高频段、宽频带的应用,可通过PCB布局实现,灵活性高,但体积相对较大,适合设备体积要求不严格的场景,比如基站、雷达站。

1.3 低噪声放大器(LNA):微弱信号的“放大器”

天线捕获的射频信号通常非常微弱,幅度仅为微伏级甚至纳伏级,而RF ADC需要一定幅度的模拟信号才能进行有效量化,因此必须通过低噪声放大器(LNA)对其进行放大,提升信号幅度,同时尽可能降低自身引入的噪声,确保信号的信噪比(SNR)不被恶化。LNA是射频前端预处理模块中最关键的器件,其性能直接决定了整个接收机的灵敏度——灵敏度是接收机能够可靠接收的最小信号幅度,LNA的噪声系数越低、增益越高,接收机的灵敏度就越高,越能捕捉到微弱的有用信号。

对于射频采样接收机而言,LNA的设计有两个核心要求:一是低噪声系数(NF),二是高增益,同时还要具备足够的带宽和线性度。从参数来看,LNA的噪声系数通常要求在1-3dB之间(越低越好),增益通常在20-40dB之间,具体增益需要根据后续RF ADC的输入要求进行调整——既要保证放大后的信号幅度满足ADC的采样范围,又要避免信号过载(过载会导致信号失真)。此外,LNA的带宽需要完全覆盖接收机的目标工作频段,比如5G通信的Sub-6GHz频段、雷达系统的X波段(8-12GHz)等,确保在整个工作频段内,LNA的增益和噪声系数保持稳定,不会出现信号放大不均衡的情况。

在实际设计中,LNA通常采用GaAs(砷化镓)或GaN(氮化镓)工艺的晶体管制作,这类器件具备低噪声、高增益、高频特性好的优势,适合射频频段的信号放大。同时,为了进一步降低噪声,LNA的偏置电路需要设计合理,避免偏置电流过大或过小导致噪声系数恶化;此外,LNA的输出阻抗也需要与后续的带通滤波器进行阻抗匹配,减少信号反射和损耗,确保放大后的信号能够高效传输到下一级。

1.4 可变增益放大器(VGA)与增益控制

在实际应用中,天线接收的射频信号幅度会随着环境变化而波动——比如距离信号源的远近、环境干扰的强弱、信号传播过程中的衰减等,这会导致LNA输出的信号幅度不稳定。如果信号幅度过小,会导致RF ADC采样的量化误差增大,信号信噪比降低,甚至无法还原有用信号;如果信号幅度过大,会导致ADC过载,产生非线性失真,同样会影响信号质量。因此,部分射频采样接收机的前端会增加可变增益放大器(VGA),用于动态调整信号幅度,确保输入到RF ADC的信号幅度稳定在ADC的最佳采样范围内。

VGA的核心特点是增益可通过外部控制信号(如电压、数字信号)进行调节,调节范围通常在20-60dB之间,能够适应不同幅度的输入信号。增益控制的实现方式主要有两种:一种是模拟增益控制,通过调节VGA的偏置电压来改变增益,结构简单、成本低,适合对增益调节精度要求不高的场景;另一种是数字增益控制,通过数字信号(如SPI接口)控制VGA的增益档位,调节精度高、灵活性强,适合高精度、高稳定性的应用场景,比如雷达、卫星通信。

此外,增益控制通常与自动增益控制(AGC)电路配合使用——AGC电路通过检测RF ADC输出的数字信号幅度,自动调节VGA的增益,形成闭环控制,确保输入到ADC的信号幅度始终稳定在最佳范围,无需人工干预。这种设计尤其适合信号幅度波动较大的场景,比如移动通信、雷达探测、射频监测等,能够大幅提升接收机的适应性和稳定性。

1.5 前端预处理模块的设计注意事项

除了上述组件的设计,射频前端预处理模块的整体布局和电磁兼容(EMC)设计也非常重要。由于射频信号频率高、幅度弱,容易受到外界电磁干扰和内部电路的干扰,因此在布局时,需要将LNA、带通滤波器等敏感器件远离数字电路(如FPGA、DSP),避免数字电路的开关噪声干扰射频信号;同时,射频链路的布线要尽量短、粗,减少信号损耗和干扰;此外,还需要做好接地处理,确保接地良好,降低接地噪声,避免噪声叠加到射频信号中。

另外,前端预处理模块的带宽需要与后续的RF ADC带宽相匹配——如果前端带宽过窄,会导致有用信号被滤除,影响接收机的接收范围;如果前端带宽过宽,会引入更多的带外干扰,增加ADC的采样压力,甚至导致采样失真。因此,在设计时,需要根据接收机的目标工作频段、RF ADC的采样率和带宽,合理设计前端预处理模块的带宽,实现性能与成本的平衡。

No.2 射频采样核心模块:RF ADC——模拟与数字的“桥梁”

如果说射频前端预处理模块是射频采样接收机的“第一道防线”,那么射频采样核心模块就是整个接收机的“核心枢纽”,而其中的射频模数转换器(RF ADC),则是连接模拟射频世界与数字信号处理领域的“桥梁”——它的核心作用是将经过前端预处理的模拟射频信号,通过采样、量化、编码,转换为数字信号,为后续的数字处理提供基础。

与传统接收机中使用的中频ADC(IF ADC)不同,RF ADC需要直接对射频频段的信号进行采样,这就对其性能提出了极高的要求——传统IF ADC的采样率通常在几十MHz到几百MHz之间,而RF ADC的采样率需要达到GHz级别,同时还要具备高分辨率、高带宽、高动态范围、低噪声等特性。可以说,RF ADC的性能直接决定了射频采样接收机的整体性能,也是射频采样技术中最核心、最具挑战性的部分。

2.1 RF ADC的基本工作原理

RF ADC的基本工作流程与传统ADC一致,均包含三个核心步骤:采样、量化、编码,但由于其采样对象是高频射频信号,因此工作频率和性能要求远高于传统ADC。

采样:采样是指按照一定的时间间隔,对连续变化的模拟射频信号进行抽取,将连续的模拟信号转换为离散的模拟信号(采样值)。采样的核心是遵循采样定理(奈奎斯特采样定理),即采样率(fs)必须大于等于被采样信号最高频率(fmax)的2倍,即fs≥2fmax,这样才能确保离散的采样值能够完整还原出原始的连续模拟信号,避免出现混叠失真。

量化:量化是指将离散的模拟采样值,映射到有限个离散的电平值(量化电平)上,实现幅度上的离散化。由于模拟信号的幅度是连续的,而量化电平是离散的,因此量化过程会产生量化误差,量化误差的大小与ADC的分辨率(位数)相关——分辨率越高,量化电平的数量越多(量化电平数=2^分辨率位数),量化误差越小,信号的保真度越高。

编码:编码是指将量化后的离散电平值,转换为二进制数字代码(如8位、12位、14位二进制数),输出数字信号,供后续的数字信号处理模块使用。编码的方式通常有二进制编码、格雷码编码等,其中二进制编码是最常用的方式,能够快速实现数字信号的传输和处理。

需要注意的是,RF ADC的采样对象是射频频段的模拟信号(通常为几百MHz到几十GHz),因此其采样率必须足够高——例如,对于最高频率为5GHz的射频信号,根据奈奎斯特采样定理,采样率至少需要达到10GHz;而实际应用中,为了预留滤波余量,避免混叠失真,采样率通常会选择为信号最高频率的2.5-3倍,即12.5-15GHz。这就对RF ADC的采样速度提出了极高的要求,也是RF ADC与传统IF ADC的核心区别之一。

2.2 RF ADC的核心性能参数

对于射频采样接收机而言,RF ADC的性能参数直接决定了采样质量和后续数字处理的效果,核心性能参数主要包括采样率、分辨率、带宽、动态范围、噪声性能、时钟抖动等,各参数之间相互制约,需要根据应用场景进行权衡设计。

2.2.1 采样率(Sampling Rate)

采样率是指RF ADC单位时间内完成的采样次数,单位为每秒采样点数(SPS),通常用GSPS(吉采样/秒)表示(1GSPS=10^9 SPS)。采样率是决定RF ADC可处理信号最高频率的核心指标,采样率越高,可处理的信号频率越高,同时也能更好地避免混叠失真。

目前,主流商用RF ADC的采样率已达到2.6-3 GSPS(如TI ADC32RF5x系列),高端产品可实现单通道10.4 GSPS、四通道40 GSPS的超高采样率(如成都华微4通道ADC芯片),支持高达19-20 GHz的输入信号带宽,能够覆盖Ku/Ka波段、汽车雷达77 GHz频段、5G 28/60 GHz毫米波频段等主流应用场景(注:77GHz汽车雷达信号需通过前端调理配合欠采样技术适配,RF ADC本身输入带宽通常不直接覆盖77GHz)。

需要注意的是,采样率的提升会带来两个问题:一是功耗增加(采样率越高,ADC的功耗越大),二是数据量增大(采样率越高,单位时间内输出的数字信号越多),这会对后续的数字信号处理模块和数据传输链路提出更高的要求。因此,在设计时,需要根据接收机的目标工作频段,合理选择采样率,避免盲目追求高采样率而导致功耗和成本的浪费。

2.2.2 分辨率(Resolution)

分辨率以位数(Bit)表示,指RF ADC能够区分的最小信号幅度变化,直接影响器件的动态范围和信噪比(SNR)。分辨率越高,量化电平的数量越多(量化电平数=2^分辨率位数),量化误差越小,对微弱信号的识别能力越强,但通常会牺牲采样率和增加功耗——这是RF ADC设计中典型的“精度与速度”的权衡。

RF ADC的分辨率常见为8-16位,其中12-14位是兼顾精度与速度的主流选择:8位分辨率的RF ADC采样率高、功耗低,但量化误差大,适合对信号保真度要求不高的场景(如简单的射频监测、短距离通信);12-14位分辨率的RF ADC能够兼顾采样率和精度,适合大多数射频通信、雷达探测、卫星通信场景;16位及以上分辨率的RF ADC精度高、量化误差小,但采样率较低、功耗较大,适合对信号保真度要求极高的场景(如射电天文、高精度测量、军用电子对抗)。

例如,TI的ADC32RF5x系列RF ADC为14位分辨率,采样率可达3GSPS,能够满足5G Massive MIMO、雷达等场景的需求;成都华微的超高速ADC为12位分辨率,采样率可达10.4GSPS,适合高频段、高带宽的应用场景;臻镭科技的军用RF ADC可达14位分辨率,具备高可靠性和抗干扰能力,适合军用雷达、电子对抗等场景(注:不同厂商产品参数以官方规格书为准,此处为主流典型参数)。

2.2.3 带宽(Bandwidth)

带宽(通常指输入带宽)是指RF ADC能够有效处理的射频信号频率范围,单位为GHz,是决定器件适配频段的关键指标。RF ADC的输入带宽需要覆盖接收机的目标工作频段,确保能够对目标频段内的射频信号进行有效采样,否则会导致有用信号无法被捕捉或采样失真。

随着5G毫米波、卫星互联网、雷达等技术的发展,对RF ADC的带宽需求不断提升。目前,主流商用RF ADC的输入带宽已达3-10 GHz,高端产品可突破20 GHz,能够覆盖Sub-6GHz、毫米波等主流频段。例如,Xilinx的RFSoC系列芯片中集成的RF ADC,输入带宽可达7.125GHz,能够直接对C带(4-8GHz)的射频信号进行采样,无需模拟下变频环节,大幅简化了接收机设计。

需要注意的是,RF ADC的带宽与采样率密切相关——采样率越高,带宽通常也越大,但两者并非完全成正比,还与ADC的架构设计有关。因此,在选择RF ADC时,需要同时考虑采样率和带宽,确保其能够满足目标应用的需求。

2.2.4 动态范围与失真性能

动态范围(Dynamic Range)表示RF ADC能够同时处理的最强信号与最弱信号的幅度比值,单位为dB,直接反映器件对复杂信号环境的适应能力——动态范围越大,RF ADC能够同时处理的信号幅度范围越广,既能捕捉到微弱的有用信号,又能避免强信号导致的过载失真。

动态范围的核心衍生指标包括:

信噪比(SNR):输出信号功率与噪声功率的比值,反映信号的纯净度,SNR越高,信号质量越好,通常要求SNR≥60dB(12位ADC)、SNR≥70dB(14位ADC)。SNR主要受量化噪声、热噪声、时钟抖动等因素影响。

无杂散动态范围(SFDR):最强信号与最强杂散信号的幅度比值,反映ADC对杂散干扰的抑制能力,SFDR越高,杂散干扰越小,通常要求SFDR≥70dBc(dBc表示相对于载波的分贝数)。杂散信号主要来源于ADC的非线性失真,如谐波失真、互调失真等。

总谐波失真(THD):所有谐波信号的总功率与基波信号功率的比值,反映ADC的非线性失真程度,THD越低,信号失真越小,通常要求THD≤-60dB。

对于射频采样接收机而言,动态范围和失真性能至关重要——因为射频信号中往往包含微弱的有用信号和较强的干扰信号,只有具备足够大的动态范围和良好的失真性能,才能确保ADC能够准确采样有用信号,同时避免强干扰信号导致的失真。

2.2.5 时钟抖动(Clock Jitter)

时钟抖动是指RF ADC采样时钟的时序不稳定,导致采样时刻出现偏差,进而影响采样精度和信噪比。时钟抖动是RF ADC的重要性能指标之一,尤其是在高采样率场景下,时钟抖动的影响会更加明显——时钟抖动越大,采样时刻的偏差越大,量化误差越大,SNR越低。

RF ADC的时钟抖动通常用均方根(RMS)表示,单位为ps(皮秒),主流RF ADC的时钟抖动通常在10-50ps之间,高端产品可达到10ps以下。时钟抖动的来源主要包括时钟源本身的抖动、电源噪声、电磁干扰等,因此,在设计RF ADC的时钟电路时,需要选择低抖动的时钟源(如晶振、锁相环PLL),同时做好电源滤波和电磁屏蔽,减少时钟抖动的影响。

2.3 RF ADC的常见类型与架构

根据架构设计的不同,RF ADC主要分为以下几种常见类型,每种类型都有其独特的优势和适用场景,可根据接收机的性能需求、成本预算进行选择。

2.3.1 流水线型ADC(Pipeline ADC)

流水线型ADC是目前RF ADC中最常用的类型之一,其核心特点是采用多级流水线结构,每一级负责对信号进行部分量化,然后将剩余的量化误差传递到下一级进行处理,最终通过多级协同实现高精度、高采样率的转换。

流水线型ADC的优势是采样率高、分辨率高、带宽大,能够兼顾精度和速度,适合大多数射频采样场景(如5G、雷达、卫星通信等);其不足是功耗相对较大,电路复杂度较高,成本也相对较高。目前,主流的12-14位、采样率2-5GSPS的RF ADC,大多采用流水线型架构。

2.3.2 折叠插值型ADC(Folding-Interpolating ADC)

折叠插值型ADC通过折叠电路将输入信号的幅度范围折叠到较小的区间,再通过插值电路提高分辨率,其核心优势是采样率高、带宽大,适合高频段、高采样率的应用场景(如毫米波雷达、电子对抗等)。

折叠插值型ADC的不足是分辨率相对较低(通常为8-12位),非线性失真相对较大,SNR和SFDR性能不如流水线型ADC。因此,这种类型的RF ADC主要用于对分辨率要求不高,但对采样率和带宽要求较高的场景。

2.3.3 sigma-delta型ADC(Σ-Δ ADC)

sigma-delta型ADC采用过采样和噪声整形技术,通过提高采样率(远高于奈奎斯特采样率),将量化噪声转移到高频段,再通过数字滤波滤除高频噪声,从而实现高分辨率的转换。

sigma-delta型ADC的优势是分辨率高(通常为16位及以上),量化误差小,SNR高,适合对信号保真度要求极高的场景(如射电天文、高精度测量等);其不足是采样率相对较低(通常在1GSPS以下),带宽较小,不适合高频段、高带宽的应用场景。

2.3.4 时间交织型ADC(Time-Interleaved ADC)

时间交织型ADC由多个低采样率的ADC并行工作,通过时间交错的方式,将采样率提升到单个ADC的N倍(N为并行ADC的数量)。例如,4个采样率为2.5GSPS的ADC,通过时间交织可以实现10GSPS的总采样率。

时间交织型ADC的优势是采样率极高,能够满足高频段、高带宽的应用需求(如毫米波通信、高端雷达等);其不足是需要多个ADC协同工作,电路复杂度高,且容易出现通道失配(如增益失配、相位失配),导致SNR和SFDR性能恶化,需要通过复杂的校准算法进行补偿。

2.4 采样定理在射频采样中的实际应用

我们在前面提到,RF ADC的采样需要遵循奈奎斯特采样定理,即采样率fs≥2fmax。但在实际应用中,对于高频射频信号(如5GHz以上),要实现fs≥2fmax,需要RF ADC具备极高的采样率,这不仅会增加ADC的设计难度和成本,还会导致功耗和数据量大幅增加。因此,在射频采样中,通常会采用“欠采样(亚奈奎斯特采样)”技术,在不降低采样质量的前提下,降低对RF ADC采样率的要求。

欠采样技术的核心原理是:故意让采样率fs低于信号最高频率fmax,但通过合理设计带通滤波器,将目标射频信号与其他频段的信号隔离,利用信号的混叠效应,将目标射频信号折叠到第一奈奎斯特区(0-fs/2),从而以较低的采样率实现对高频信号的采集。

例如,要采集中心频率为5GHz、带宽为1GHz的射频信号,若采用理想奈奎斯特采样,采样率至少需要达到12GHz(信号最高频率为5.5GHz,fs≥2×5.5GHz=11GHz,预留余量后通常取12GHz);而采用欠采样技术,选择采样率为4GHz,此时第一奈奎斯特区为0-2GHz,目标信号通过混叠效应,会折叠到1-2GHz的区间(5GHz - 2×2GHz = 1GHz),再通过数字滤波将折叠后的信号提取出来,即可实现对目标信号的采样,大幅降低了对RF ADC采样率的要求。

需要注意的是,欠采样技术的关键是精准控制混叠频率,通过设计高性能带通滤波器将目标频段信号与其他频段信号隔离,确保仅目标信号折叠至有效采样区间,避免混叠干扰。如果带通滤波器的性能不足,其他频段的干扰信号也会折叠到第一奈奎斯特区,导致采样失真。因此,欠采样技术通常需要与高性能的射频带通滤波器配合使用,才能确保采样质量。

No.3 数字信号处理模块:全数字架构的“灵魂”

RF ADC输出的数字信号,还需要经过一系列数字信号处理,才能转换为可直接用于后续应用的基带信号——比如通信系统中的解调信号、雷达系统中的目标检测信号、监测系统中的信号分析结果等。数字信号处理模块是射频采样接收机“全数字处理”的核心载体,也是其区别于传统接收机的关键所在,其核心作用是通过可编程算法,实现信号的频率转换、滤波、解调、干扰抑制、校准补偿等功能,弥补模拟环节的不足,提升信号质量。

与传统接收机的数字处理模块相比,射频采样接收机的数字处理模块需要处理更高速率的数字信号(通常为GHz级采样率对应的数字信号),因此对处理能力和实时性提出了极高的要求。目前,射频采样接收机的数字信号处理模块主要采用“FPGA+DSP”的异构计算架构,或集成了ADC/DAC、FPGA与处理器的RFSoC(射频系统级芯片),其中FPGA负责实时并行信号处理(如数字滤波、数字下变频),DSP负责算法调度、复杂信号解调(如QPSK、QAM解调)和系统控制,兼顾处理速度和灵活性。

3.1 数字信号处理模块的核心功能

射频采样接收机的数字信号处理模块,核心功能包括数字下变频(DDC)、数控振荡器(NCO)、数字滤波、正交解调、信号解调、干扰抑制、校准补偿等,各功能模块协同工作,实现对ADC输出数字信号的全方位处理和优化。

3.1.1 数字下变频(DDC):数字域的“频率转换”

RF ADC直接对射频信号进行采样后,输出的数字信号频率仍然较高(通常为GHz级),而后续的信号解调、分析等处理,通常需要在基带频率(0Hz附近)进行,因此需要通过数字下变频(DDC),将高频数字信号转换为基带数字信号。

数字下变频的核心原理是:将ADC输出的数字信号,与数控振荡器(NCO)产生的数字本振信号进行混频运算,通过频率叠加与抵消,将目标信号的频率降低到基带范围。与传统模拟下变频不同,数字下变频是在数字域进行的,没有模拟混频器带来的非线性失真、本振泄漏等问题,且频率转换的精度更高、灵活性更强——通过调整NCO的输出频率,可以灵活调整下变频的目标频率,适配不同频段的信号处理需求。

数字下变频的具体流程通常包括三个步骤:

混频:将ADC输出的数字信号(设为x(n))与NCO产生的数字本振信号(设为cos(ω0n)和sin(ω0n))进行混频,得到同相(I)和正交(Q)两路信号,即I(n)=x(n)×cos(ω0n),Q(n)=x(n)×sin(ω0n)。

低通滤波:混频后的信号中,除了基带信号外,还包含高频杂散信号,需要通过数字低通滤波器,滤除高频杂散信号,保留基带信号。

抽取:由于ADC的采样率较高,下变频后的基带信号仍然包含大量的冗余数据,需要通过抽取技术,降低信号的采样率(即减少采样点数),减少后续处理的数据量,降低DSP的处理压力。抽取的过程通常与低通滤波配合使用,避免抽取过程中出现混叠失真。

数字下变频是数字信号处理模块的核心功能之一,其性能直接决定了基带信号的质量——混频精度越高、低通滤波的阻带衰减越大、抽取后的采样率越合理,基带信号的信噪比和保真度就越高。

3.1.2 数控振荡器(NCO):数字本振的“发生器”

数控振荡器(NCO)是数字下变频的核心器件,其核心作用是产生高精度、高稳定性的数字本振信号(正弦波和余弦波),为数字混频提供频率基准。与传统模拟本地振荡器(LO)相比,NCO具有以下优势:

频率精度高:NCO的输出频率由数字控制字决定,精度可达Hz级甚至mHz级,远高于模拟LO。

频率切换快:通过改变数字控制字,可以快速切换NCO的输出频率,切换时间通常为ns级,适合多频段、多制式的信号处理场景。

稳定性好:NCO的输出频率不受温度、电压等环境因素的影响,稳定性远高于模拟LO。

灵活性强:可以通过软件配置,灵活调整输出频率、相位、幅度,适配不同的数字下变频需求。

NCO的工作原理是通过数字累加器和查找表(LUT)实现的:数字累加器根据输入的频率控制字,不断累加,产生相位码;查找表根据相位码,输出对应的正弦波和余弦波数字信号。NCO的输出频率由频率控制字和系统时钟频率决定,计算公式为:f0 = (FCW / 2^N) × fclk,其中FCW为频率控制字,N为累加器的位数,fclk为NCO的系统时钟频率(注:NCO系统时钟通常与ADC采样时钟同源或同步,确保采样与混频时序一致)。

在射频采样接收机中,NCO通常集成在FPGA或RFSoC中,其位数通常为32位或64位,确保输出频率的精度和分辨率。同时,NCO还可以与锁相环(PLL)配合使用,进一步提升输出频率的稳定性和精度。

3.1.3 数字滤波:数字域的“干扰过滤器”

数字滤波是数字信号处理模块的核心功能之一,其核心作用是滤除数字信号中的杂散干扰、噪声,提升信号的信噪比,确保后续处理的准确性。与传统模拟滤波相比,数字滤波具有以下优势:滤波特性稳定(不受温度、电压等环境因素影响)、滤波精度高、灵活性强(可通过软件配置调整滤波参数)、无插入损耗等。

在射频采样接收机的数字信号处理中,常用的数字滤波器主要包括以下几种:

低通滤波器(LPF):主要用于数字下变频后的信号处理,滤除混频产生的高频杂散信号,保留基带信号。低通滤波器的核心参数包括截止频率、阻带衰减、通带波纹等,通常要求截止频率与基带信号的带宽匹配,阻带衰减≥40dB,通带波纹≤0.1dB。

带通滤波器(BPF):主要用于滤除基带信号中的带外干扰,尤其是当基带信号中包含多个频段的信号时,通过带通滤波器可以提取出目标频段的信号。

梳状滤波器(Comb Filter):主要用于滤除工频干扰(如50Hz、60Hz)和其谐波干扰,通常用于射频监测、医疗设备等场景。

自适应滤波器:能够根据输入信号的变化,自动调整滤波参数,适应不同的干扰环境,主要用于复杂电磁环境下的干扰抑制(如移动通信、电子对抗等场景)。自适应滤波器的核心算法包括最小均方误差(LMS)算法、递归最小二乘(RLS)算法等。

数字滤波器的实现方式主要有两种:一种是基于FPGA的硬件实现(如FIR滤波器、IIR滤波器),具备处理速度快、实时性强的优势,适合高频、高速数字信号的滤波;另一种是基于DSP的软件实现,具备灵活性强、可扩展性好的优势,适合复杂滤波算法的实现(如自适应滤波)。在实际设计中,通常会结合两种实现方式,兼顾处理速度和灵活性。

3.1.4 正交解调与信号解调:还原有用信息

经过数字下变频和数字滤波后,得到的是基带I/Q信号(同相信号和正交信号),而有用信息通常调制在基带I/Q信号中(如数字通信中的QPSK、QAM调制,模拟通信中的AM、FM调制),因此需要通过正交解调与信号解调,还原出原始的有用信息。

正交解调的核心作用是将基带I/Q信号分离,提取出调制在信号中的幅度、相位信息,为后续的信号解调奠定基础。对于数字通信信号,正交解调后,还需要通过信号解调算法,还原出原始的数字基带信号(如二进制代码);对于模拟通信信号,正交解调后,需要通过解调算法,还原出原始的模拟信号(如语音、图像信号)。

常见的信号解调算法包括:

数字调制解调:适用于数字通信信号,如QPSK(四相相移键控)、QAM(正交振幅调制)、FSK(频移键控)等,核心算法包括载波同步、位同步、判决解调等。例如,QPSK解调的核心是通过载波同步提取出载波信号,然后对I/Q信号进行判决,还原出原始的数字信号。

模拟调制解调:适用于模拟通信信号,如AM(调幅)、FM(调频)等,核心算法包括包络检波、频率检波等。例如,AM解调通过包络检波提取出信号的幅度变化,还原出原始的模拟信号;FM解调通过频率检波提取出信号的频率变化,还原出原始的模拟信号。

信号解调的精度直接决定了接收机的通信质量——解调算法越先进,还原出的有用信息越准确,误码率越低。在射频采样接收机中,信号解调通常由DSP或RFSoC中的处理器实现,通过软件算法完成解调过程,具备灵活性强、可适配多种调制方式的优势。

3.2 数字信号处理模块的核心器件

射频采样接收机的数字信号处理模块,核心器件主要包括FPGA、DSP和RFSoC,三者各有优势,通常根据应用场景的需求,选择合适的器件组合。

3.2.1 FPGA(现场可编程门阵列)

FPGA是数字信号处理模块的核心硬件载体,其核心优势是并行处理能力强、处理速度快、实时性高,适合处理高频、高速的数字信号(如GHz级采样率的数字信号)。FPGA的内部包含大量的可编程逻辑单元(LE)、触发器、乘法器、加法器等,能够通过硬件编程,实现数字下变频、数字滤波、NCO等实时性要求高的功能。

在射频采样接收机中,FPGA主要负责:数字下变频(DDC)、数控振荡器(NCO)、数字滤波、I/Q通道校准、高速数据传输等实时并行处理任务。目前,主流的FPGA厂商包括Xilinx(赛灵思)、Intel(阿尔特拉)等,其高端FPGA产品(如Xilinx的UltraScale+系列、Intel的Arria 10系列),具备极高的逻辑密度和并行处理能力,能够满足射频采样接收机的高性能需求。

3.2.2 DSP(数字信号处理器)

DSP是专门用于数字信号处理的处理器,其核心优势是具备高效的数字信号处理指令集(如乘法-累加指令MAC),适合处理复杂的数字信号处理算法(如信号解调、自适应干扰抑制、校准补偿等)。与FPGA相比,DSP的串行处理能力强,灵活性高,适合处理需要复杂算法的任务,但实时性和并行处理能力不如FPGA。

在射频采样接收机中,DSP主要负责:信号解调、干扰抑制算法实现、系统控制、数据处理与输出等任务。目前,主流的DSP厂商包括TI(德州仪器)、ADI(亚德诺)等,其高端DSP产品(如TI的TMS320C6000系列、ADI的Blackfin系列),具备强大的数字信号处理能力,能够满足复杂算法的处理需求。

3.2.3 RFSoC(射频系统级芯片)

RFSoC是近年来发展起来的一种高度集成化芯片,其核心特点是将RF ADC、RF DAC、FPGA、DSP、处理器(如ARM)等功能模块集成在单芯片上,实现了从射频采样到数字处理的全链路集成。RFSoC的出现,大幅简化了射频采样接收机的硬件设计,降低了系统体积、重量和功耗,同时提升了系统的稳定性和集成度。

与“FPGA+DSP”的异构架构相比,RFSoC的优势是集成度高、体积小、功耗低、成本可控,适合小型化、低功耗的应用场景(如卫星载荷、无人平台、便携式通信设备等);其不足是灵活性相对较低,难以根据具体需求灵活调整硬件架构。目前,主流的RFSoC厂商包括Xilinx、Intel、TI等,其产品广泛应用于5G、雷达、卫星通信等领域。

No.4 射频采样接收机的优势、挑战与典型应用

4.1 核心优势

相比超外差、零中频接收机,射频采样接收机的全数字架构带来了诸多显著优势:

链路简化,集成度高:取消了模拟混频、中频放大等环节,硬件结构大幅简化,体积和重量显著降低,更容易实现小型化、集成化设计,适配便携式、嵌入式应用场景。

信号质量更优:将模拟链路的非理想因素(如直流偏移、I/Q不平衡、非线性失真)转移到数字域,通过数字算法进行补偿和优化,信号保真度更高,抗干扰能力更强。

灵活性强,可扩展性好:数字信号处理算法可通过软件编程灵活调整,无需修改硬件电路,即可适配不同频段、不同调制方式的信号处理需求,支持多制式、多场景应用。

长期稳定性好:数字器件的稳定性远高于模拟器件,受温度、电压等环境因素影响小,接收机的长期工作稳定性更高,维护成本更低。

4.2 面临的挑战

尽管射频采样接收机优势显著,但目前仍面临一些技术挑战:

RF ADC性能要求高:RF ADC需要具备高采样率、高分辨率、高带宽、低噪声等特性,设计难度大、成本高,尤其是高频段、高精度场景,对RF ADC的性能要求更为苛刻。

数字处理压力大:RF ADC输出的数字信号速率极高,需要高性能的FPGA、DSP或RFSoC进行实时处理,对数字器件的处理能力和数据传输链路提出了极高要求。

电磁兼容设计难度大:高频射频信号和高速数字信号共存,容易产生电磁干扰,需要复杂的电磁屏蔽和布线设计,确保信号传输的稳定性。

4.3 典型应用场景

随着RF ADC和数字信号处理技术的不断发展,射频采样接收机已广泛应用于多个领域:

5G通信:尤其是5G Massive MIMO基站、毫米波终端,需要高带宽、高灵活性的接收机,射频采样架构能够满足多频段、多制式的信号处理需求。

雷达系统:包括军用雷达、民用雷达(如汽车毫米波雷达、气象雷达),需要高灵敏度、高实时性的信号处理,射频采样架构能够提升雷达的探测精度和抗干扰能力。

卫星通信与导航:卫星载荷、地面接收站需要小型化、低功耗、高稳定性的接收机,RFSoC集成化架构能够完美适配。

射频监测与电子对抗:需要快速适配不同频段的信号监测和干扰抑制,射频采样接收机的灵活性的优势能够得到充分发挥。

No.5 总结与未来发展趋势

直接射频采样接收机作为一种全数字架构的接收机,以“数字化尽早”为核心设计理念,彻底打破了传统接收机“模拟处理为主、数字处理为辅”的格局,既保留了零中频接收机的简化优势,又克服了模拟链路的固有缺陷,成为射频通信领域从模拟向全数字转型的核心方向。其架构主要由射频前端预处理模块、RF ADC采样模块、数字信号处理模块三大核心部分组成,三者协同工作,实现了从射频信号接收、模拟转数字到数字信号优化处理的全流程。

未来,随着RF ADC技术的不断突破(如更高采样率、更高分辨率、更低功耗)、数字信号处理算法的持续优化(如更高效的干扰抑制、更精准的校准补偿),以及RFSoC集成度的不断提升,射频采样接收机将呈现三大发展趋势:一是小型化、低功耗,适配更多便携式、嵌入式应用场景;二是高频化、宽频化,满足5G毫米波、卫星互联网、高端雷达等领域的需求;三是智能化,通过人工智能、机器学习算法,实现自适应信号处理、智能干扰抑制,进一步提升接收机的性能和适应性。

对于射频从业者而言,掌握射频采样接收机的架构原理、核心模块和设计要点,不仅能够提升自身的技术储备,还能更好地适应射频通信技术的发展趋势,为后续从事射频电路设计、软件定义无线电(SDR)开发等相关工作奠定坚实基础。

加入知识星球,获取更多资料

更多文章:

|

注释:射频学堂原创或者转载的内容,其版权皆归原作者所有,其观点仅代表作者个人,射频学堂仅用于知识分享。如需转载或者引用,请与原作者联系。

转载/推广/ 宣传/招聘/加群...... 如果您需要我,就加 VX:RF_Centered