Y12T98 UCdavis:硅光芯片3D封装焊点寄生电容对灵敏度的影响

发布时间:2026-04-08来源:光通信女人

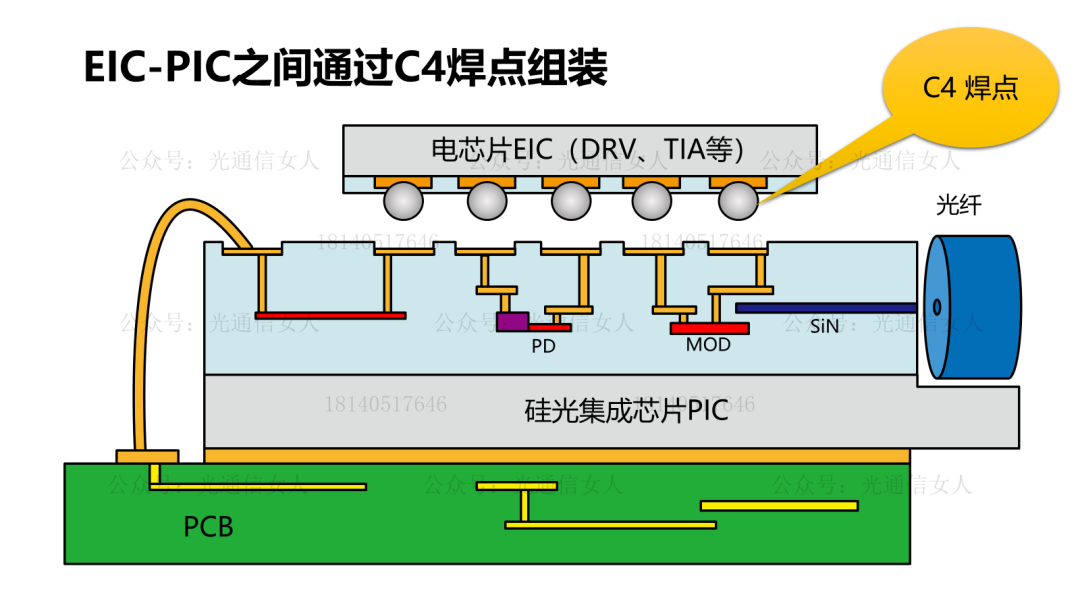

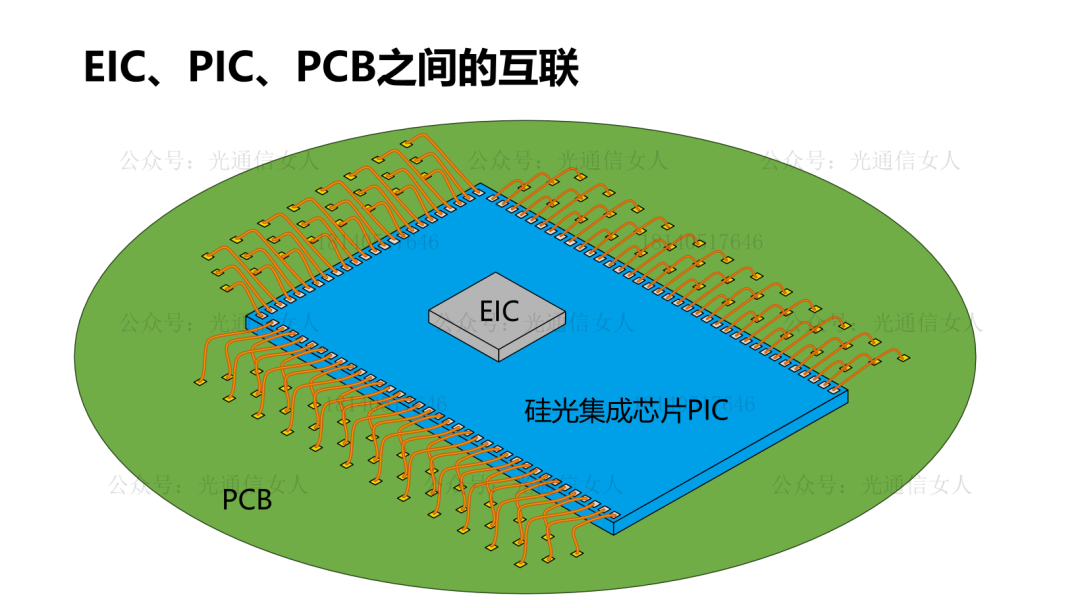

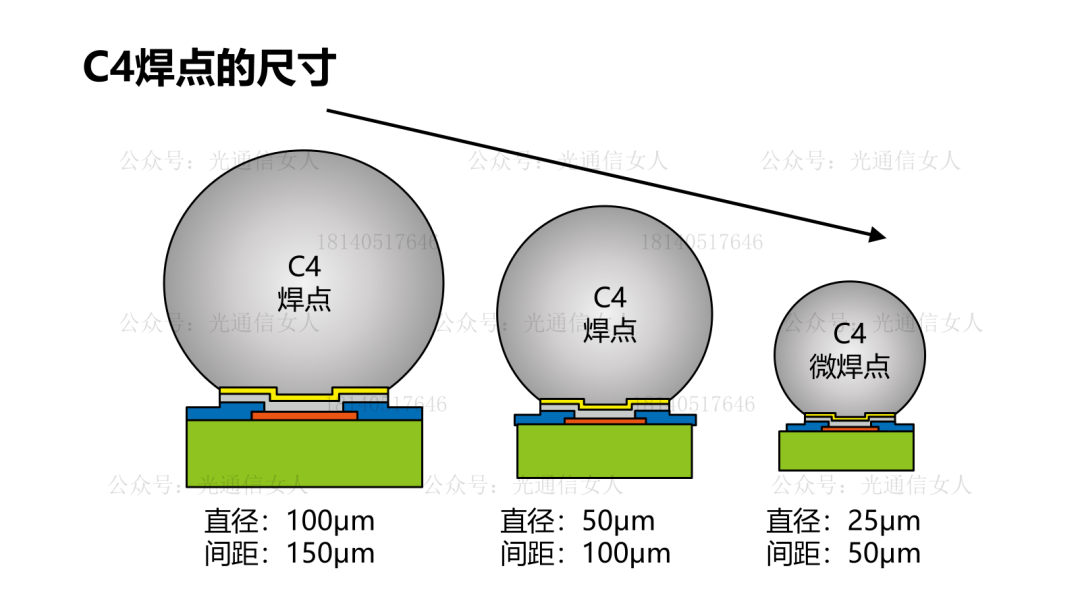

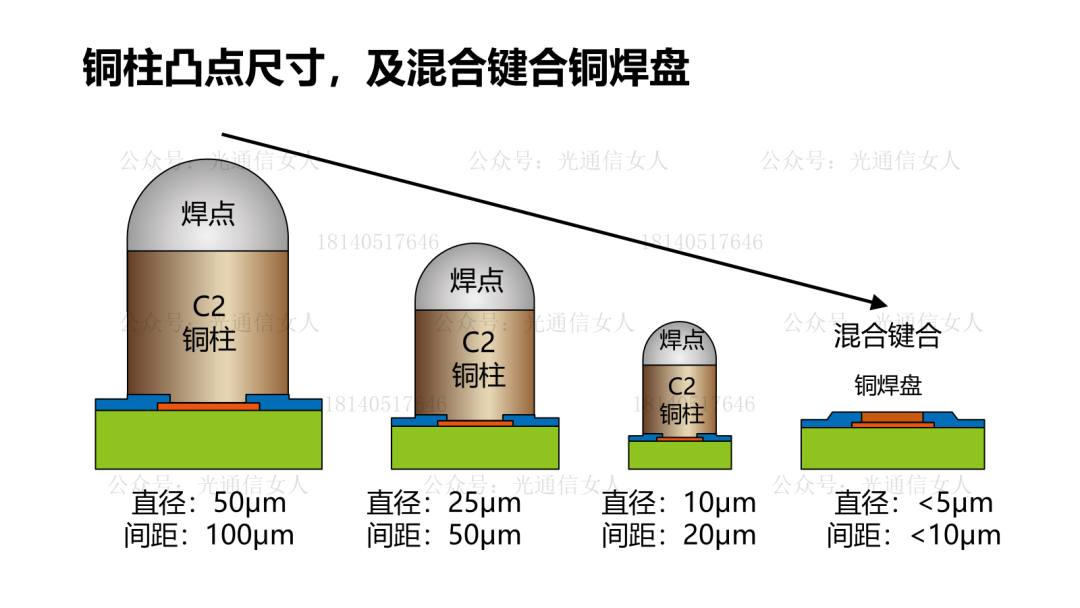

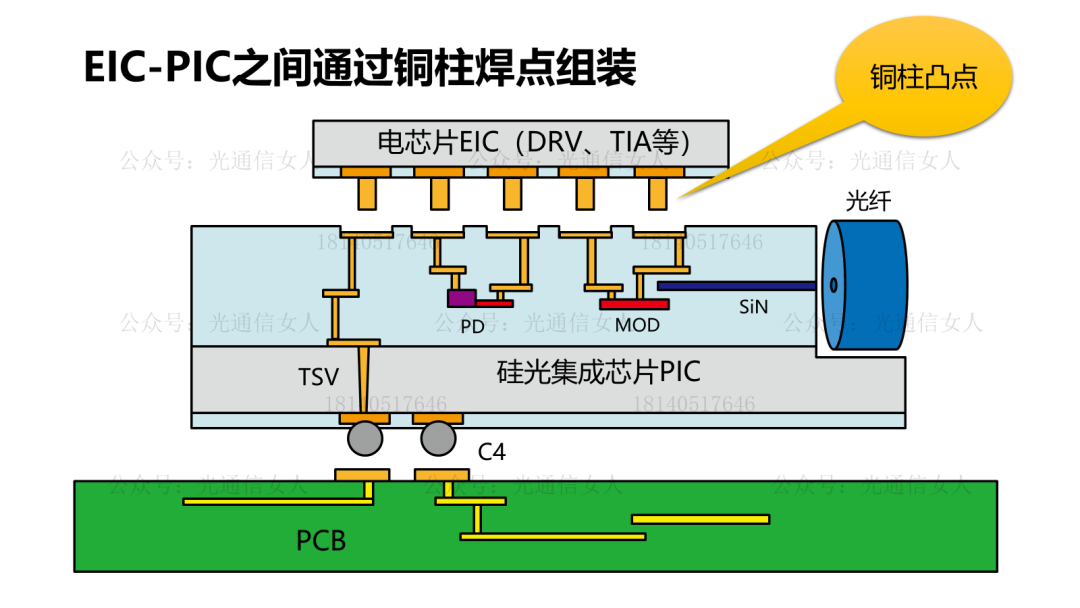

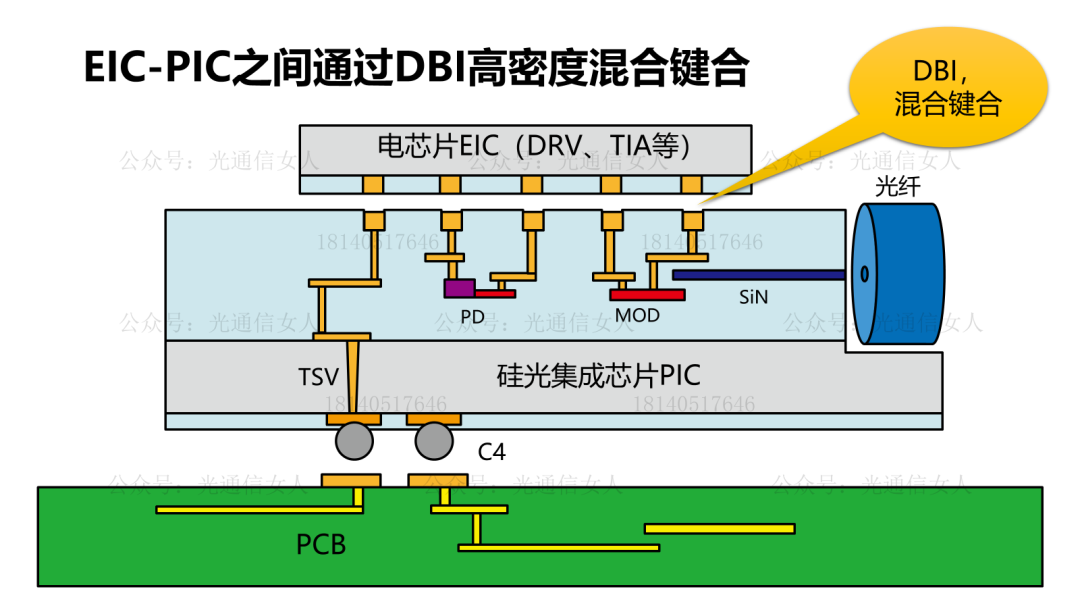

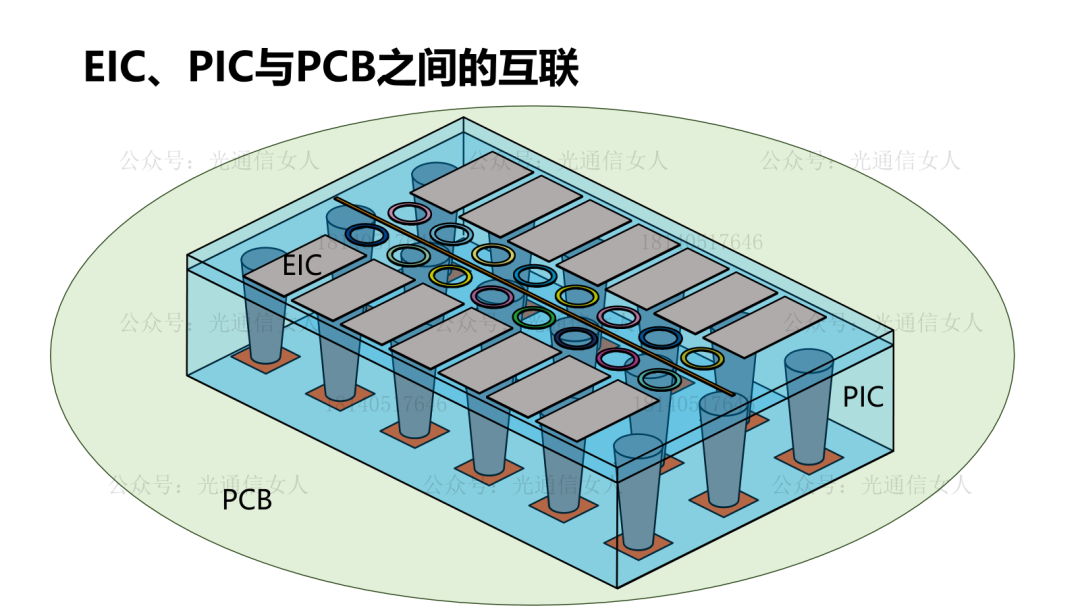

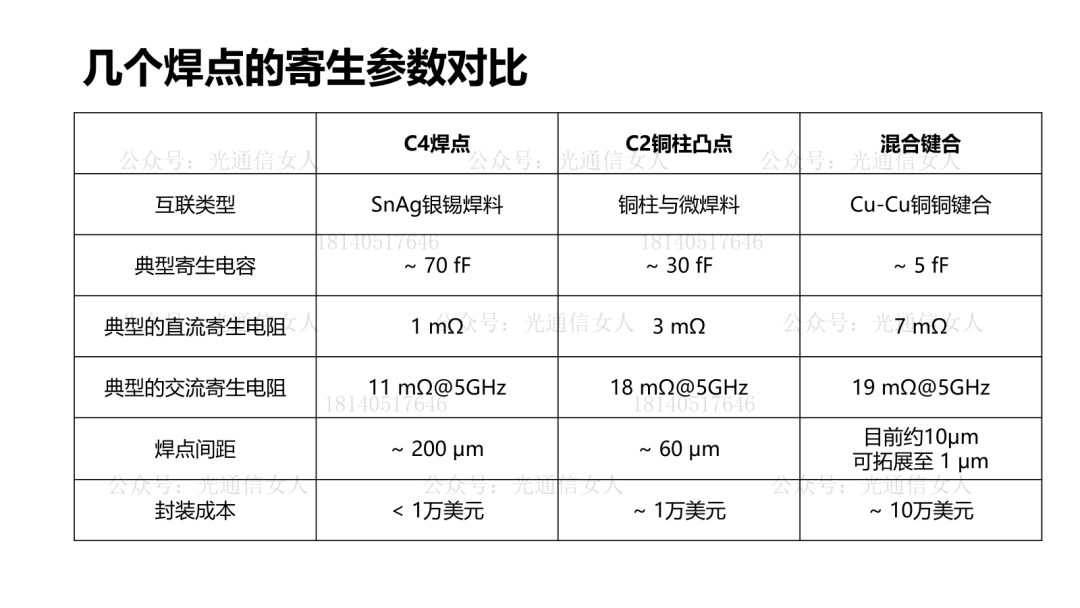

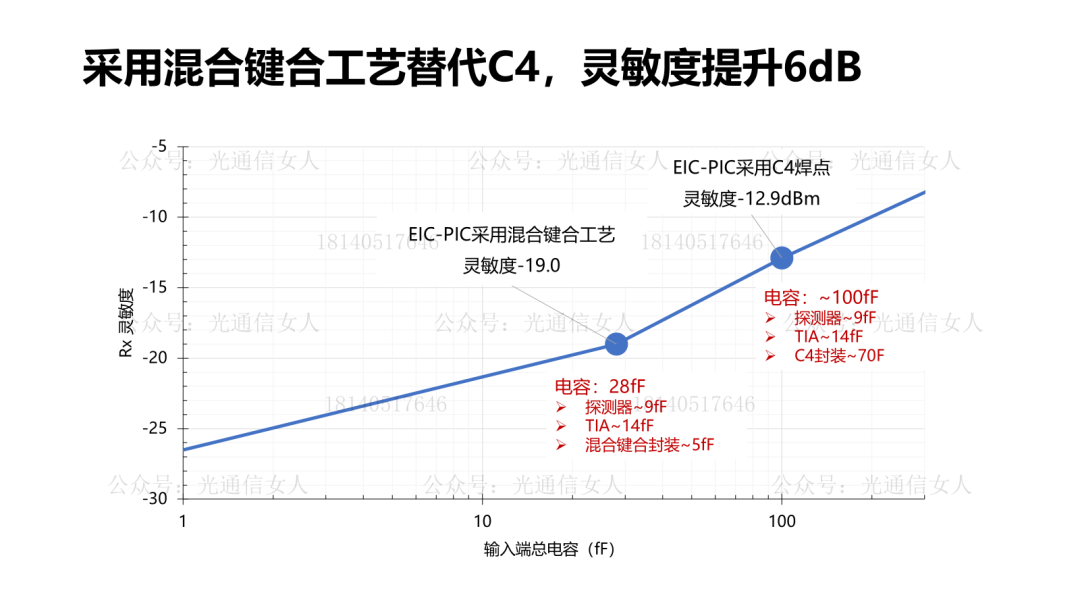

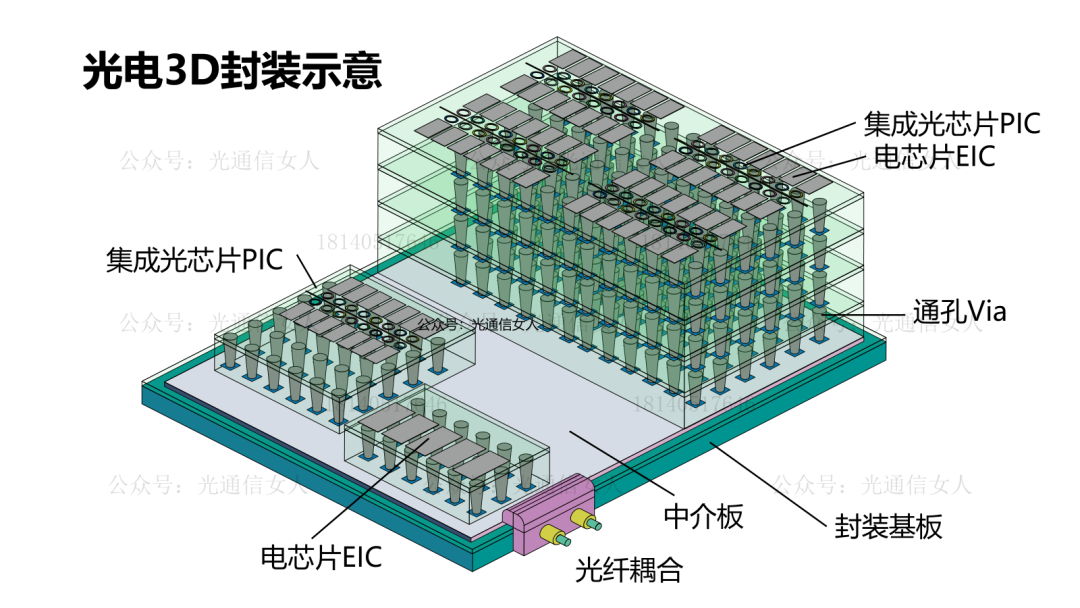

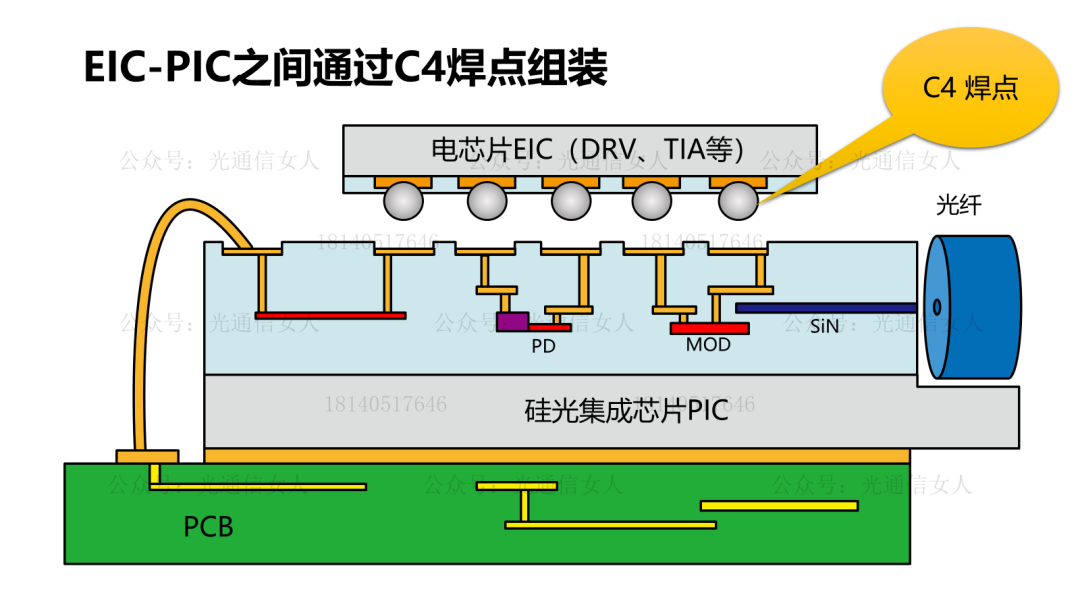

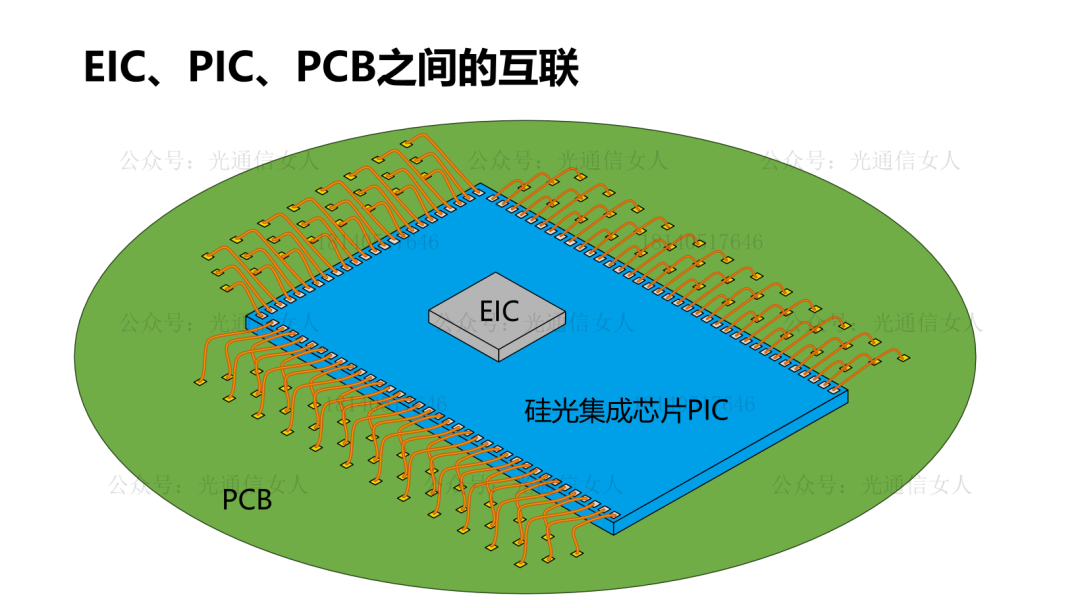

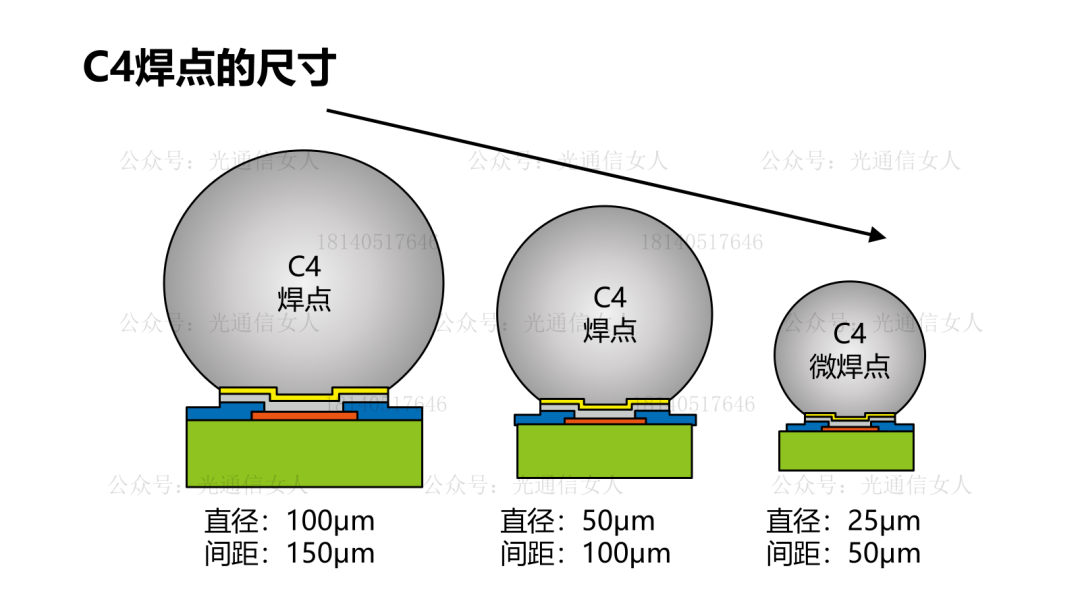

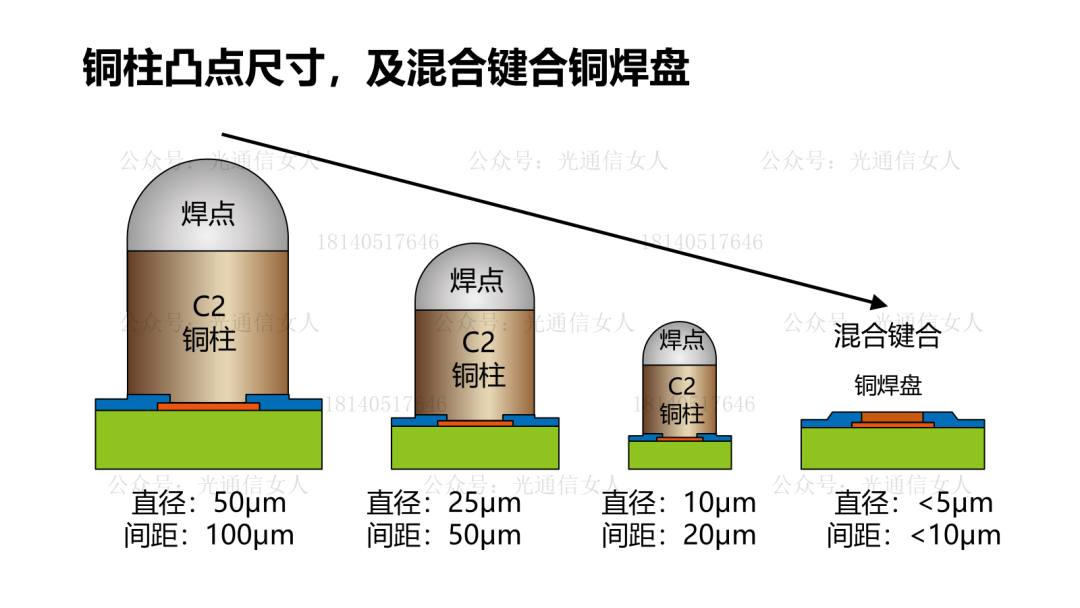

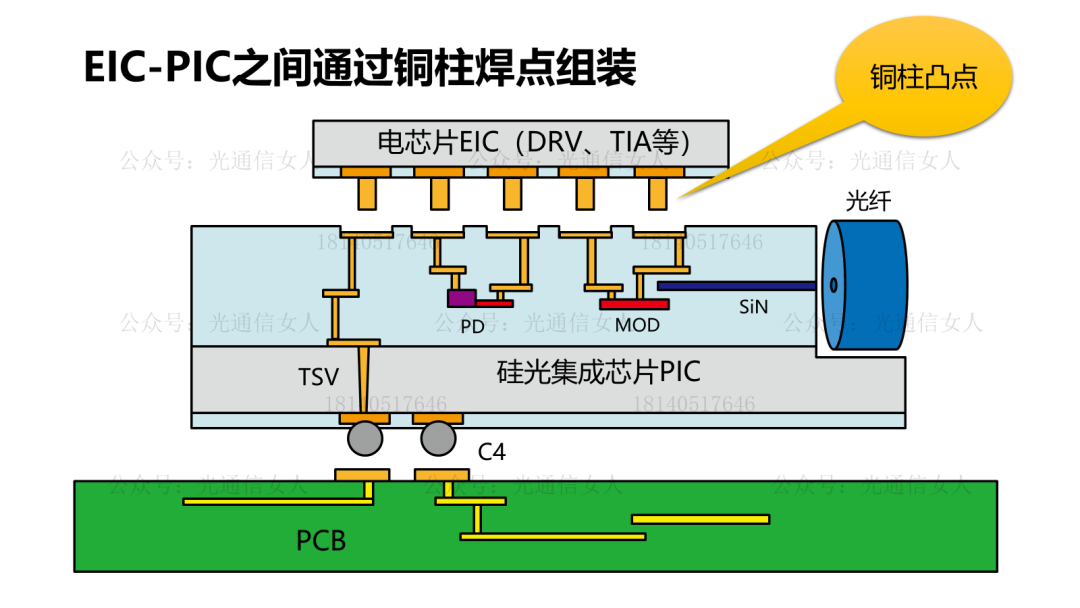

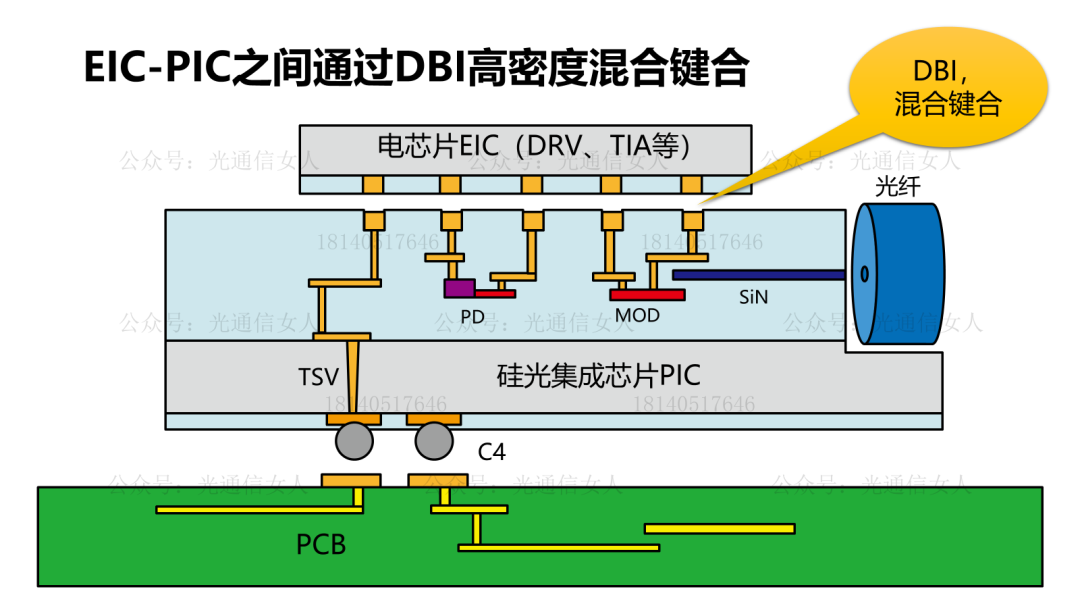

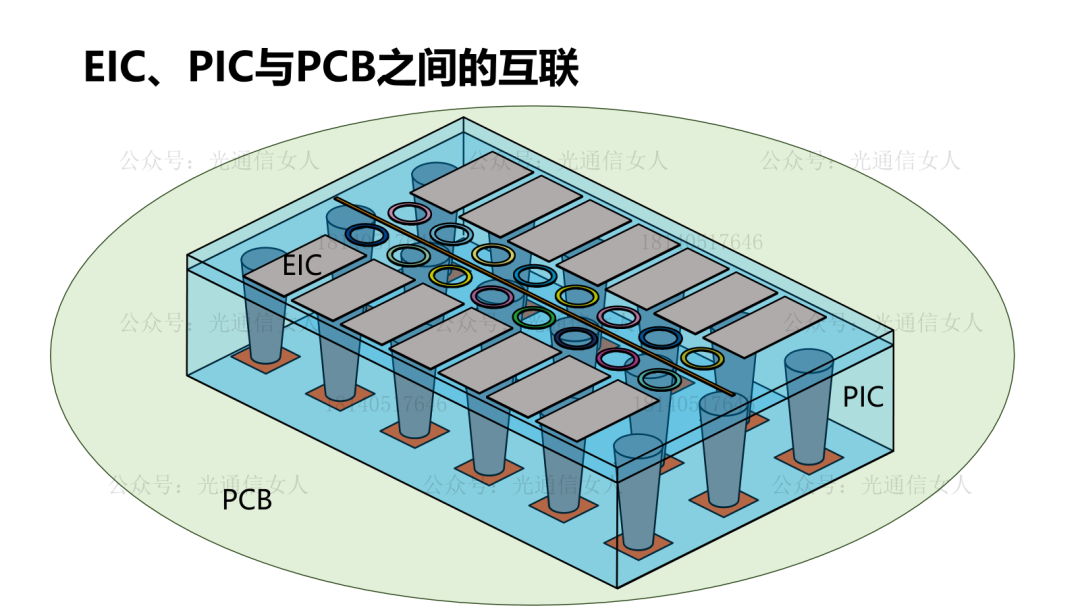

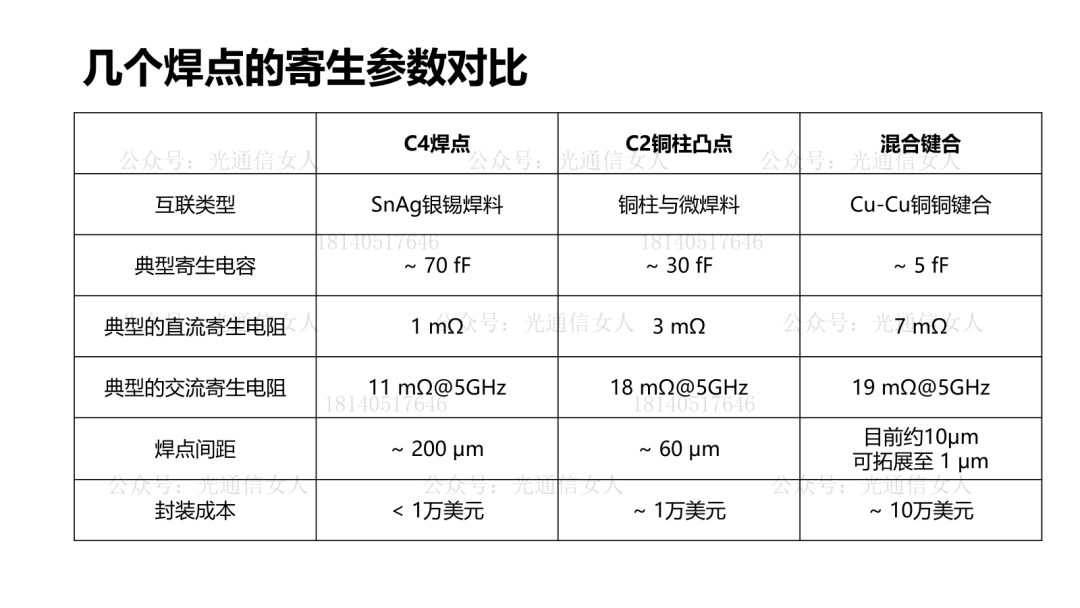

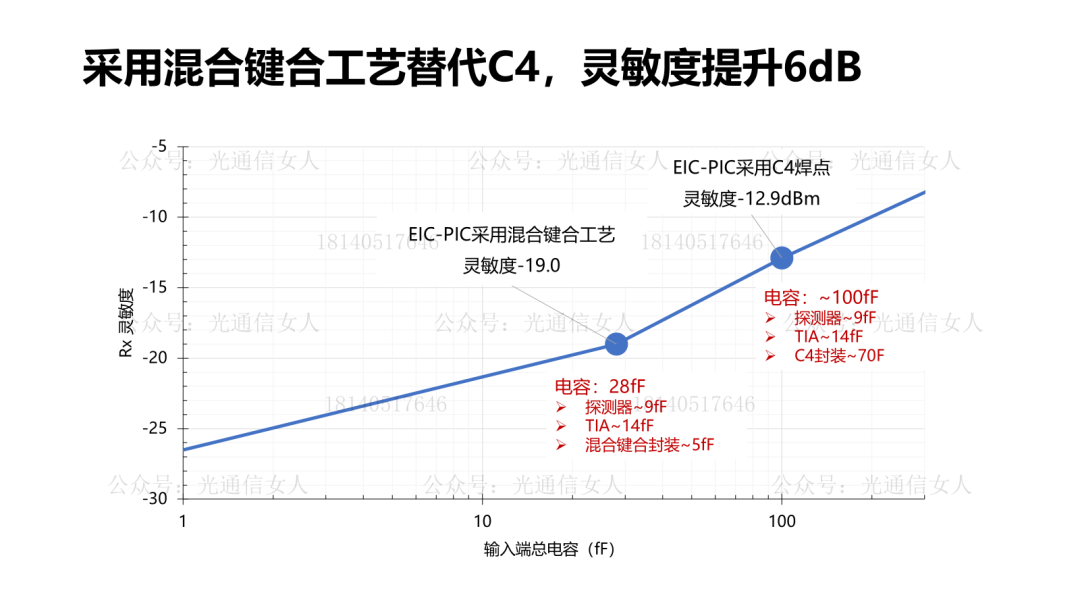

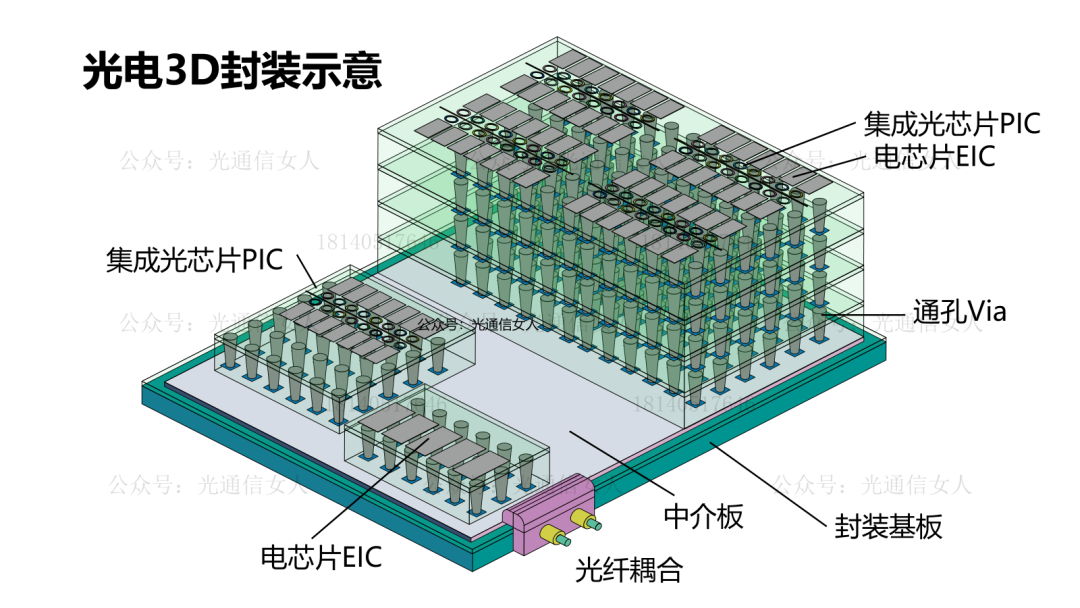

现在的硅光芯片3D封装,电芯片EIC与硅光芯片PIC“叠摞”焊接,C4凸点、铜柱C2凸点或者是混合键合,UCdavis大学做了焊点工艺与寄生参数的分析,以及与灵敏度的关系。之前他家就分析这些内容,Y9T161 硅光芯片与电芯片采用DBI或C4高密度大带宽互联可以通过C4焊点来连接EIC与PIC,焊点间距在150-200μm,硅光芯片与PCB可以采用键合金丝互联。一个立体示意图如下所以,EIC与PIC之间焊点的寄生电容约70fF,如果是接收端,硅光芯片的PD例如为9fF,到TIA放大器的输入电容为14fF,而EIC芯片之间的C4焊点电容如果为70fF, 整体输入总电容接近100fF,会导致带宽受限,导致高频信号的衰减,劣化灵敏度。产业也在不断的优化C4焊点向小型化路径演进,但由于焊料的高温熔融塌陷,其总体的焊点间距是受限的。另一种更小型化的方式是采用铜柱凸点工艺。焊料采用银锡的话,铜的熔融温度高于锡基焊料,铜柱支持焊点间距进一步缩小。而采用混合键合工艺,则大幅度降低引脚间距,提高带宽,以及优化灵敏度。采用铜柱焊点的工艺可如下示意图。硅光芯片与PCB也可以将键合金丝优化为TSV的硅通孔。~~,TSV是一种硅光芯片的衬底通孔,有些公司则是用其他孔,如博通、台积电用的是扇出的绝缘介质孔,不是硅通孔。回到EIC与PIC的工艺,C4焊点以及铜柱凸点,铜铜键合的工艺,其寄生电容差异很大。采用混合键合工艺替代C4,其中C4封装引起的70fF电容就可以降低为5fF,其他电容不变,仅仅优化封装工艺,就可以得到6dB的性能提升。采用混合键合,是高密度封装工艺,也称之为DBI。先进封装的成本也会增大。UC davis大学给出一个未来的光电3D封装的示意图。采用更多阶的高密度3D封装,提高线路密度,优化性能。4月11日,《人工智能AI大算力驱动的高速光模块/引擎发展趋势》,三个小时,可详询18140517646

转载说明:本文系转载内容,版权归原作者及原出处所有。转载目的在于传递更多行业信息,文章观点仅代表原作者本人,与本平台立场无关。若涉及作品版权问题,请原作者或相关权利人及时与本平台联系,我们将在第一时间核实后移除相关内容。