AI 重构集成电路设计:从数字后端到射频前端,一场正在发生的设计革命

传统 IC 设计的困局:数字与模拟 / RF 的双重痛点

1. 数字后端:复杂度爆炸下的效率天花板

2. 模拟 / RF 设计:经验密集型的 “卡脖子” 环节

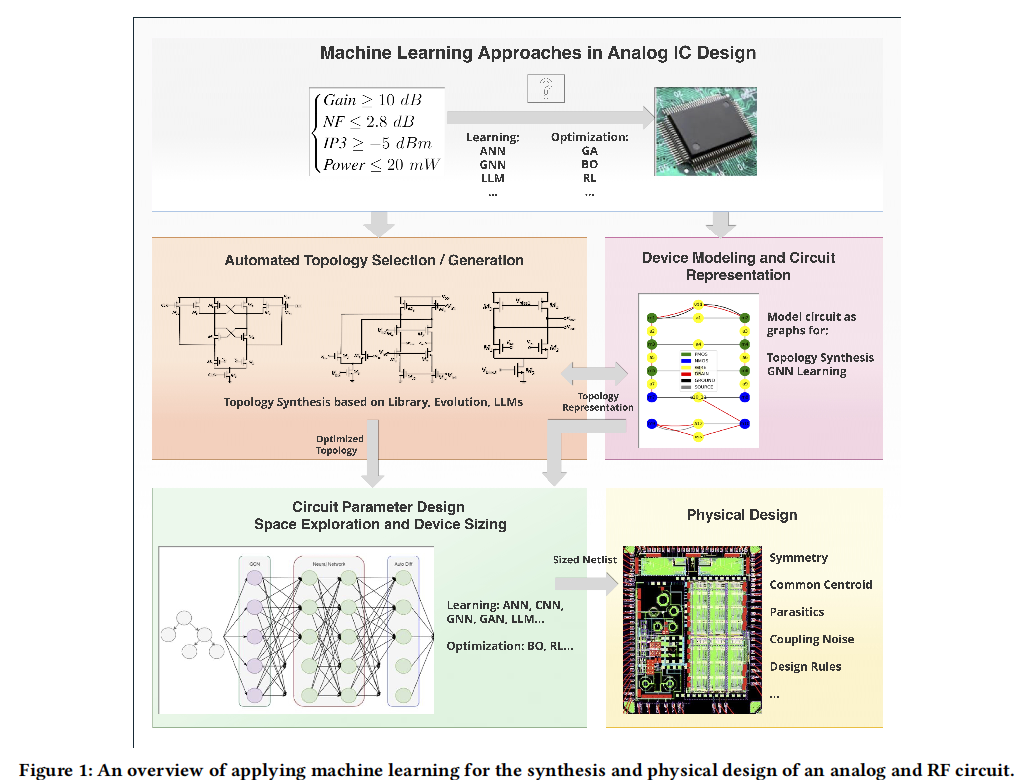

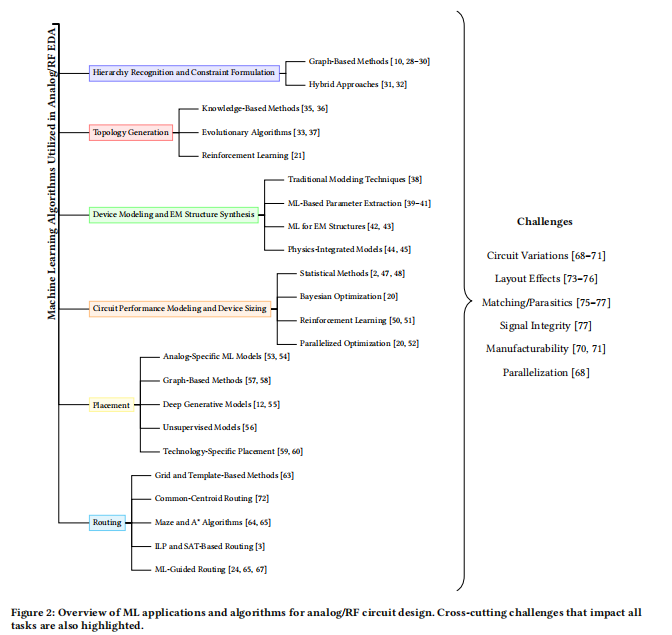

【文献图示标注】对应《Emerging ML-AI Techniques for Analog and RF EDA》图 1:Machine Learning Approaches in Analog IC Design(图示说明:展示 AI 在模拟 IC 设计中覆盖拓扑生成、器件建模、尺寸优化、物理设计全流程)

AI 在数字 IC 后端:全流程智能化,效率与质量双突破

1. 逻辑综合:从 “固定脚本” 到 “智能策略进化”

深度强化学习(DRL)

:A2C、A3C、ERL 框架直接把综合问题转为序列决策,动态选择优化序列,面积最高缩减64.9%、功耗平均优化16.01%;

主动学习 + 图神经网络

:Bulls-Eye 框架用小样本微调,运行速度提升2–30 倍,QoR 达传统方法 95%;

生成式 AI

:Circuit Transformer 结合 GAN 实现等价 AIG 变换,自动优化逻辑结构,突破人工改写局限。

2. 布局布线:AI 把 “周级工作” 缩到 “6 小时内”

Google 基于GNN+DRL将芯片布局建模为马尔可夫决策过程,PPO 算法训练后,6 小时完成专家数周工作量,超越传统人工与 EDA 工具;

ibUNet 神经网络

:精准预测布线拥堵与 DRC 热点,提前疏导拥挤区域,大幅减少后期返工;

Wiremask-EA 框架

:预测线长增量,引导进化算法优化宏单元布局,兼顾可布线性与线长目标。

3. 时钟树综合(CTS):功耗与偏移的精准平衡

GAN-CTS 框架

:三阶段学习精准预测时钟功耗、线长、最大偏移,给出参数建议;

ANN 预测时钟缓冲器

:平均减少 **31%** 缓冲器数量,功耗估计误差 < 5%,显著降低时钟网络功耗;

智能架构实现对称时钟分发,提升时序余量与工作频率。

AI 在模拟 / RF IC 设计:从 “靠经验” 到 “全自动”

1. 拓扑生成:AI “创造” 超越人类的电路结构

强化学习

:逐次添加器件与连接,自动生成运放、LNA 等拓扑,性能超人工设计;

进化算法

:以矩阵编码拓扑,交叉变异探索 10^19 级空间,发现高效新颖结构;

LLM+RL

:大模型理解指标,生成拓扑后用 RL 优化,实现指标到拓扑的端到端生成。

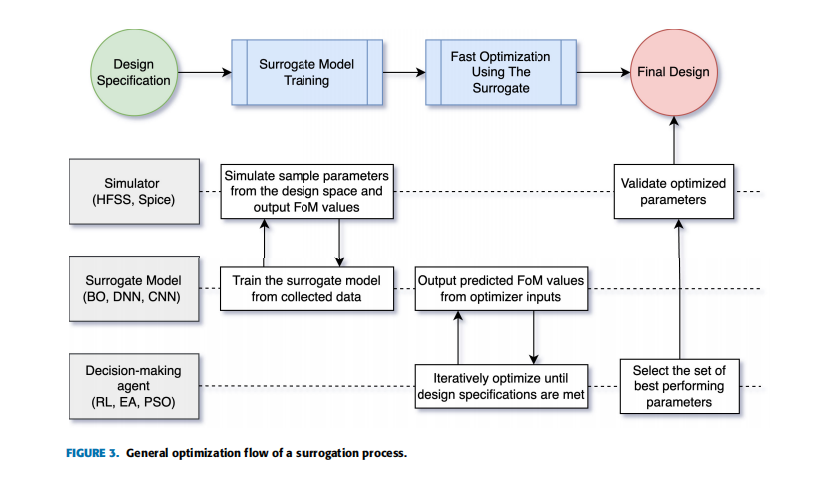

2. 器件尺寸与性能建模:秒级替代 SPICE 仿真

GNN+RL(GCN-RL)

:电路图表示提取结构特征,跨拓扑、跨工艺节点迁移,减少重复训练;

贝叶斯优化(BO)

:样本效率极高,用极少仿真点逼近 Pareto 最优,适合多目标权衡;

深度代理模型

:DNN/CNN 快速预测增益、噪声、S 参数,速度比 EM/SPICE 快100–1000 倍。

【文献图示标注】对应《AI-Driven Integrated Circuit Design》图 3:General optimization flow of a surrogation process(图示说明:代理模型训练→快速优化→仿真验证的标准 AI 设计流程)

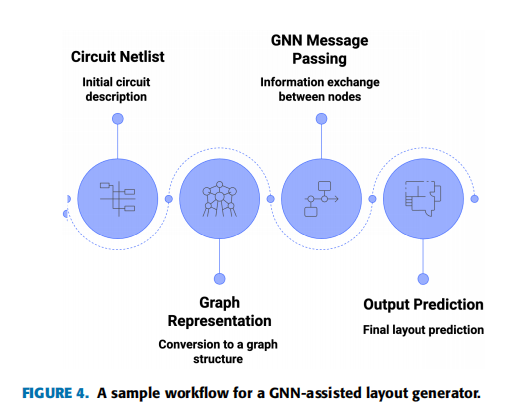

3. 版图自动化:对称、匹配、寄生一站式解决

DeepPlacer

:深度生成模型毫秒级输出满足约束的版图;

GAN/Transformer

:WellGAN、MAGICAL 实现从网表到 GDSII 全自动,DRC/LVS 通过率大幅提升;

GNN 约束提取

:自动识别对称组、匹配规则,把人工周级工作缩至小时级。

【文献图示标注】对应《AI-Driven Integrated Circuit Design》图 4:A sample workflow for a GNN-assisted layout generator(图示说明:电路网表→图表示→GNN 消息传递→布局预测的完整流程)

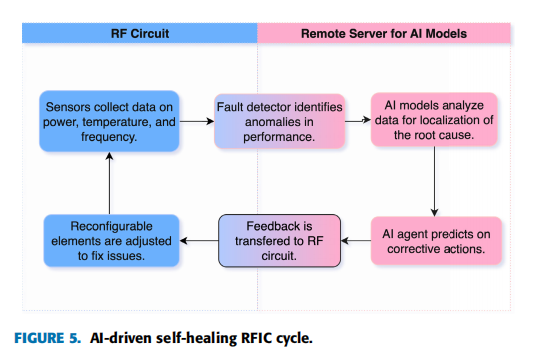

4. 硅后校准与自修复:芯片 “自带智能大脑”

RL 自校准

:实时调整偏置、电容阵列,补偿 PVT 偏差,提升良率与稳定性;

故障诊断

:1D-CNN、LightGBM 精准定位软故障,支持在线修复;

自修复架构

:传感器 + AI 决策 + 可重构硬件,实现失效旁路与性能自愈。

【文献图示标注】对应《AI-Driven Integrated Circuit Design》图 5:AI-driven self-healing RFIC cycle(图示说明:传感器采集→故障检测→AI 决策→电路重构的闭环自愈流程)

AI 驱动 IC 设计的核心技术栈:四大算法撑起全流程

深度强化学习(DRL):sequential 决策最优解适合布局、综合、尺寸优化等序列决策,代表算法:PPO、A2C、A3C、DDPG。

图神经网络(GNN):天生适配电路结构电路天然是图,GNN 捕捉连接与拓扑,用于寄生预测、约束提取、拓扑表征。

贝叶斯优化(BO):小样本高效全局寻优适合仿真昂贵的模拟 / RF,用高斯过程等代理模型平衡探索与利用。

生成式 AI(GAN/VAE/LLM):从 “优化” 到 “创造”GAN 做逆设计与版图生成,LLM 理解自然语言指标、生成代码与方案,RAG 减少幻觉。

【文献图示标注】对应《Emerging ML-AI Techniques for Analog and RF EDA》图 2:Overview of ML applications and algorithms for analog/RF circuit design(图示说明:ML 算法在约束定义、拓扑、建模、优化、布局、布线的全景分布)

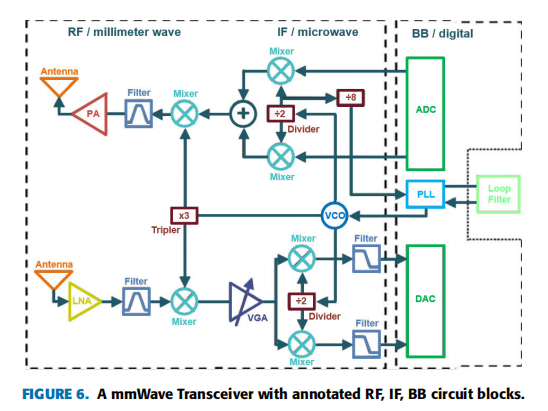

产业落地:从谷歌、新思到国内厂商,AI 已成标配

谷歌

新思、楷登

:DSO.ai 等 AI-EDA 工具,实现 PPA 全面提升;

国内

:概伦电子等推出 AI 布局工具,推动 AI 与 EDA 深度融合;

实测效果:某处理器面积缩 5%、功耗降 6%;5nm 移动芯片性能提 14%、功耗降 3%,1 人 10 天完成 10 人数月工作。

【文献图示标注】对应《AI-Driven Integrated Circuit Design》图 6:A mmWave Transceiver with annotated RF, IF, BB circuit blocks(图示说明:AI 已覆盖毫米波收发机所有射频 / 中频 / 基带模块设计)

挑战与未来:走向全自动、可解释、物理一致

1. 现存挑战

泛化性不足:跨工艺、跨拓扑迁移仍需优化;

数据壁垒:PDK 保密、高质量数据集稀缺;

可解释性差:黑盒模型难满足车规 / 医疗合规;

物理一致性:部分模型缺乏物理约束,结果不可制造。

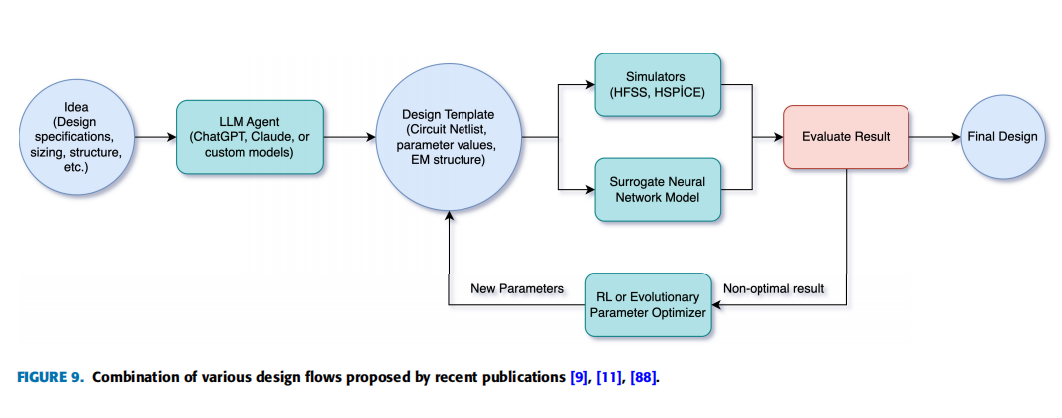

2. 未来方向

物理知情 AI(PINN)

:嵌入电路方程,减少数据依赖、提升泛化;

多智能体协同

:拓扑、尺寸、版图、测试 Agent 分工协作;

端到端全自动

:指标→拓扑→尺寸→版图→GDSII 一键完成;

可解释 AI(XAI)

:SHAP/LIME/Grad-CAM 提供决策依据,满足合规。

【文献图示标注】对应《AI-Driven Integrated Circuit Design》图 9:Combination of various design flows proposed by recent publications(图示说明:LLM 代理 + 神经网络代理 + 优化器 + 仿真器的全自动设计闭环)

写在最后:AI 不是替代工程师,而是重构设计范式

【文末参考文献】

热门文章导读

|

请戳右下角,给我一点好看!