Y12T114 稳懋:用于通信和传感的VCSEL批量制造

发布时间:2026-04-24来源:光通信女人

稳懋有GaAs材料体系的VCSEL晶圆代工,七年前写过他家,Y5T226 激光器芯片器件产业链:Winsemi 穏懋2026年OFC,稳懋做了个技术报告,聊了一下VCSEL的批量制造的发展方向。- Y12T77 VCSEL的模式、带宽与可靠性的矛盾

- Y12T60 博通 200G VCSEL进展,NPO进展

- Y12T104 Coherent:VCSEL CPO功耗进展

- Y12T41 Lumentum:VCSEL输出偏振控制

- Y11T259 海思:高速VCSEL用于AI场景光模块或NPO

- Y11T210 华为 212G VCSEL传输验证

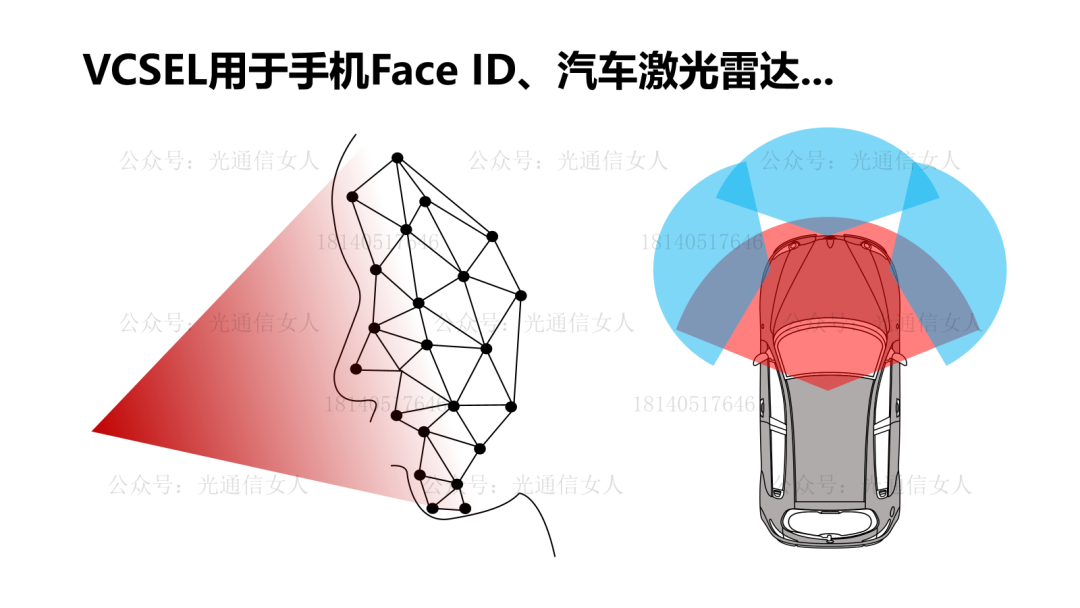

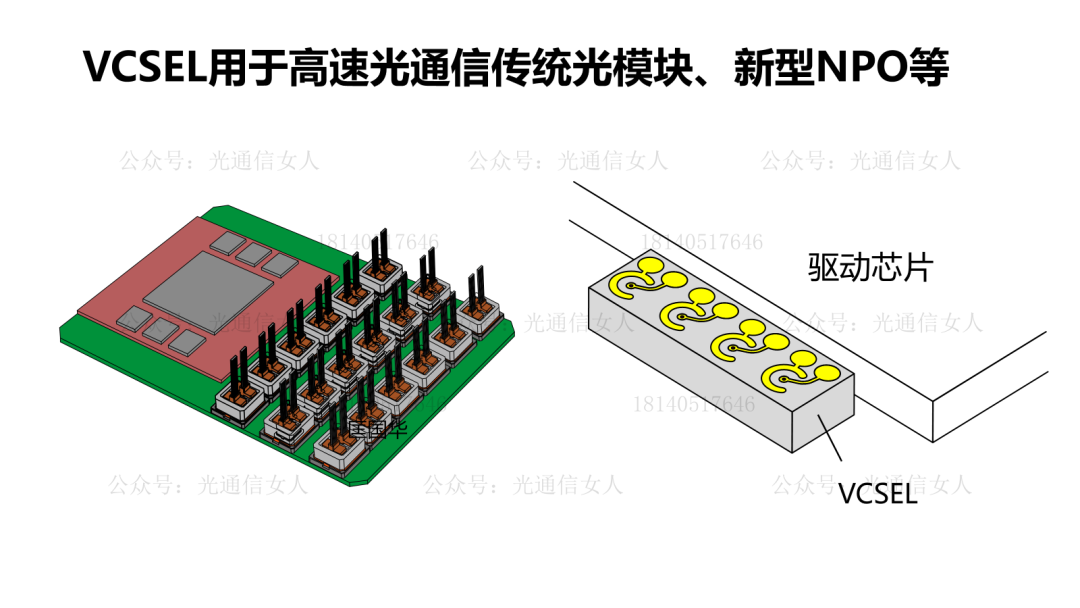

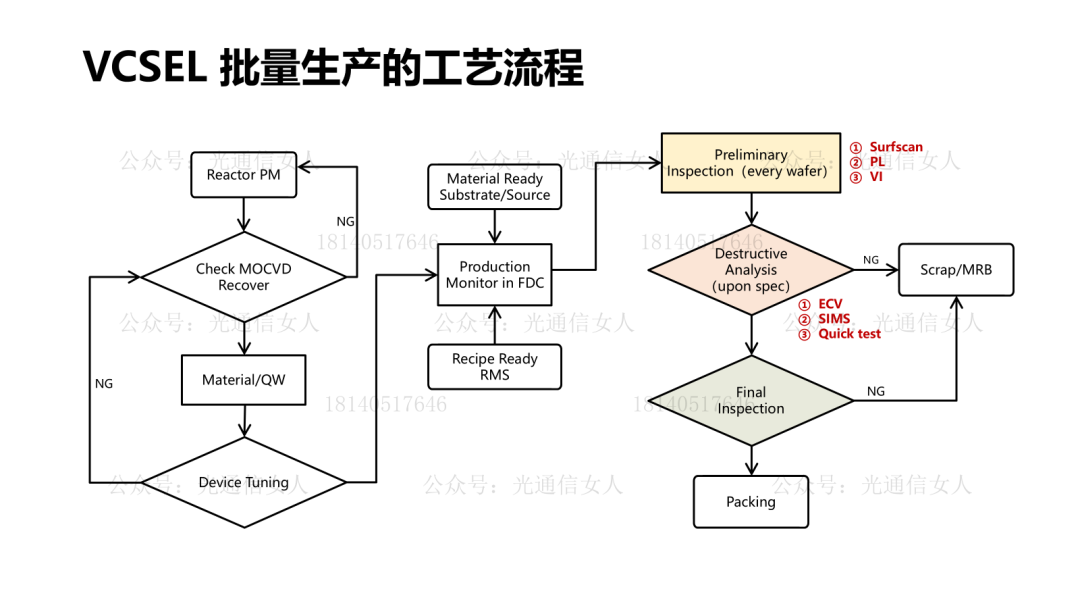

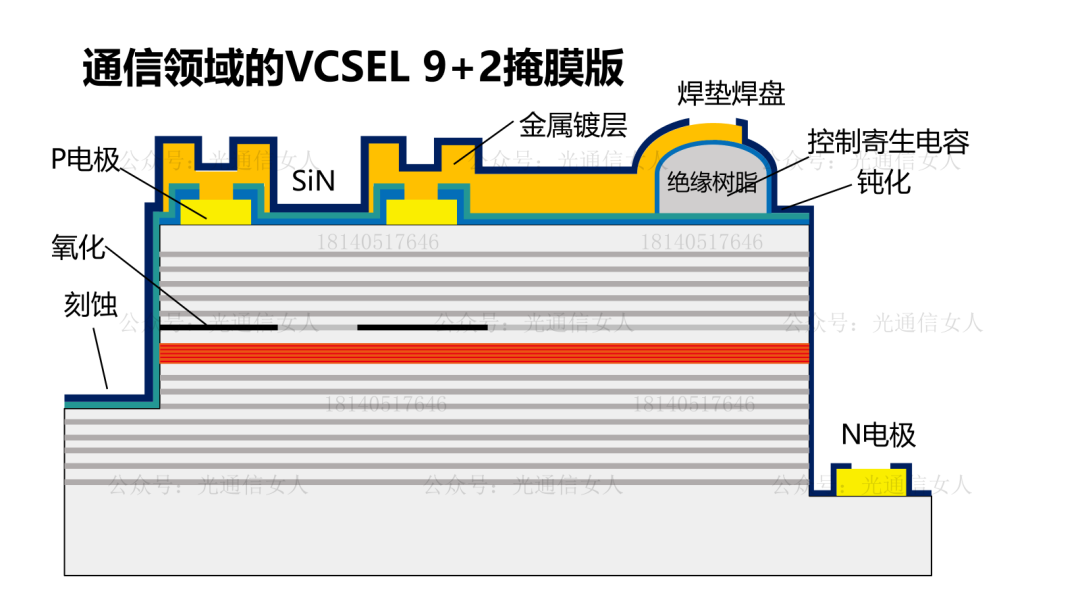

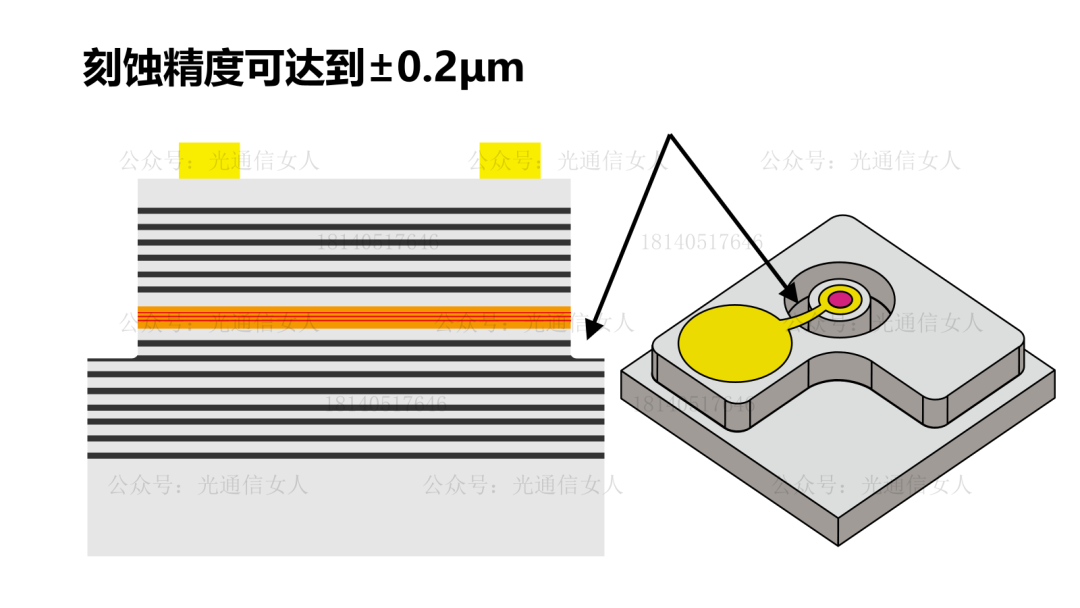

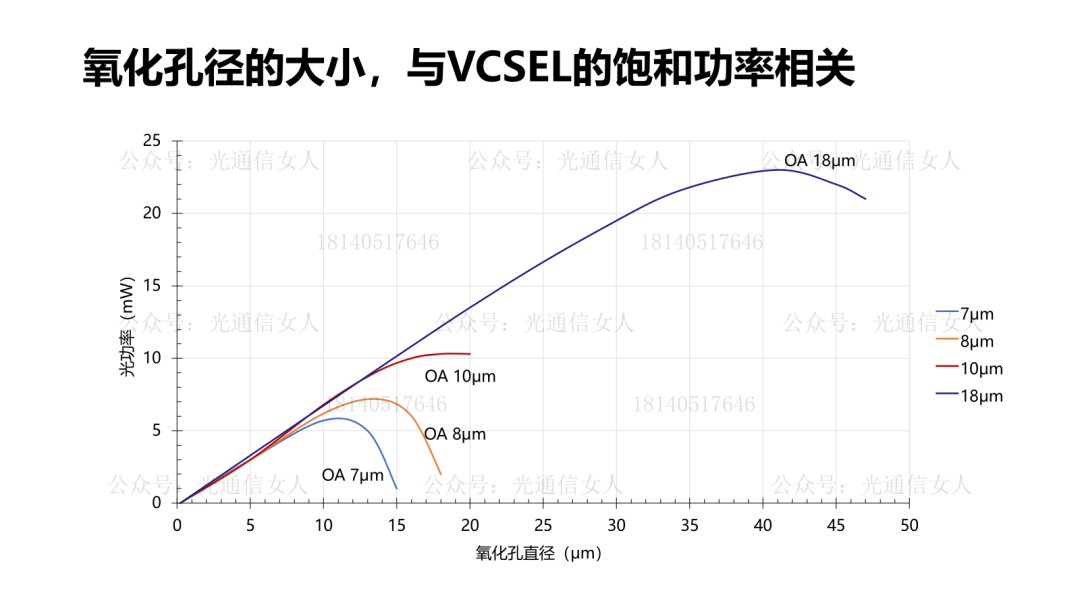

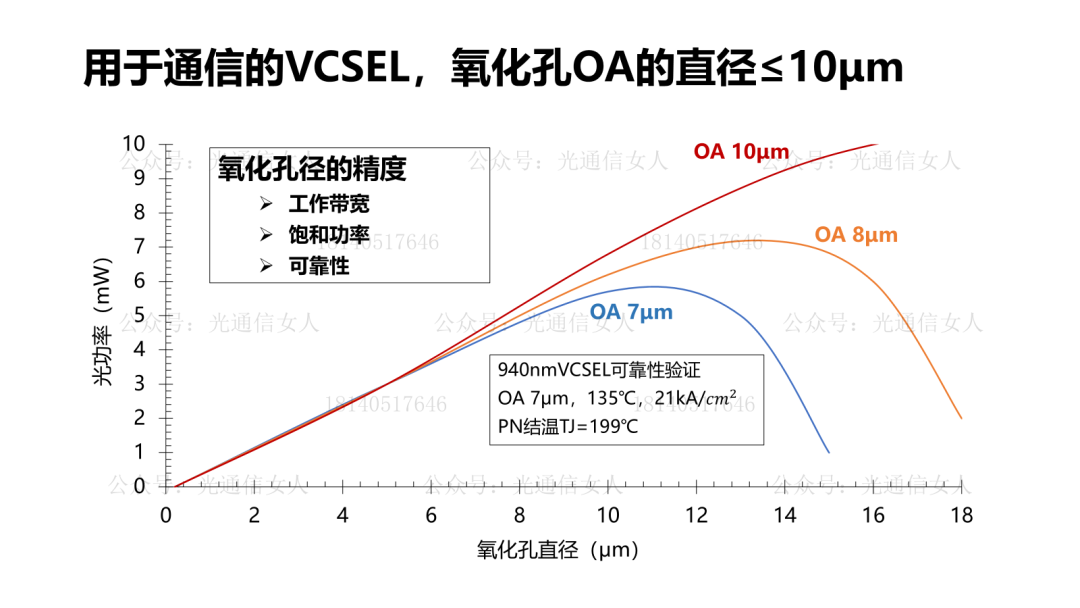

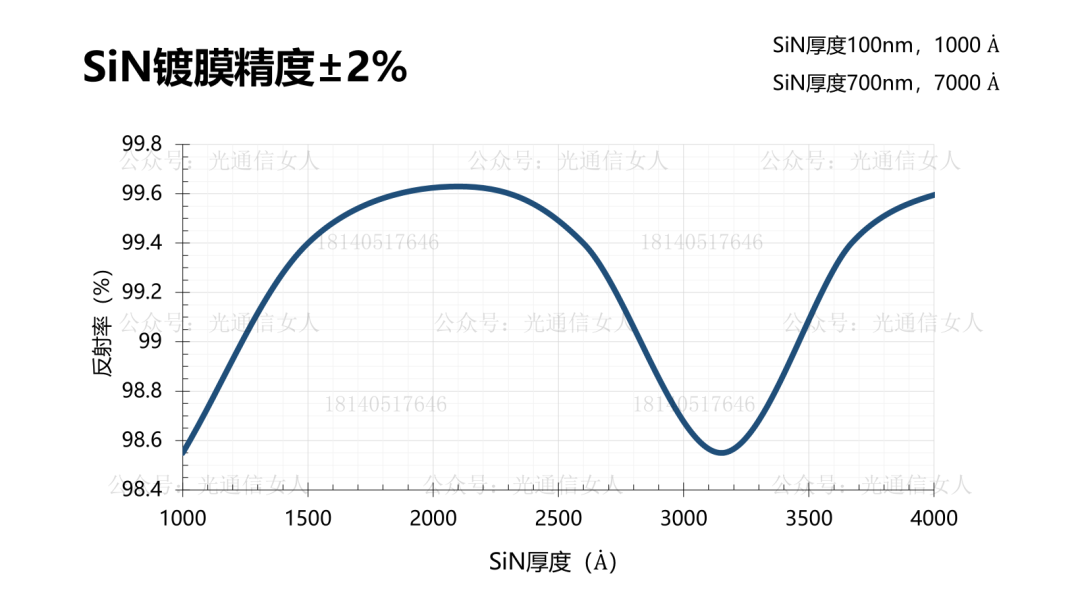

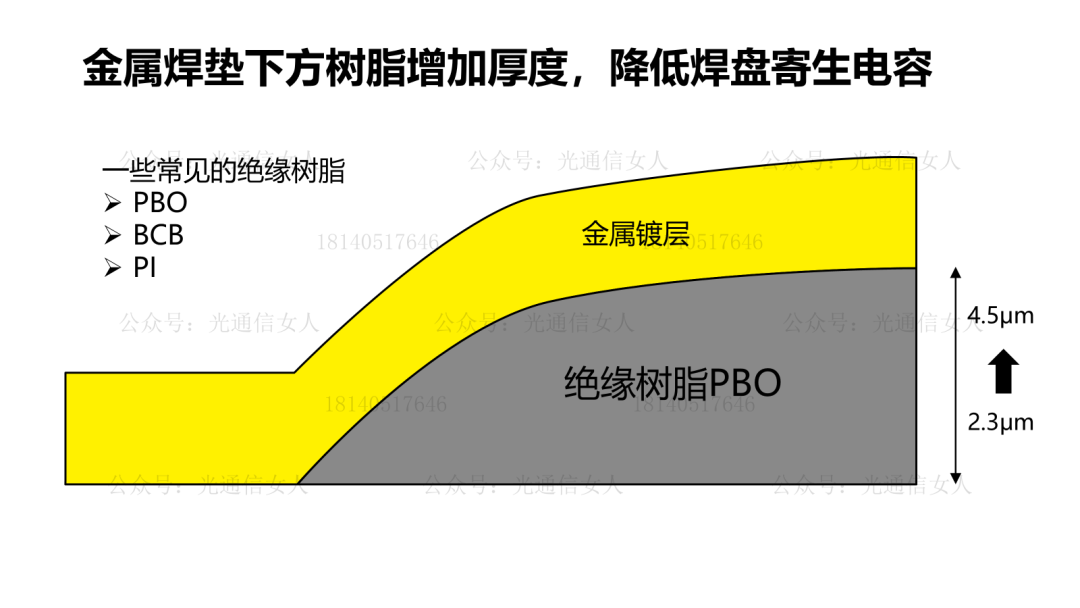

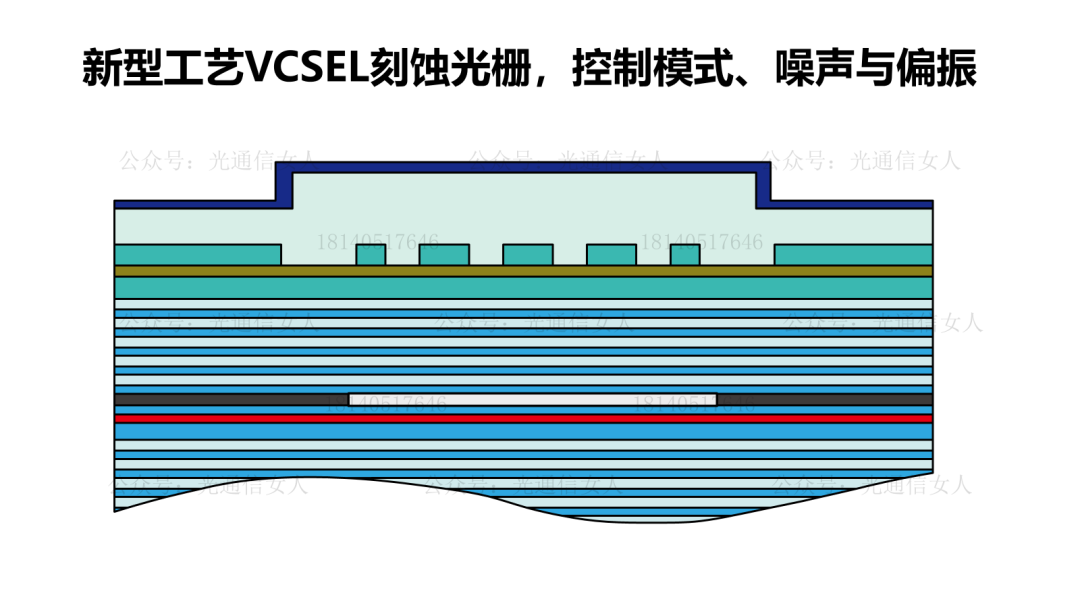

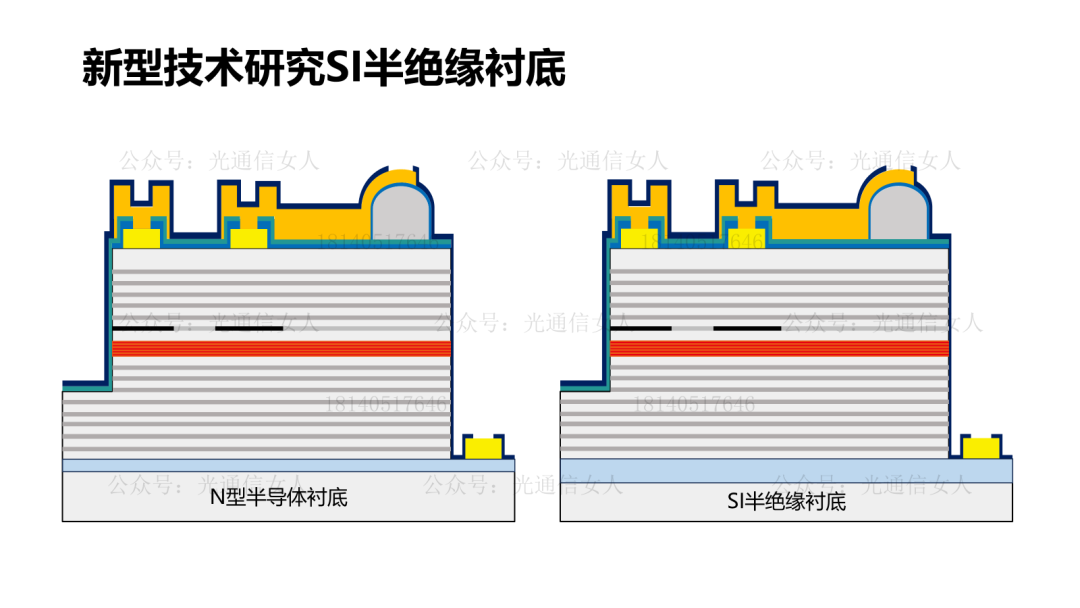

用于传感领域,调制速率很低,对光功率、热效率、电光效率....的要求较高。用在通信的VCSEL,则考虑的是带宽、功耗、可靠性以及热效应。用于传感的VCSEL,氧化孔径要大一些,设计的复杂度也没有通信那么多。传感需要9个掩膜版,而通信VCSEL则需要9+2的掩膜版,且对于高速信号处理的挑战越来越大。深刻蚀,需要做N型接触、侧氧化工艺。底部的N型DBR内部有高铝层用于散热,深刻蚀工艺精度需要尽量精确,避免可靠性风险。对于氧化孔径而言,传感的孔径很大,主要考虑进一步提高饱和功率。而通信VCSEL,为了提高带宽,会尽量降低氧化孔的直径,降低RC常数。对于小孔径大带宽的设计,要考虑饱和功率,PN结的结温以及带宽之间的权衡。稳懋给了两组可靠性测试条件,940nm波长,7μm氧化孔径,电流密度21kA/cm2, 135℃,激光器芯片的PN结结温199℃。另外一组参数,940nm波长,710μm氧化孔径,电流密度21kA/cm2, 150℃,激光器芯片的PN结结温220℃。在很重要的刻蚀,氧化工艺外,光窗的SiN钝化层的薄膜厚度的精度对性能也有影响。稳懋可控制薄膜厚度的精度在±2%,用于控制光窗的透反射率以及光子寿命。在传统的氧化工艺外,一些工艺还需要不断的优化和开发。比如焊盘下方的绝缘树脂垫,索尼用的是BCB,很多厂家也用PBO或PI,这个垫子用来降低焊盘的寄生电容,提高带宽。稳懋用PBO树脂,厚度从2.3μm向4.5μm高度发展。Y12T41 Lumentum:VCSEL输出偏振控制另外,主流VCSEL厂家开始研究通过顶部光栅控制VCSEL模式,噪声以及偏振,用于提高多模传输的有效带宽。Y11T263 阿里:AI组网多模通信的优劣势及观点稳懋也在研究VCSEL的顶部光栅的DUV刻蚀工艺。大多数VCSEL用的是半导体GaAs衬底,现在稳懋在研究SI半绝缘衬底,从而降低衬底射频损耗,提高带宽。InP的很多大带宽芯片,比如差分EML,从半导体InP衬底向SI半绝缘InP衬底发展。GaAs的大带宽芯片,也是同样的思路,从半导体GaAs衬底向SI半绝缘GaAs衬底发展,有利于提高带宽。5月13日,《高速信号调制器格式NRZ、PAM4、QPSK以及n-QAM》,可详询18140517646

转载说明:本文系转载内容,版权归原作者及原出处所有。转载目的在于传递更多行业信息,文章观点仅代表原作者本人,与本平台立场无关。若涉及作品版权问题,请原作者或相关权利人及时与本平台联系,我们将在第一时间核实后移除相关内容。