概伦电子9812AC:洞察交流噪声独特行为,拓宽射频电路设计空间

在万物互联的新时代,常用的通信频段正变得日益拥挤。随着手机网络、卫星通信和雷达传感等新兴技术的快速发展,集成电路需要在更高频段下稳定运行。器件特性参数的准确提取,对射频电路性能优化至关重要。概伦电子9812AC动态交流测试系统,创新性地引入动态方波激励技术,跨越直流偏置测试的局限,还原了器件在真实工况下的噪声特性。

01

射频电路的相位噪声

VCO电路工作原理

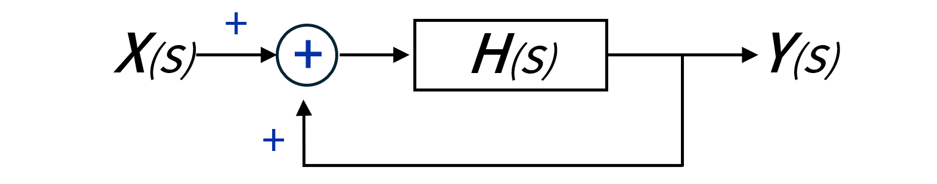

对于射频集成电路而言,高质量的频率源尤为关键。压控振荡器(VCO)作为频率源的核心模块,也是一个重要的噪声源。压控振荡器本质上是一个正反馈系统,通过把电路自身的微小信号不断放大,形成振荡,最终产生特定频率的信号。

压控振荡器的反馈模型

相位噪声对VCO电路的影响

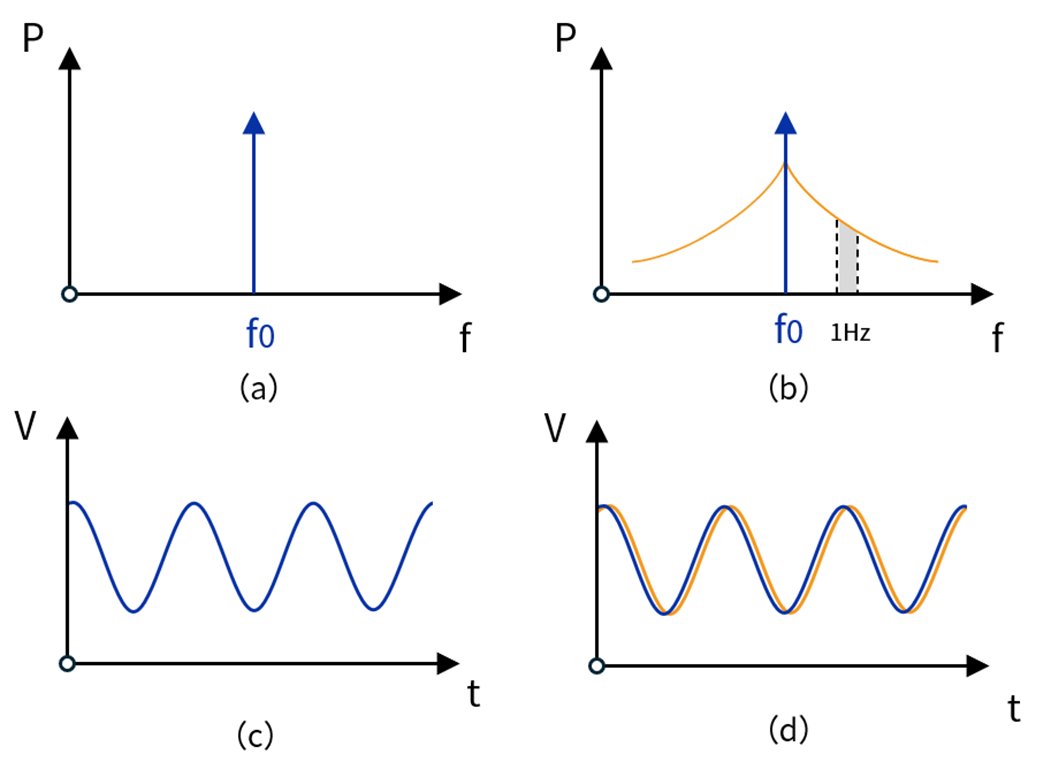

理想情况下,VCO应该输出一个完美的正弦波,但实际中由于各种噪声干扰,信号会变得“不干净”,在频域上表现为载波周围出现一些不需要的边带,这就是相位噪声。相位噪声作为振荡器的关键性能指标之一,将直接关系到信号的谱频纯度,从而影响到频率源乃至整个电路系统是否能够稳定、高效地运行。射频电路中相位噪声的恶化可能导致通信误码率上升,雷达探测精度下降,测试误差增大。

输出相位噪声:

频域谱线(a)理想(b)实际;时域波形(c)理想(d)实际

02

器件低频噪声对相位噪声的影响

DC噪声的影响

若想改善相位噪声,首先要了解振荡器相位噪声的产生机制。经典Leeson模型(1966)假定振荡器的相位噪声由白噪声和1/f噪声构成。通过剖析这些噪声在振荡器回路中的传播情况,可以推导出相位噪声特性。

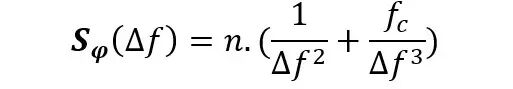

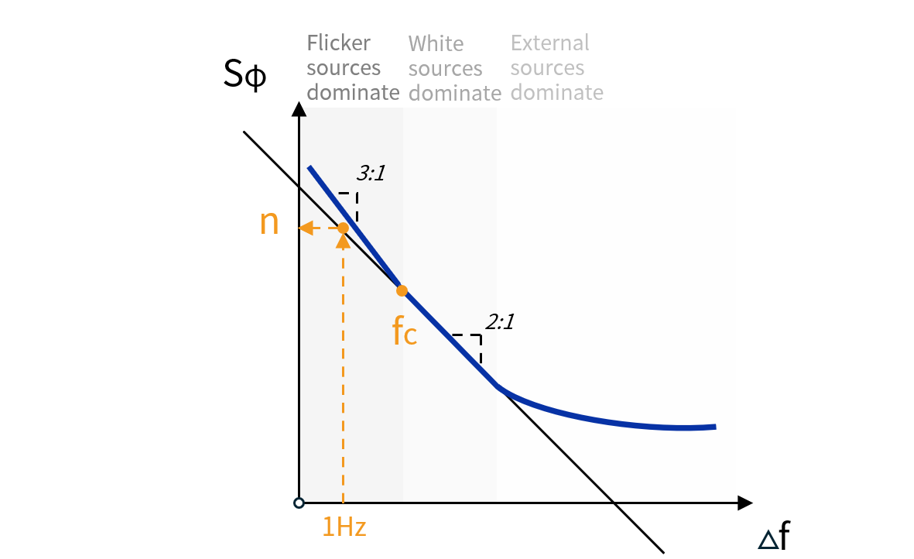

在传统噪声测量与模型建立中,施加直流偏置所得到的1/f噪声(DC噪声),长期以来被视为评估器件低频噪声性能的主要依据。对于VCO而言,相位噪声功率谱密度的理论表达式为:

*其中,n 表示△f=1Hz处的白噪声功率,fc为1/f噪声拐角频率。

VCO相位噪声曲线

VCO的相位噪声曲线呈现三段式特征:在△f<fc时由1/f噪声主导,斜率-30dB/dec;在△f>fc时,斜率-20dB/dec;在△f>>fc时,曲线平坦与频率无关。依据曲线,n可由白噪声主导区的-20dB/dec斜率反推至1Hz获得,fc则可直接从两段斜率线的交点读出。

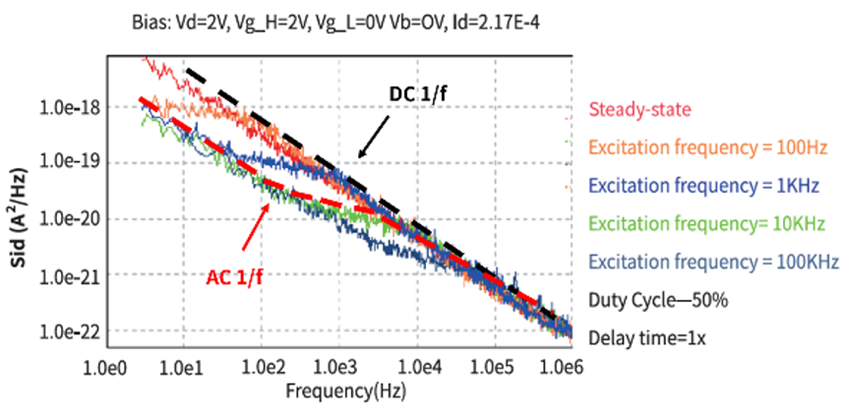

AC噪声带来的变化

当分析对象从器件延伸至如VCO这类具备周期性大信号工作的电路时,仅依赖 DC噪声,往往不足以完整解释实际电路中的相位噪声表现。这是因为,VCO电路中的有源器件并非工作在静态偏置点,而是处于随时间周期性变化的动态工作状态。在这种情况下,器件1/f噪声的统计特性与谱频分布将偏离直流偏置条件下的测量结果。

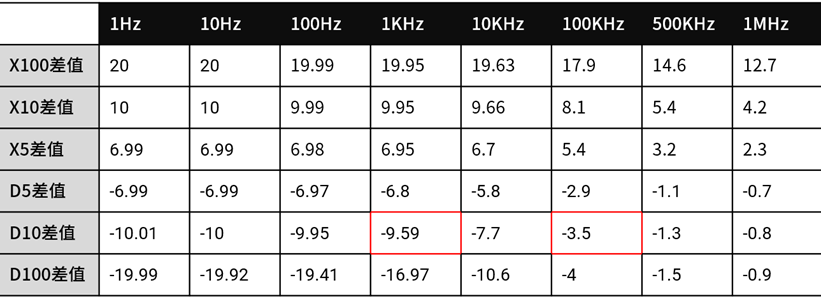

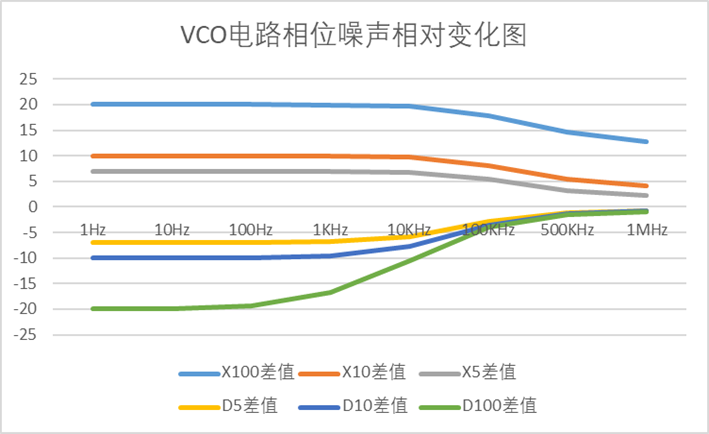

9812AC实测结果:不同频率下的交流噪声测试结果

从概伦电子9812AC的实测数据可以看出,在低频段,AC噪声测试的结果相对DC噪声会有所降低。一方面,9812AC可用于筛选在动态工作条件下噪声表现更优的器件;另一方面,该表征工具也可在相位噪声建模中引入更贴近实际的噪声描述,从而显著提升电路性能预测精度。

概伦电子噪声测试系统981X系列是全球半导体行业低频噪声测试的“黄金标准”。9812AC专门为研究动态激励信号下的器件噪声特性和交流RTN效应而设计,支持不同频率和不同占空比下的交流激励信号,结合交流信号噪声模型,可更准确地评估工作状态中的器件噪声特性,帮助优化电路设计和性能指标。9812AC可广泛应用于半导体代工厂、IDM公司、集成电路设计公司和学术研究机构,为半导体新领域的研究探索提供了一个全新的专业工具。

03

VCO电路仿真实践

建立噪声模型

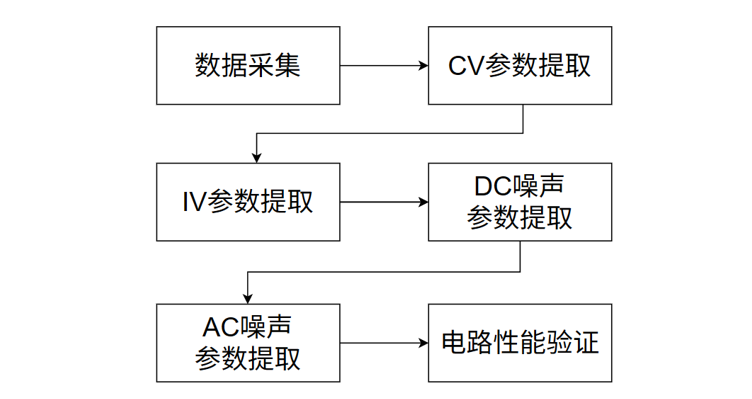

提取器件噪声模型

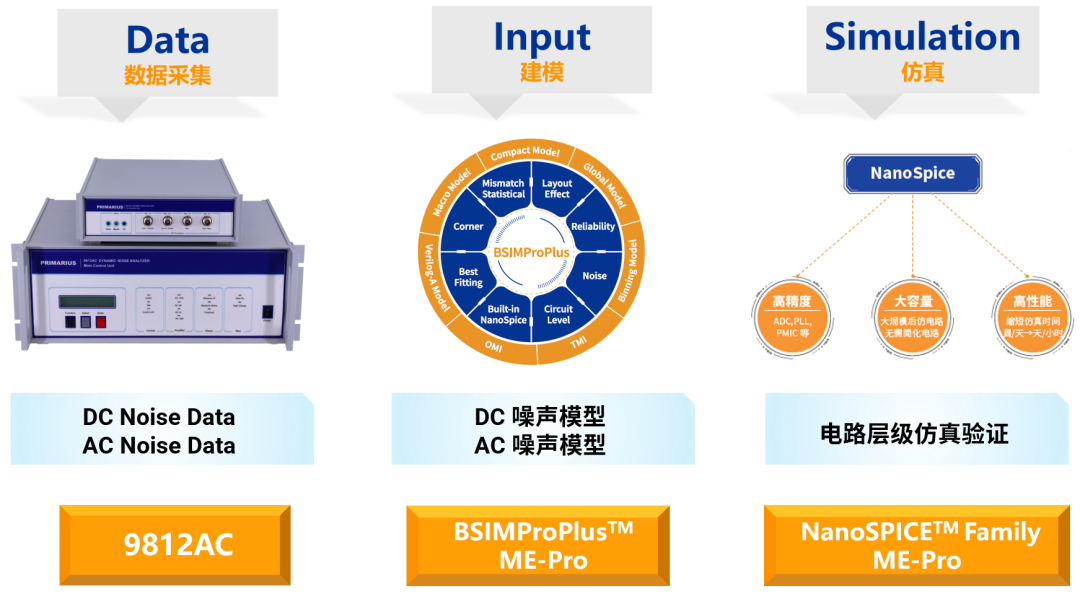

器件噪声模型提取流程

第一步:数据采集

通过器件参数分析仪FS800采集器件的IV、CV特性;通过动态交流噪声测试系统9812AC采集器件噪声特性,其中,测试DC噪声时,需要将占空比设定为1;测试AC噪声时,可根据VCO电路的真实情况,设置交流噪声测试参数。

第二步:MOS器件模型参数提取

在先进器件建模平台BSIMProPlus中选定要提取的MOS器件模型,例如BSIM4或BSIM Bulk。按照CV -> IV -> DC Noise -> AC Noise的顺序,提取出对应的参数值。

第三步:电路性能验证

当MOS器件模型完成后,可使用集成电路工艺与设计验证评估平台ME-Pro检验模型的收敛性和趋势,并和电路网表结合,进行电路端的仿真验证。

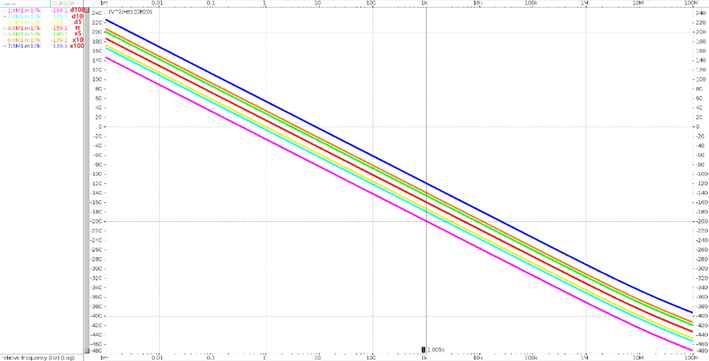

我们首先根据MOS器件的DC噪声数据,完成模型提取,以作为后续输入噪声水平的标准(下图红线)。已知在低频处,同一器件的AC噪声水平将低于其DC噪声水平,因此在标准曲线基础上,分别实现输入噪声水平的恶化和优化(输入噪声恶化5/10/100倍,输入噪声优化5/10/100倍)。

晶体管的不同噪声水平的噪声输入,NanoWave显示

搭建VCO仿真电路

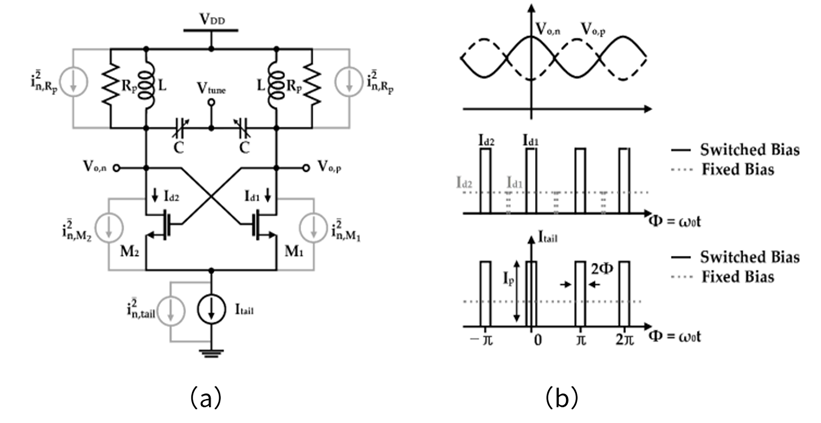

在仿真工作开始前,还需准备VCO工作电路的搭建。基于数学模型的理论分析表明,方波激励偏置技术通过对电流源进行调制,可以有效改善 VCO的相位噪声性能[1],这一结论可以通过脉冲灵敏度函数(ISF)理论加以解释[2]。基于上述理论,本文采用如下所示的拓扑结构搭建 VCO 电路。

基于脉冲调制电流源的VCO相位噪声改善机制[1]:

(a)差分LC-VCO示意图(b)VCO的输出电压和漏极电流以及脉冲调制电流源的偏置电流的概念波形

结果讨论

仿真结果验证

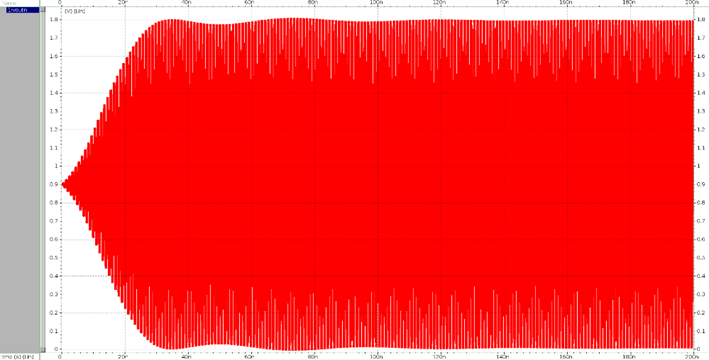

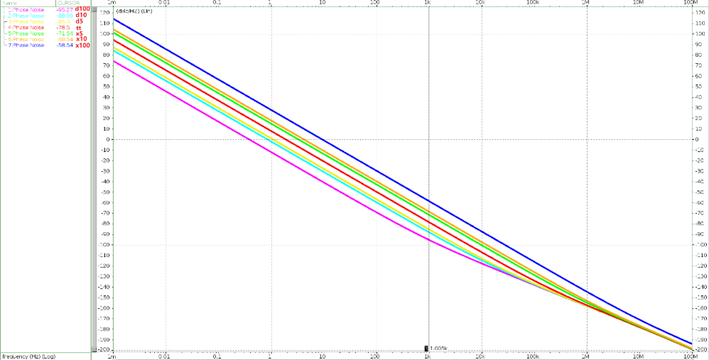

在完成噪声模型提取、VCO工作电路搭建后,即可进行电路级别仿真,并获取VCO电路的相位噪声。不同1/f噪声水平下的相位噪声图谱如下。

不同1/f噪声水平下的相位噪声

依据曲线可推算,fc约为100KHz。小于fc的低频段,每个decade约下降29dB;大于fc的高频段,每个decade约下降20dB。仿真结果的斜率变化与前述理论中VCO相位噪声三段式曲线吻合,符合预期。

偏移频率、输入电流噪声、相位噪声对应关系

相较于传统的DC偏置,基于9812AC交流激励条件下获取的器件1/f噪声本征值更低。而上述VCO电路仿真实践证实,在低频段(<1KHz),MOS器件输入噪声水平的降低对VCO电路的相位噪声具有显著的改善效果。

不同1/f噪声输入对应的相位噪声相对变化图谱

在VCO电路设计中,相位噪声水平不仅决定了信号的频谱纯度,还直接关联到系统整体性能上限。AC噪声模型能够还原电路更优的相位噪声水平,这种准确的物理描述,对于VCO等噪声敏感型射频电路具有重要意义。

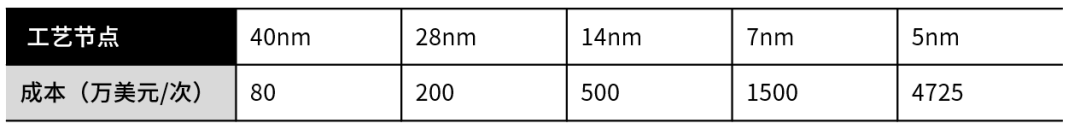

芯片流片成本参考

04

总结

噪声:从测试到建模仿真的一站式解决方案

参考文献

[1] Soltanian, B.; Kinget, P.R. Tail Current-Shaping to Improve Phase Noise in LC Voltage-Controlled Oscillators. IEEE J. Solid-StateCircuits 2006, 41, 1792–1802.

[2] Hajimiri, A.; Lee, T.H. A General Theory of Phase Noise in Electrical Oscillators. IEEE J. Solid-State Circuits 1998, 33,179–194.

扫码加微信,供需同分享