CPO光学封装技术详解:AI算力时代的封装革命

发布时间:2026-04-03来源:半导体在线

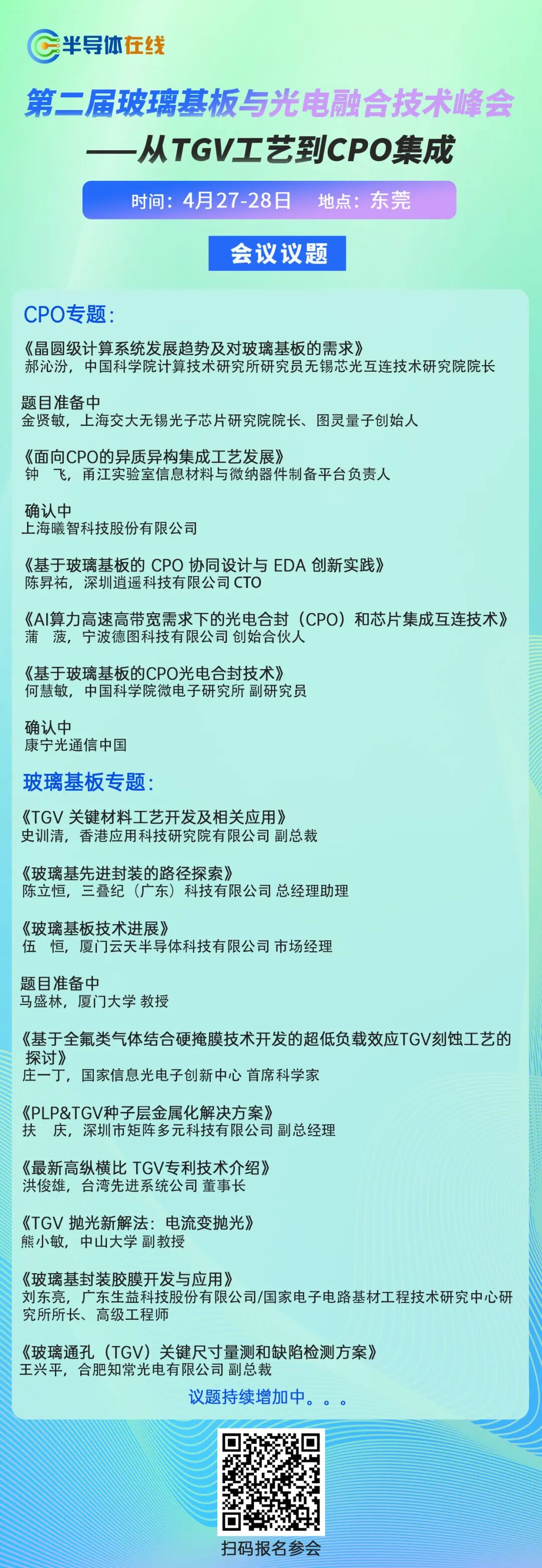

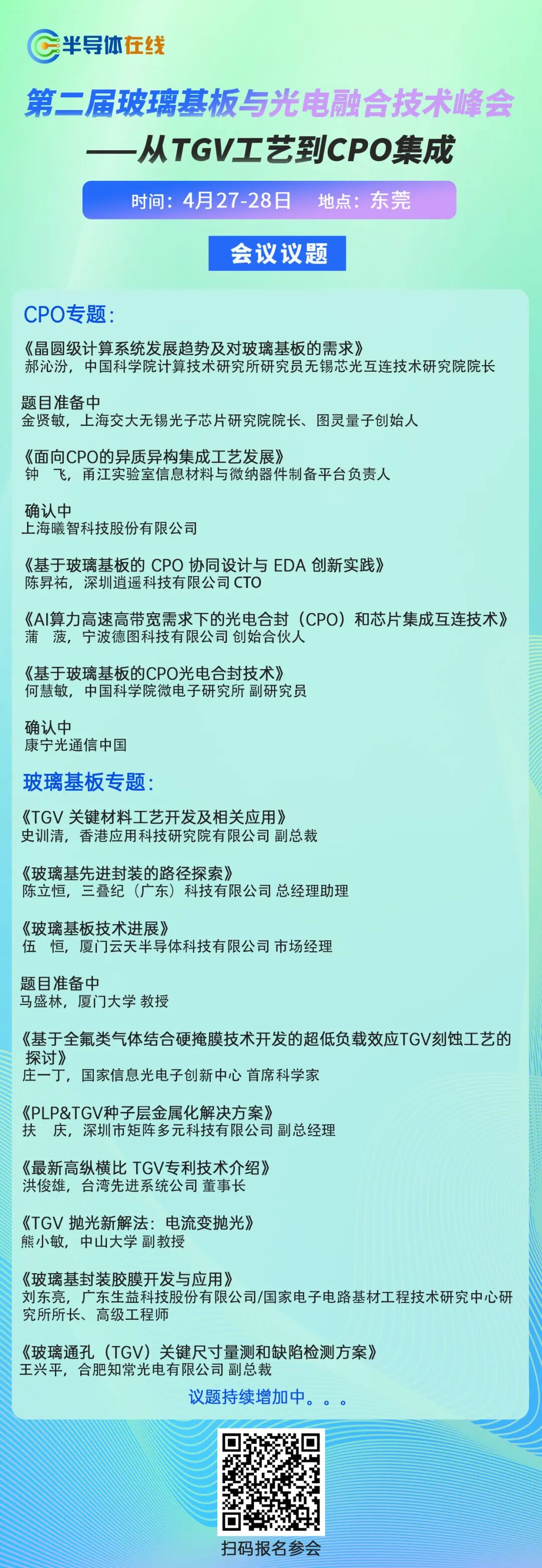

2026年第二届

玻璃基板与光电融合技术峰会

——从TGV工艺到CPO集成

随着英伟达Feynman芯片发布、CPO概念持续升温,越来越多人开始关注这项支撑AI算力突破的核心技术。但多数人对CPO的认知,仍停留在“光电共封装”的表面定义,对其光学封装的核心原理、技术细节、实现路径及产业落地难点知之甚少。今天,我们跳出“概念炒作”,深度拆解CPO光学封装技术——从核心定义、封装架构,到关键流程、技术难点,再到产业现状与未来演进,用通俗语言讲透这项改写光通信格局的“硬核技术”,看懂它为何能成为AI算力时代的必选项。一、核心定义:CPO光学封装,到底“封”的是什么?

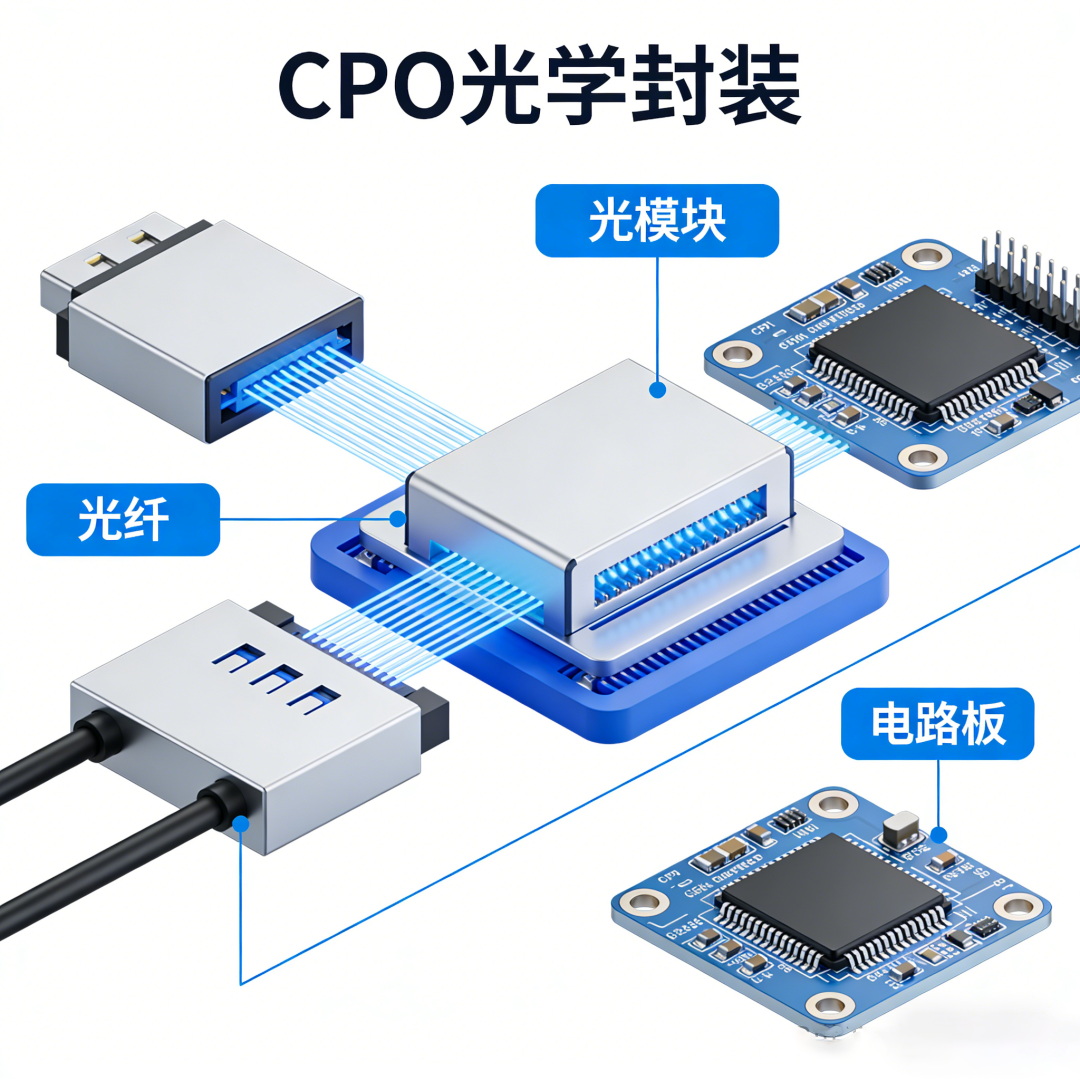

CPO(Co-Packaged Optics,光电共封装),本质是一种将光引擎(光学组件)与交换芯片(电组件)集成在同一封装基板上的先进光学封装技术,核心目的是解决传统光通信架构中“光电分离”带来的效率瓶颈。要理解CPO光学封装,首先要明确两个核心组件的角色,以及封装的核心逻辑:- 核心组件拆解:光引擎是“信号转换器”,由光发射模块(激光器、调制器)、光接收模块(探测器)、光耦合结构组成,负责电信号与光信号的相互转换;交换芯片是“信号调度中心”,负责数据的分发与路由,是AI数据中心的“算力枢纽”。

- 封装核心逻辑:传统架构中,光引擎(光模块)与交换芯片是“分离式布局”,通过长距离铜缆连接,相当于“异地办公”,信号传输过程中损耗大、延迟高、功耗高;而CPO光学封装,就是将两者“打包”在同一块基板上,实现“同桌协作”,将光电互连距离从厘米级缩短至百微米级,从根源上解决传统架构的痛点。

补充说明:CPO光学封装并非简单的“物理拼接”,而是通过先进的封装工艺,实现光学组件与电组件的精准耦合、信号协同,是“光、电、热”三位一体的系统工程,也是区别于传统光模块封装的核心所在。二、CPO光学封装的核心架构:3大核心组成,缺一不可

CPO光学封装的核心竞争力,源于其精密的架构设计。一套完整的CPO光学封装系统,主要由3部分组成,各部分协同工作,才能实现“低损耗、高带宽、低功耗”的核心优势,也是光学封装技术的核心难点所在。1. 封装基板:CPO的“承载底座”

封装基板是CPO光学封装的基础,相当于“承载平台”,负责固定光引擎、交换芯片,同时实现两者之间的电互连与光互连。其核心要求是“高精度、低损耗、高导热”——- 高精度:基板的线路精度需达到微米级,确保光引擎与交换芯片的引脚精准对接,避免信号偏移; - 低损耗:基板的电介质损耗需控制在极低水平,减少电信号传输过程中的能量浪费; - 高导热:基板需具备优异的导热性能,及时导出芯片与光引擎工作时产生的热量,避免高温影响封装可靠性。目前主流的CPO封装基板以硅基、陶瓷基为主,其中硅基基板凭借良好的兼容性和集成度,成为中高端CPO产品的首选,而台积电、英特尔等巨头正加速硅基基板的技术迭代与产能布局。2. 光互连结构:CPO的“信号通道”

光互连结构是CPO光学封装的核心,负责光信号的传输与耦合,相当于“光电沟通的桥梁”,其设计水平直接决定了CPO的信号损耗与传输效率。传统光模块的光互连的是“外部连接”,通过光纤与光模块接口连接,损耗较大;而CPO的光互连是“内部集成”,主要分为两种形式:- 芯片级光互连:将光引擎的光器件(激光器、探测器)直接集成在交换芯片表面,实现“芯片内光电互连”,损耗最低,但技术难度极高; - 基板级光互连:将光引擎与交换芯片分别固定在基板上,通过基板内部的光 waveguide(光波导)实现光信号传输,是目前主流的实现方式,兼顾性能与可量产性。关键难点:光互连的“精准耦合”——光信号的传输路径极细,耦合偏差哪怕是微米级,也会导致信号损耗大幅增加,因此需要高精度的封装设备与工艺,这也是CPO光学封装的核心技术壁垒之一。此外,外置激光源(ELS)方案的普及,进一步优化了光互连结构,降低了芯片侧的热管理难度,成为当前CPO技术的主流演进方向。3. 热管理系统:CPO的“降温神器”

热管理是CPO光学封装的“生命线”。光引擎中的激光器、交换芯片,工作时都会产生大量热量,而硅光器件对温度极其敏感(最佳工作温度需低于60℃),温度过高会导致光信号漂移、器件寿命缩短,甚至封装失效,因此高效的热管理系统必不可少。- 被动散热:通过高导热基板、散热片,将热量自然导出,适用于中低功率的CPO产品; - 主动散热:采用微通道液冷、热管散热等技术,主动带走热量,适用于高功率、高密度集成的CPO产品(如3.2T及以上速率的CPO光引擎)。例如,华工科技发布的3.2Tb/s液冷共封装光引擎,通过液冷散热方案,将集群电源使用效率(PUE)从1.25W降至1.12W,单机架算力密度提升40%,完美解决了高功率CPO的散热痛点。三、CPO光学封装关键流程:4步实现“光电共融”

CPO光学封装是一项精密的系统工程,从组件准备到最终封装完成,需经过4个核心步骤,每一步都对工艺精度有极高要求,也是决定CPO产品良率与性能的关键。第一步:组件预处理——对光引擎(激光器、调制器、探测器)、交换芯片进行清洗、测试,去除表面杂质,确保组件性能达标;同时对封装基板进行预处理,蚀刻线路、预留光互连通道,为后续组装做好准备。这一步的核心要求是“无杂质、高洁净”,避免杂质影响后续耦合精度。第二步:芯片贴装——通过高精度贴片机,将交换芯片、光引擎组件精准贴装在封装基板的预设位置,确保引脚对齐、贴合紧密。贴装精度需控制在±1微米以内,否则会导致电互连接触不良、光耦合偏差,影响产品性能。目前,长电科技、日月光等封测巨头,已在芯片贴装工艺上实现技术突破,可满足高端CPO产品的贴装需求。第三步:光电耦合与互连——这是CPO光学封装最核心、最复杂的一步。通过高精度耦合设备,将光引擎的光器件与基板上的光波导精准对接,实现光信号的高效传输;同时通过引线键合技术,实现交换芯片与光引擎、基板的电互连,确保电信号与光信号协同工作。耦合过程中,需实时监测信号损耗,调整耦合位置,直至损耗达到最低标准。第四步:封装封帽与测试——将贴装、耦合完成的组件,用封装外壳封帽,保护内部组件免受外界环境(灰尘、湿度)影响;随后进行全面测试,包括信号损耗、传输速率、功耗、温度稳定性等,筛选出合格产品。测试合格后,CPO光学封装产品方可进入下游应用环节。据摩根大通测算,目前CPO封装的良率仍有待提升,这也是制约其成本下降的关键因素之一。四、CPO光学封装的技术优势:为何能替代传统封装?

CPO光学封装之所以能成为AI算力时代的“香饽饽”,核心是其相比传统光模块封装,在性能上实现了全方位突破,精准破解了AI数据中心的核心痛点,具体优势集中在4点:- 损耗大幅降低,传输效率翻倍——传统光模块封装中,光信号需经过长距离铜缆传输,损耗高达25dB以上;而CPO光学封装将光电互连距离缩短至百微米级,信号损耗可控制在5dB以内,部分高端方案甚至能降至1-2dB,传输效率提升显著。以英伟达Spectrum-X平台为例,其CPO方案可将信号损耗从22dB降至4dB,大幅提升数据传输的稳定性与效率。

- 功耗显著下降,告别“电老虎”——传统可插拔光模块的功耗主要消耗在长距离电信号传输与信号补偿上,而CPO光学封装减少了长距离铜缆的使用,降低了信号补偿的能耗。据Cisco统计,对比传统可插拔方案,CPO能让ASIC连接光模块的功耗最多降低50%,51.2T交换机总功耗降低25%-30%;英伟达Feynman芯片凭借CPO相关技术,更是将AI数据中心通信能耗降低70%以上,每比特功耗仅约5皮焦,远低于传统光模块的15皮焦,对于超大规模AI数据中心来说,每年能节省巨额电费。

- 带宽密度提升,适配高速需求——CPO光学封装通过高密度集成,突破了传统封装的空间限制,单位面积的带宽密度实现数量级提升,可达到每平方毫米1太比特以上。目前,CPO已能支撑800G规模化商用、1.6T量产,未来还能适配3.2T及更高速率,完美匹配AI集群、超算中心的海量数据传输需求,而传统封装方案很难突破带宽瓶颈。博通推出的51.2T CPO以太网交换机,已实现全部I/O光化,充分体现了CPO的高密度优势。

- 体积缩小,集成度更高——将光引擎与交换芯片封装在同一块基板上,相比传统“分离式封装”,CPO产品的体积可缩小30%以上,能节省数据中心的机柜空间,提升机柜的算力密度。对于空间紧张的超大规模AI数据中心来说,这一优势尤为重要,可有效降低数据中心的建设成本与运营成本。

五、技术难点与产业现状:CPO光学封装的“成长烦恼”

尽管CPO光学封装优势显著,且已迎来产业拐点,但目前仍处于“从技术验证到规模商用”的关键阶段,面临着诸多技术难点与产业挑战,主要集中在3个方面:- 技术难点:封装精度与热管理是核心瓶颈——一方面,光电耦合的精度要求极高(±1微米以内),对封装设备、工艺的要求远超传统封装,目前全球能掌握高精度CPO封装技术的企业寥寥无几;另一方面,光引擎与交换芯片的高热流密度,对热管理系统提出了更高要求,尤其是高密度集成的CPO产品,如何实现高效散热、避免温度漂移,仍是行业亟待解决的难题。外置激光源(ELS)方案的应用,虽在一定程度上缓解了热管理压力,但也增加了封装复杂度。

- 产业挑战:良率偏低,成本居高不下——CPO光学封装的工艺复杂,涉及多个环节的精准协同,任何一个环节出现偏差,都会导致产品失效,因此目前行业整体良率偏低(低于70%)。良率偏低直接推高了CPO产品的成本,目前CPO产品的价格是传统可插拔光模块的2-3倍,制约了其规模化应用。不过,随着英伟达等巨头的布局、封装工艺的成熟,以及量产规模的扩大,CPO的良率与成本有望逐步改善,摩根大通预测,2027年CPO将进入规模化转折期,成本将大幅下降。

- 生态挑战:产业链协同不足,标准尚未统一——CPO光学封装颠覆了传统光模块的供应链体系,需要芯片厂商(交换芯片)、光器件厂商(光引擎)、封装厂商、设备厂商深度协同,而目前行业内尚未形成统一的技术标准与协同机制,不同企业的产品兼容性较差。此外,CPO的核心器件(如高端激光器、硅光芯片)仍有部分依赖进口,国内企业在核心技术上仍需突破,尤其是在高端光引擎封装领域,与海外巨头仍有差距。不过,国内企业正加速追赶,华工科技、中际旭创等企业已推出相关产品,逐步打破海外技术垄断。

六、未来演进:CPO光学封装的3大发展方向

随着AI算力的持续爆发、技术的不断迭代,CPO光学封装将朝着“更高集成度、更高速率、更低成本”的方向演进,未来主要有3个发展趋势,将进一步巩固其在光通信领域的核心地位:- 集成度持续提升:从“基板级封装”走向“芯片级封装”——未来,CPO光学封装将逐步实现光引擎与交换芯片的“芯片级集成”,将光器件直接嵌入交换芯片内部,进一步缩短光电互连距离,降低损耗、提升效率。同时,多芯片集成(Chiplet)技术将与CPO深度融合,实现“多芯片+光互连”的一体化封装,适配更高算力的AI集群需求,华工正源已在这一方向实现突破,其CPO光引擎采用硅光集成与Chiplet架构,为向6.4T演进预留了架构空间。

- 速率持续升级:向3.2T、6.4T甚至更高速率演进——目前1.6T CPO已进入量产阶段,未来3-5年,3.2T CPO将实现规模化商用,6.4T及更高速率的CPO产品将逐步落地,以满足AI大模型、超算、6G等领域的超高带宽需求。LightCounting预测,到2029年,3.2T CPO端口出货量预计超过1000万个,成为行业主流产品。

- 成本持续下降:规模化量产+技术成熟,推动普及——随着封装工艺的成熟、良率的提升,以及英伟达等巨头的规模化采购,CPO产品的成本将逐步下降,预计未来2-3年,CPO的成本将与传统高端光模块持平,逐步替代传统可插拔光模块,成为AI数据中心、超算中心的主流封装方案。同时,CPO的应用场景将从AI数据中心延伸至智能驾驶、工业互联网等领域,市场空间持续扩大。据预测,到2030年,CPO核心组件市场规模将达150亿美元,占光互联市场的20%,成为行业增长的核心引擎。

结语:光学封装革命,重构AI算力底层逻辑

CPO光学封装技术的崛起,并非偶然,而是AI算力爆发与光通信技术迭代共振的结果。它不仅是一项“封装技术”的升级,更是一场重构光通信架构、破解AI算力瓶颈的革命——通过“光电共融”,打破了传统“光电分离”的局限,实现了“低损耗、高带宽、低功耗”的核心目标,成为支撑AI时代发展的底层基石。目前,CPO光学封装仍面临技术、良率、成本等多重挑战,但随着全球巨头的加速布局、国内企业的技术突破,以及产业链的逐步完善,其规模化商用的步伐正在加快。未来,随着CPO技术的不断成熟,它将彻底改变光通信行业的格局,为AI、超算、6G等领域的发展注入新的动力。来源:Bill Tang技术支持

点击左下方阅读原文,立即报名第二届玻璃基板与光电融合技术峰会!

点击左下方阅读原文,立即报名第二届玻璃基板与光电融合技术峰会!

转载说明:本文系转载内容,版权归原作者及原出处所有。转载目的在于传递更多行业信息,文章观点仅代表原作者本人,与本平台立场无关。若涉及作品版权问题,请原作者或相关权利人及时与本平台联系,我们将在第一时间核实后移除相关内容。