光子封装黄金时代:技术谱系全面升级,2031年规模剑指144亿美元!

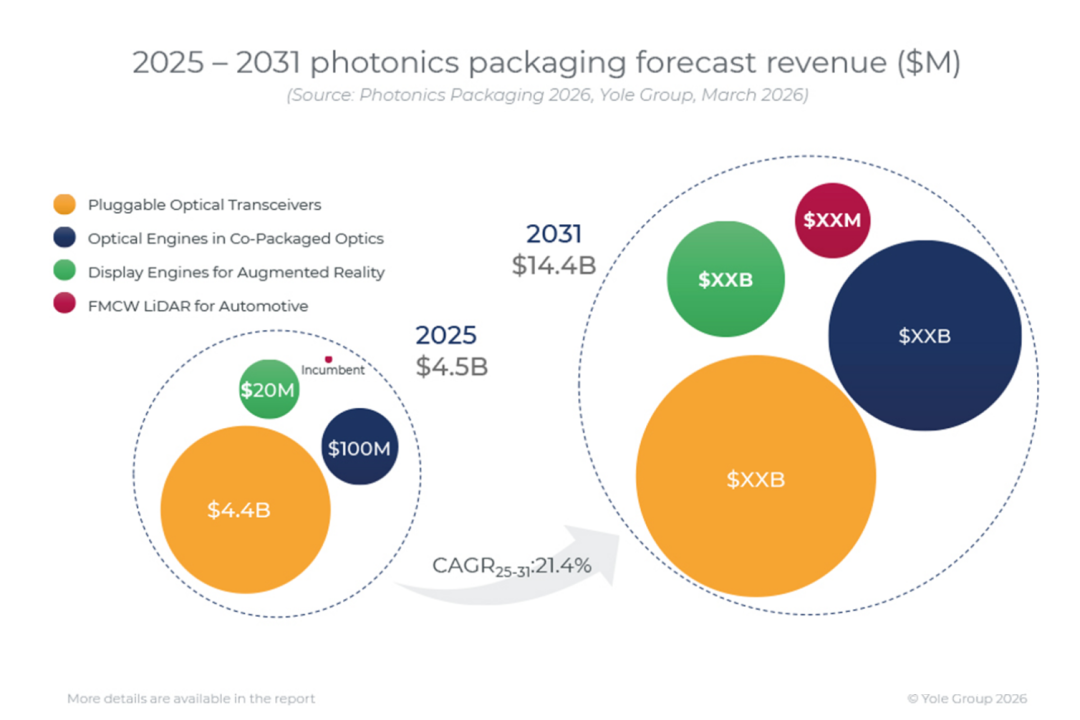

随着人工智能大模型训练与推理算力需求呈指数级爆发,传统电互联在带宽、功耗与延迟上的瓶颈日益凸显,光子封装正从光通信配套环节跃升为算力基础设施的核心支撑。全球领先的科技行业分析机构Yole Group发布的《2026年光子封装》(Photonics Packaging 2026)报告显示,受AI数据中心、高性能计算(HPC)等场景的强劲驱动,全球光子封装市场将迎来结构性增长,预计从2025年的约45亿美元,以超21%的年复合增长率(CAGR)扩张,到2031年达到144亿美元,六年内市场规模增长三倍。

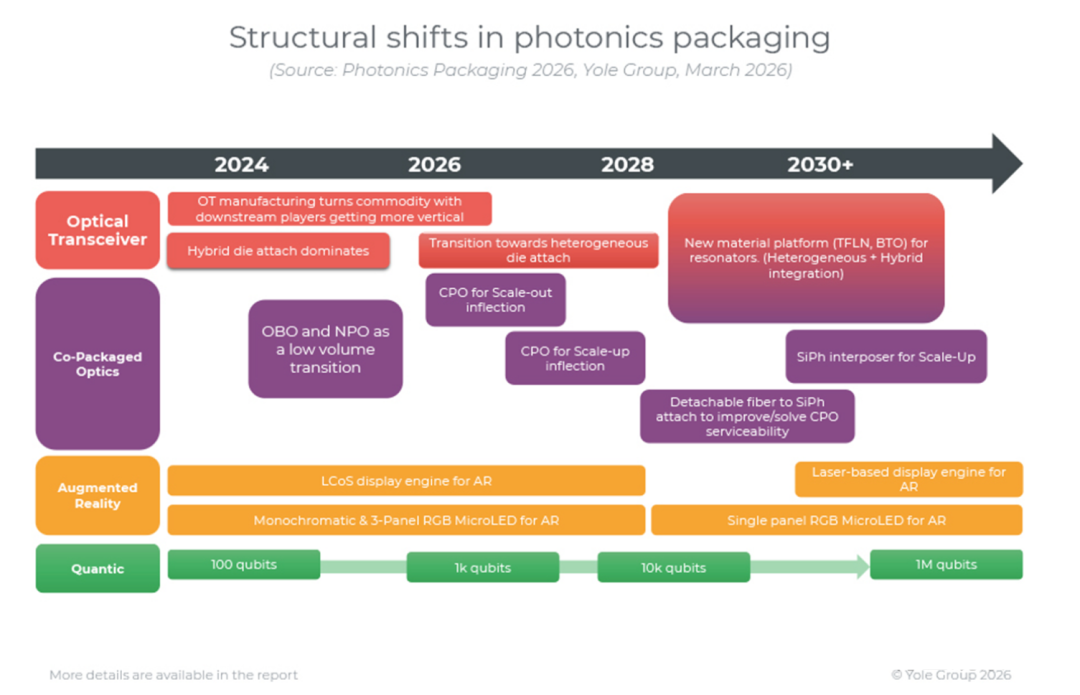

Yole Group的分析师在报告中明确指出,人工智能数据中心对光收发器和共封装光器件(CPO)的需求不断增长,将成为市场大幅增长的核心驱动力。值得关注的是,当前光子封装年产值已达45亿美元,这一规模几乎完全与可插拔收发器需求相关,AR/VR、自动驾驶、量子计算等其他场景的应用才刚刚浮出水面,未来增长潜力巨大。结合现阶段人工智能发展的趋势,光子封装正正式进入结构性增长阶段——该市场过去长期以数据通信和电信用光收发器为主,如今正受到人工智能驱动的带宽需求、CPO的兴起以及光子学和先进半导体封装融合的三重重塑,产业格局迎来根本性变革。

报告进一步分析认为,随着光与逻辑的距离越来越近,光子封装架构正朝着2.5D、3D集成、光子集成电路(PIC)和电子集成电路(EIC)的异构集成以及更紧密的光纤到芯片耦合方案演进。这种技术转变不仅大幅增加了封装的复杂性,更显著提升了其在整个半导体产业链中的战略价值,同时将创新重心推向了设计和平台级集成的上游,推动光子封装从“后端制造环节”向“前端核心技术”转型。

光子封装:算力时代的“光互联基石”,技术谱系全面升级

光子封装是实现光子集成电路(PIC)、电子集成电路(EIC)、光引擎与光纤高效耦合、稳定互联的关键工艺,其核心目标是在保证光学耦合精度、信号完整性的前提下,实现更高集成度、更低功耗与更优成本。当前,光子封装已形成覆盖从传统分立封装到先进异质集成的完整技术谱系,主流技术路径及核心优势如下,且不同技术路径的迭代的背后,正是AI算力需求与产业升级的必然推动。

(一)传统分立封装:成熟稳定,适配中低速场景

传统分立封装是光子封装的基础形态,目前仍在中低速光模块领域发挥重要作用,也是当前45亿美元市场规模的核心支撑,其需求主要集中在传统数据通信与电信领域的可插拔收发器。

1. TO-CAN封装(Transistor Outline Can)

技术特点:最经典的光器件封装形式,采用金属管壳密封,将激光器、探测器等光芯片与热敏电阻、TEC(半导体制冷器)集成于一体,通过引脚与外部电路连接,光纤通过尾纤耦合输出。

核心优势:工艺成熟、成本低廉、可靠性高、散热性能好,可满足-40℃至85℃的工业级环境要求,是10G及以下速率光模块的主流选择,目前在中低速可插拔收发器中仍有广泛应用。

应用局限:封装体积大、集成度低,高频信号损耗大,无法适配40G及以上高速率场景,随着AI驱动的高速率需求爆发,正逐步被先进封装替代。

2. COB封装(Chip-on-Board,板上芯片)

技术特点:将光芯片直接贴装在PCB或陶瓷基板上,通过金丝键合实现电气互联,光纤通过耦合结构与芯片波导对接,省去传统管壳,实现裸芯片级集成。

核心优势:体积较TO-CAN缩小50%以上,成本降低30%-40%,信号传输路径更短,可支持40G-100G速率,是中低速光模块的主流升级方案,也是当前可插拔收发器封装的重要补充。

技术挑战:光学耦合对准精度要求高(±1μm),良率控制难度大,散热与防潮性能依赖基板与封装工艺,难以满足AI数据中心对高速率、高可靠性的极致需求。

(二)先进集成封装:面向高速率、高集成,支撑AI算力需求

随着AI大模型对带宽、功耗的极致追求,先进集成封装成为产业发展的核心方向,也是Yole报告中预测的未来六年增长主力。这类技术以更高集成度、更低损耗、更优能效为核心优势,支撑CPO、硅光芯片等前沿产品落地,推动光子封装与先进半导体封装深度融合。

1. 倒装焊封装(Flip Chip)

技术特点:光芯片与电芯片通过凸点(Bump)面对面贴装,实现芯片间的高密度互联,取代传统引线键合,大幅缩短信号路径,契合“光与逻辑距离拉近”的产业趋势。

核心优势:高频信号损耗低、热稳定性优异、集成密度高,可支持200G-800G光模块,是当前高速率可插拔光模块的主流封装工艺,2023年全球市场规模达78亿美元,也是未来可插拔收发器向更高速率升级的核心支撑技术。

技术演进:从传统焊料凸点向铜柱凸点、混合键合(Hybrid Bonding)升级,进一步提升互联密度与散热能力,适配PIC与EIC异质集成的需求,为CPO技术落地奠定基础。

2. 晶圆级封装(Wafer-Level Packaging,WLP)

技术特点:在晶圆片上完成光芯片的光学耦合、电气互联与密封保护,切割后直接形成单颗封装器件,实现“晶圆级批量制造”,是降低封装成本、提升量产效率的关键技术。

核心优势:极致小型化、成本最优(批量生产摊薄工艺成本)、一致性好,可实现PIC与EIC的晶圆级异质集成,适配硅光芯片规模化量产,预计2030年市场规模达65亿美元,将成为AR、激光雷达等新兴场景封装的核心方案。

应用场景:硅光收发器、激光雷达芯片、AR显示引擎等对体积与成本敏感的领域,尤其在AR领域,晶圆级封装可支撑超紧凑型光学引擎的实现,成为产品性能与外形的关键差异化因素。

3. 2.5D/3D异质集成封装

技术特点:2.5D封装通过硅中介层(Silicon Interposer)实现PIC与EIC的高密度互联,利用TSV(硅通孔)实现垂直电气连接;3D封装则通过TSV与微凸点技术,将光电芯片垂直堆叠,实现“三维立体集成”,是Yole报告中强调的架构演进核心方向。

核心优势:互联距离最短(微米级)、带宽密度最高、功耗最低,可支持1.6T/3.2T及以上超高速率,是CPO技术的核心载体,完美适配AI数据中心的极致性能需求,也是光子学与先进半导体封装融合的核心体现。

技术壁垒:TSV制造、高精度对准、异质材料热应力匹配、散热设计等难度极高,目前仅台积电、英特尔、日月光等头部厂商具备规模化能力,而这种高壁垒也进一步提升了先进封装的战略价值。

4. 共封装光学(CPO,Co-Packaged Optics)——下一代主流方向

技术定义:将光引擎(含激光器、调制器、探测器、波导等)与交换ASIC、GPU等计算芯片直接集成在同一封装基板上,实现“光电共封”,两者间距小于5厘米,信道损耗低于10分贝,是“光与逻辑近距离融合”的终极形态之一。

核心优势:Yole分析师认为,CPO正处于一个关键的转折点,这既受到带宽扩展需求的驱动,也受到能源效率要求的制约。其核心优势集中在三个方面:一是极致带宽,支持单端口1.6T/3.2T速率,满足AI集群百万GPU互联的带宽需求;二是超低功耗,较传统可插拔模块功耗降低40%-50%,较NPO(近封装光学)降低20%-30%,破解数据中心“功耗墙”难题,这也是AI算力扩张的核心诉求;三是超高集成,省去光模块外壳与PCB走线,交换机端口密度提升3倍以上,适配AI数据中心高密度部署。

技术形态:分为2D(芯片并排)、2.5D(中介层互联)、3D(垂直堆叠)三种,其中2.5D CPO是当前商用化主流,3D CPO为长期演进方向,而要实现这些技术,就需要先进的半导体制造能力来支持业内一些要求较高的工艺流程。

(三)近封装光学(NPO,Near-Packaged Optics)——过渡性方案

技术特点:光引擎制成独立可插拔模块,通过Socket固定在主板上,距离ASIC约5-15厘米,高速信号通过PCB短走线传输(≤150毫米),是可插拔模块向CPO过渡的中间形态。

核心优势:兼顾性能与可维护性,光引擎可热插拔更换,良率与量产难度低于CPO,是800G向1.6T过渡的主流方案,将在2026-2027年达到市场峰值,随后逐步被CPO替代,成为CPO规模化落地前的重要补充。

Yole报告:AI驱动市场爆发,CPO成增长核心引擎

Yole Group在报告中系统拆解了光子封装市场的增长逻辑、结构与趋势,结合AI产业发展现状,明确了光子封装的结构性增长特征,其中CPO作为核心增长引擎,将主导未来六年的市场扩张,同时新兴场景的崛起将进一步拓宽市场边界。

(一)市场规模:六年增三倍,2031年达144亿美元

Yole报告明确给出核心数据:当前(2025年)全球光子封装市场规模约45亿美元,这一规模几乎完全由数据通信与电信领域的可插拔光收发器驱动,其中数据通信领域封装价值占比约25%,电信领域约20%,其他场景贡献微乎其微。

图源:Yole Group

增长预测方面,2025-2031年全球光子封装市场将以超21%的年复合增长率(CAGR)扩张,到2031年达到144亿美元,六年内市场规模增长三倍,成为半导体封装领域增速最快的细分赛道之一。这一增长主要得益于AI数据中心的爆发式需求,尤其是CPO与高速可插拔收发器的规模化应用。

价值占比变化上,CPO市场中,光子封装价值占比将在2026-2027年达到拐点,峰值约50%;随后随着硅光子芯片成熟,封装工艺的标准化与规模化,到2031年回落至35%左右,但绝对规模仍持续扩张,凸显其核心增长地位。

(二)市场结构:CPO与可插拔互补,多场景协同增长

Yole方面预测,到2031年,全球光子封装市场将形成“CPO主导、可插拔支撑、新兴场景补充”的多元结构,不同细分领域协同发力,推动市场整体增长,其中各细分场景的规模预测已形成明确格局。

1. 可插拔光收发器:稳健增长,基本盘稳固

尽管CPO快速崛起,但可插拔光模块市场仍将保持稳健增长,2031年将贡献约80亿美元的光子封装需求,占总市场的55%以上,仍是市场的核心支撑。其驱动因素主要包括云计算、5G/6G、边缘计算的持续扩容,以及中低速光模块的存量替换与增量需求,同时高速可插拔模块(如800G、1.6T)的升级也将持续贡献封装价值。

2. CPO:从0到1,爆发式增长

作为市场增长的核心引擎,CPO驱动的封装需求将实现跨越式增长——2025年CPO封装需求几乎为零,2031年将飙升至约50亿美元,占总市场的35%,成为第一增长动力。关键拐点将出现在2026-2027年,随着英伟达、博通、Marvell等厂商CPO方案商用化,市场将进入规模化落地阶段。其中,英伟达Spectrum-X、Quantum-X等CPO交换机率先商用,将推动1.6T CPO成为AI数据中心标配,而硅光子学对于提供下一代数据中心所需的带宽和能源效率至关重要,将进一步加速CPO的落地进程。

3. 新兴场景:贡献增量,拓展市场边界

除了AI数据中心与传统通信领域,光子封装正逐步拓展到新的领域,成为市场增长的重要补充。Yole预测,到2031年,这些新兴场景将贡献约16.75亿美元的封装需求,其中增强现实(AR)显示引擎有望带来15亿美元的收入,用于自动驾驶汽车的调频连续波(FMCW)激光雷达将达到1.75亿美元,并且未来还会产生更多用途。

具体来看,在AR领域,微型LED混合、CMOS背板集成和超紧凑型光学引擎使封装成为外形尺寸和性能的关键差异化因素,京东方等企业已在MicroLED封装领域取得突破,通过创新封装方案提升光效,支撑AR设备的小型化与高性能化;在自动驾驶领域,FMCW激光雷达作为实现真4D感知的理想方案,其规模化量产依赖先进的光子封装技术,瑞士Pointcloud GmbH公司已研发出超60万个光子器件大规模集成的纯固态FMCW激光雷达焦平面阵列芯片,推动激光雷达封装技术升级;在量子技术中,无论是基于光子、离子还是原子,超低损耗光纤对准、高密度激光集成和极高精度组装都重新定义了封装要求,Xanadu、Senko等企业已推出针对性的量子光子封装方案,推动量子技术从实验室走向商业化。

(三)核心驱动:AI算力需求是根本动力

Yole报告明确指出,人工智能行业的爆发式发展是光子封装市场实现结构性增长的根本原因,其核心驱动逻辑集中在带宽刚需、功耗约束与架构升级三大方面,这也决定了光子封装的技术演进方向。

1. 带宽刚需:AI大模型训练需要百万GPU集群互联,传统铜互联仅支持100G-400G速率,且功耗极高;光互联可实现1.6T/3.2T超高速传输,是唯一能满足AI集群带宽需求的解决方案,而光子封装作为光互联的核心环节,直接决定了带宽的上限与稳定性。

2. 功耗约束:数据中心功耗已成为全球算力发展的核心瓶颈,尤其是AI大模型训练的耗电量极高,CPO较传统方案功耗降低50%以上,可将数据中心PUE(电源使用效率)从1.5降至1.2以下,符合“绿色算力”发展趋势,这也是AI数据中心选择CPO方案的核心考量之一。

3. 架构升级:AI数据中心从“Scale-out(横向扩展)”向“Scale-up(纵向扩展)”演进,需要更紧密的光电集成,而CPO、2.5D/3D异质集成等封装技术,正是实现光电紧密互联的核心载体,完美适配这一架构变革,推动光子封装与先进半导体封装的深度融合。

技术演进与产业挑战:从实验室到规模化,突破三大核心瓶颈

随着光子封装进入结构性增长阶段,技术迭代速度持续加快,同时产业规模化落地也面临诸多挑战。Yole报告指出,了解CPO的生态系统、技术挑战和市场动态,对于充分发挥其增长潜力至关重要,而整个光子封装产业的发展,也需要突破一系列核心技术与产业瓶颈。

(一)核心技术突破方向

1. 光学耦合技术:从边缘耦合、光栅耦合向混合耦合、倏逝耦合升级,核心目标是降低插入损耗(目标<1dB)、提升对准容差(目标>5μm),适配晶圆级批量制造,解决硅光波导与光纤模场尺寸不匹配的难题,这也是硅光芯片封装的核心技术瓶颈之一。目前,行业内主要通过设计端面耦合器或光栅耦合器来缓解这一问题,提升耦合效率。

2. 异质集成工艺:突破硅、磷化铟(InP)、锗(Ge)等异质材料的键合与热应力匹配难题,实现PIC与EIC的高密度、高良率集成。由于硅材料本身不发光,制造过程中需要通过外延生长或异质键合技术,将InP等III-V族材料制成的激光器集成到硅基底上,这一过程对封装工艺的精度要求极高,也是制约CPO良率的关键因素。

3. 散热与可靠性:开发微流控散热、石墨烯散热等先进方案,解决CPO中光芯片与电芯片的共热问题;提升封装气密性与抗振动能力,满足数据中心20年以上使用寿命要求。同时,在量子、AR等新兴场景中,还需要满足超低损耗、超高稳定性的封装要求,进一步推动封装技术的升级。

4. 标准化与平台化:推动CPO接口、封装工艺、测试方法的标准化,解决不同厂商方案兼容性差的问题;构建平台级集成能力,将创新推向设计上游,提升封装的战略价值,推动光子封装与半导体设计、制造的深度融合。

图源:Yole Group

(二)产业面临的三大挑战

1. 良率与成本:CPO涉及高精度光学对准与复杂异质集成,当前良率低于70%,导致成本居高不下,规模化量产需良率提升至90%以上。同时,硅光芯片、高速光引擎等核心器件的成本较高,也进一步推高了光子封装的整体成本,制约了其在中低端场景的应用。

2. 供应链成熟度:硅光芯片、高速光引擎、先进封装基板、TSV中介层等核心环节依赖海外厂商,国内供应链尚处于突破阶段。例如,国内头部光模块厂商的高端硅光芯片流片高度依赖海外代工厂,国内虽有中试线和部分量产线,但在工艺稳定性和良率爬坡上仍需时间沉淀;CPO所需的高端调制器、探测器等器件,国产化率也有待提升。

3. 标准与生态:CPO接口、封装工艺、测试方法尚未形成统一标准,不同厂商方案兼容性差,制约生态快速成熟。同时,光子封装与半导体制造、光学器件、计算芯片等领域的协同不足,生态构建仍需完善,这也影响了CPO等先进技术的规模化落地速度。

全球格局与中国机遇:国产替代加速,抢占算力时代制高点

随着光子封装市场的爆发式增长,全球产业竞争日趋激烈,海外龙头率先布局核心技术并实现商用化,而国内厂商也在加速追赶,依托国内庞大的AI算力市场需求,推动国产替代进程,迎来重要发展机遇。

(一)全球竞争格局

海外领先:台积电、英特尔、博通、英伟达、Luxtera(思科)、II-VI等厂商在CPO、2.5D/3D集成、硅光封装等领域占据技术与市场主导地位,率先实现商用化。其中,台积电的COUPE硅光整合平台预计2026年进入量产,整合3D晶圆堆栈的SoIC技术,被视为CPO商业化关键里程碑;英伟达推出的Spectrum-X CPO交换机,通过台积电CoWoS封装技术,实现了带宽密度提升10倍,传输能耗降低90%,引领CPO技术商用化进程。

中国追赶:中际旭创、新易盛、光迅科技、长光华芯、通富微电、长电科技等国内厂商在可插拔光模块封装、COB、倒装焊等领域已实现全球领先;在CPO、硅光异质集成等前沿领域加速突破,部分厂商已推出1.6T CPO验证样品,其中中际旭创的1.6T CPO已批量出货给英伟达,新易盛LPO模块市占率达75%,获英伟达认证并批量交付;罗博特科斩获约6亿元硅光耦合设备订单,成为英伟达、博通核心供应商,国产厂商在光子封装领域的竞争力持续提升。

(二)中国产业机遇

1. 政策加持:国家“十四五”规划将光通信、光子技术列为战略性新兴产业,多地出台专项政策支持光子封装研发与产业化;国内“东数西算”等政策要求智算中心核心器件国产化率≥70%,推动上游核心器件与封装技术的国产替代。

2. 市场红利:中国是全球最大的AI算力基础设施建设市场,三大运营商、互联网巨头、云厂商加速布局CPO与硅光方案,为国内厂商提供巨大应用场景。同时,国内AR、自动驾驶、量子计算等新兴场景的快速发展,也为光子封装提供了广阔的市场空间。

3. 技术突破:国内在硅光芯片、混合键合、晶圆级封装等领域已实现多项核心技术突破,逐步打破海外垄断。例如,长光华芯、亨通光电联合建设8英寸90nm硅光芯片量产线,加速硅光芯片国产替代;光库科技已掌握薄膜铌酸锂调制器核心技术,可开发800Gbps及以上速率的芯片;京东方在MicroLED封装领域取得突破,为AR场景提供技术支撑,国产替代空间广阔。

未来展望:光子封装开启“光计算”新纪元

Yole Group在报告最后强调,光子封装的爆发不仅是光通信产业的升级,更是半导体行业从“电时代”向“光时代”跨越的关键标志。随着AI算力持续增长、CPO规模化落地、硅光技术成熟,光子封装将深度融入计算、通信、传感、显示等全领域,成为支撑数字经济与智能社会的核心底层技术。

从技术演进来看,未来光子封装将持续朝着“更紧密集成、更低损耗、更低功耗、更高良率”的方向发展,2.5D/3D异质集成将成为主流架构,CPO将逐步替代NPO成为AI数据中心的核心方案,晶圆级封装将在新兴场景中实现广泛应用;同时,光子封装与半导体制造、光学器件、计算芯片的融合将更加深入,创新将持续向设计与平台级集成上游延伸,进一步提升其战略价值。

从市场格局来看,未来六年全球光子封装市场将实现三倍增长,2031年规模达144亿美元,CPO与新兴场景将成为核心增长动力,市场竞争将从技术竞争转向生态竞争。海外龙头将持续巩固技术优势,而国内厂商有望依托市场红利与政策支持,加速核心技术突破与供应链完善,实现国产替代的跨越式发展。

对于中国半导体产业而言,光子封装是实现“换道超车”的重要机遇。建议国内厂商聚焦CPO、硅光异质集成等前沿方向,加强产学研协同,突破核心技术瓶颈,完善供应链生态,抢占全球光子封装产业制高点,为中国AI算力基础设施建设与数字经济发展提供坚实支撑。

【结语】 从45亿美元到144亿美元,六年增长三倍,AI驱动的光子封装市场正迎来前所未有的黄金时代。这不仅是一组数据的跃升,更是全球算力基础设施重构的时代信号——光子封装正从传统光通信的配套环节,跃升为AI算力时代的核心支撑,推动半导体产业进入“光电融合”的全新阶段。随着技术不断突破与产业生态成熟,光子封装将彻底打破电互联的物理极限,开启“光计算”的全新篇章,重塑半导体产业的未来格局,也为中国半导体产业实现高质量发展提供了重要契机。

2026先进半导体封装技术与应用论坛(CASPF 2026)

为更好的推动国内先进半导体封装技术与应用交流,在第三代半导体产业技术创新战略联盟(CASA)指导下,江南大学、极智半导体产业网和第三代半导体产业联合主办,将于2026年5月15-17日举办“2026先进半导体封装技术与应用论坛(CASPF 2026)”。论坛内容将围绕硅、碳化硅、氮化镓等集成电路封装技术,涉及先进半导体材料,器件,封装工艺、装备、制造、应用等相关主题,邀请产业链相关专家、高校科研院所及知名企业代表共同深入探讨,追踪先进半导体封装最新技术进展,分享应用及相关生态链构建发展,携手促进先进半导体封装技术协同发展。——CASPF2026 首批嘉宾揭晓!江大先进半导体封装技术与应用论坛邀您5月共赴江南之约!

来源:Yole Group、半导体产业网 整理,仅供参考

—— 完 ——

CASPF2026 | 首批嘉宾揭晓!江大先进半导体封装技术与应用论坛邀您5月共赴江南之约!

聚势共赴!2026功率半导体器件与集成电路会议(CSPSD2026)邀您6月相约上海

一图看懂氮化镓GaN在英伟达AI数据中心里的应用

划重点!“十五五”规划纲要:加快宽禁带半导体产业提质升级,推动超宽禁带半导体产业化发展

启动申报|2026功率半导体器件与集成电路会议(CSPSD 2026)优秀功率半导体产品征集活动

宇树科技IPO获受理 加速氮化镓器件在机器人赛道渗透

AI算力狂飙!GaN/SiC撑场,英伟达牵头800V HVDC,开启数据中心供配电革命!

【赞助、展示及商务合作】

张女士:13681329411 贾先生:18310277858