一文看懂!台积电为何要用SiC中介层?

最近,《2026碳化硅(SiC)衬底与外延产业调研白皮书》正在进行紧锣密鼓的调研工作。我们在走访企业中了解到,台积电已经向部分企业提出较为明确的12英寸中介层SiC衬底需求,今年将开启交付,而且明年的需求预期量将翻倍增长。

值得思考的是,台积电明知12英寸SiC衬底成本很高,SiC加工技术也存在一定挑战,但仍连续多年研发SiC中介层,这背后的考量值得我们好好分析。因此,“行家说三代半”今天将试图站在台积电的角度去思考:

为什么台积电要探索SiC中介层路线?

台积电的CoWoS封装遇到了什么难题?

SiC中介层可以帮助台积电解决哪些问题?

同时,我们还将深入解读CoWoS和SiC中介层技术,为先进封装企业与碳化硅衬底厂商在技术协同上提供一些参考:

先进封装为什么需要中介层?

中介层是什么?有哪些类型的中介层?

CoWoS-S和CoWoS-L的工艺流程是怎样的?

SiC在CoWoS-S和CoWoS-L中的应用价值是什么?

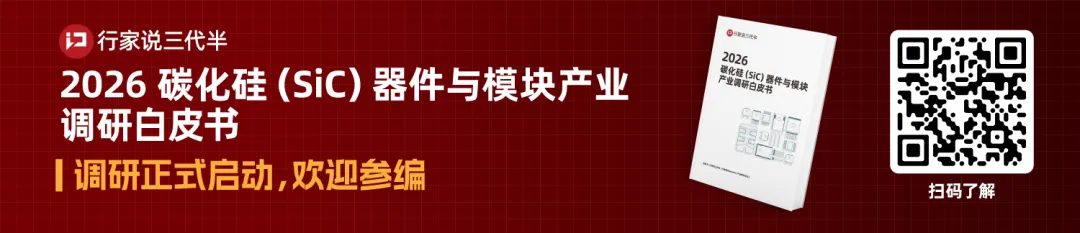

芯片封装大致可简单分为2D封装、2.5D封装与3D封装。

2D封装、2.5D封装和3D封装对比 来源:台积电

现阶段,GPU、ASIC等AI加速器通常采用基于中介层的2.5D封装,与HBM内存等集成构成HPC芯片组,这主要有两个原因。

首先,传统PCB难以满足要求。

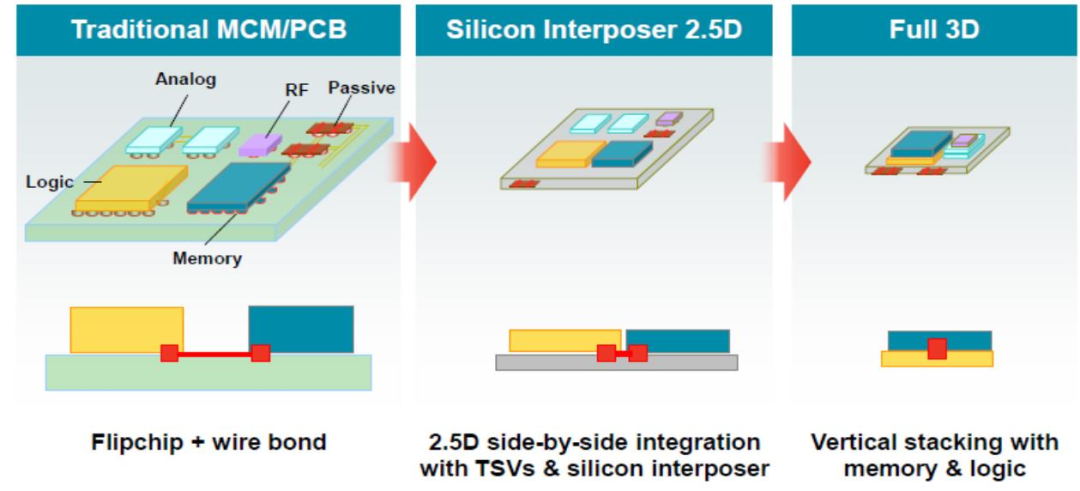

HBM内存通常具有1024个I/O通道,英伟达最新Rubin芯片组的HBM4为提高数据带宽,将I/O通道增加到了2048个。

不同版本HBM内存技术参数对比 来源:行家说三代半

而PCB使用的是有机材料,线宽/线距高达数十微米,一方面无法在极小面积内完成上千级信号走线。另一方面,HBM要求的TB/s级带宽需要极短距离才能维持信号完整性,而PCB厘米级的互连长度会导致严重的信号衰减和延迟。

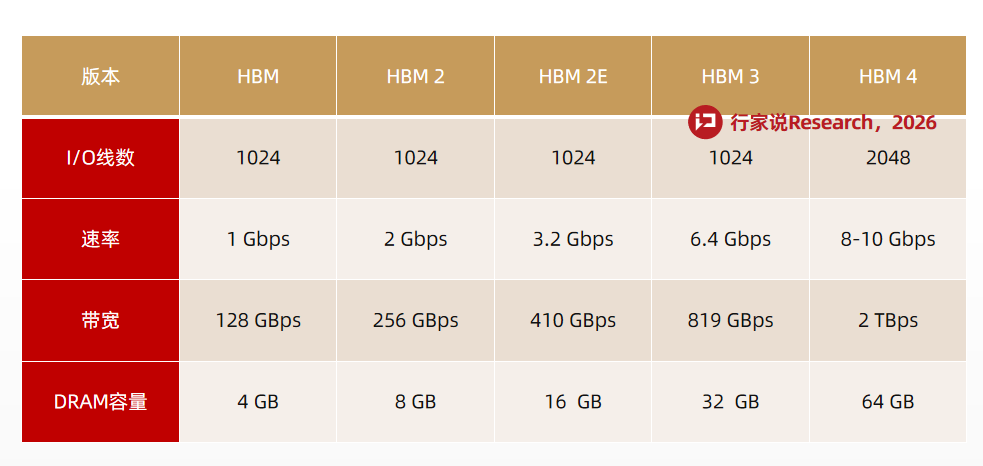

2D封装与2.5D封装的尺寸对比 来源:新加坡A*Star科技局

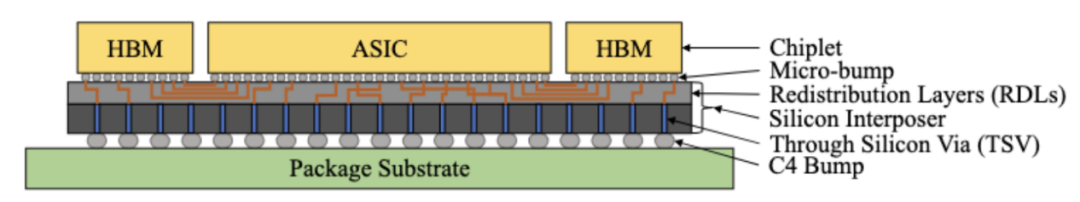

中介层是通过高密度水平互连与超短垂直互连的组合,同时解决芯片间的横向通信带宽和纵向对外连接的瓶颈问题。

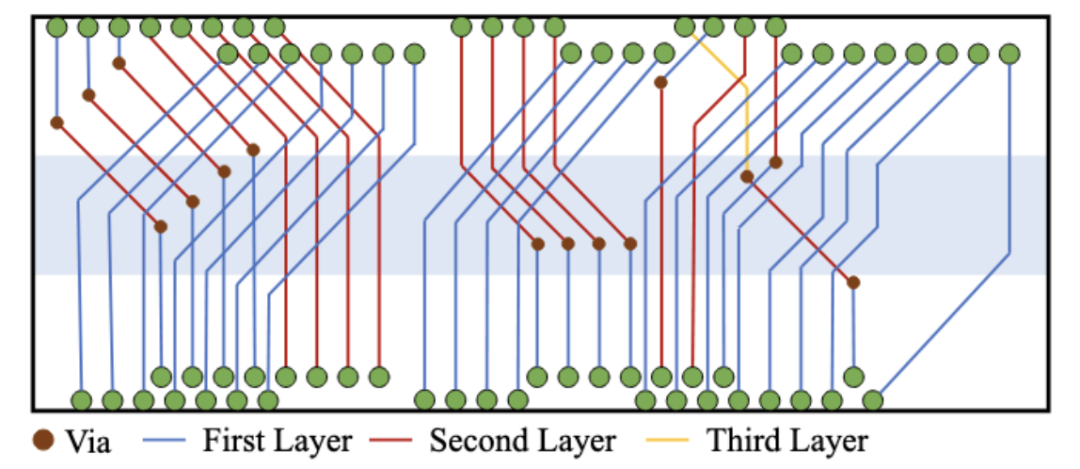

例如,硅中介层的微米级RDL布线,能够在芯片边缘布设超千条通道,实现GPU与HBM间的TB/s级带宽,并显著降低功耗;而硅通孔(TSV)可实现约100微米超短垂直互连,能够以极低阻抗支撑大电流瞬态响应,确保供电稳定与信号完整性。

CoWoS-S结构(上);硅通孔与多层布线(下) 来源:香港中文大学(2025)

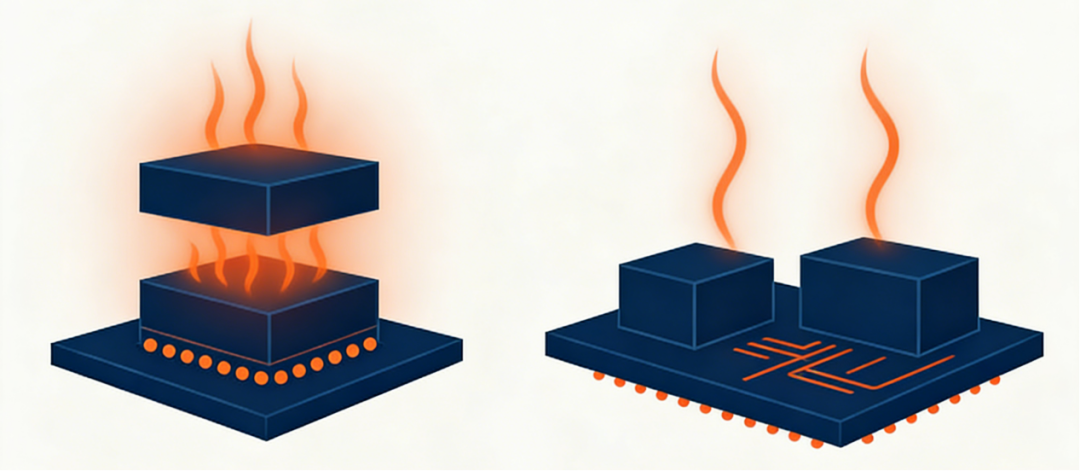

其次,3D封装虽然理论性能上限更高,但目前面临较大挑战。一方面,芯片需背磨将晶圆减薄至50-100μm,增加工艺步骤、成本和碎片风险;另一方面,3D堆叠后的芯片还需要进行KGD等可靠性验证流程,增加了交付周期,而2.5D使用已知良品裸片(KGD)。此外,热管理也是3D封装需要解决的重要问题。

3D封装与2.5D封装的散热对比示意图

如前文所说,中介层不是某一种材料,它是一种结构。

根据核心材料的不同,常见的中介层结构可分为:硅中介层、再分布层(RDL)、嵌入式硅桥(LSI)、玻璃中介层,还有SiC中介层、金刚石中介层和陶瓷中介层等。

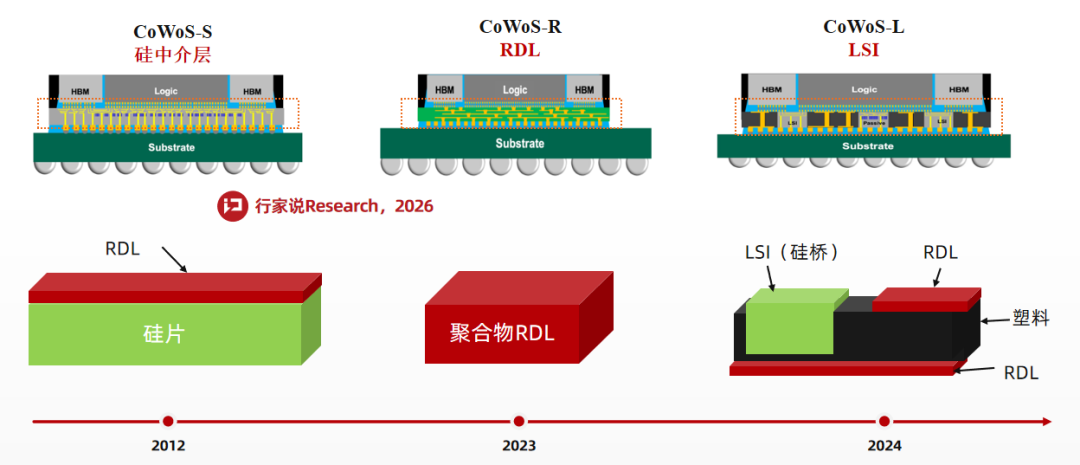

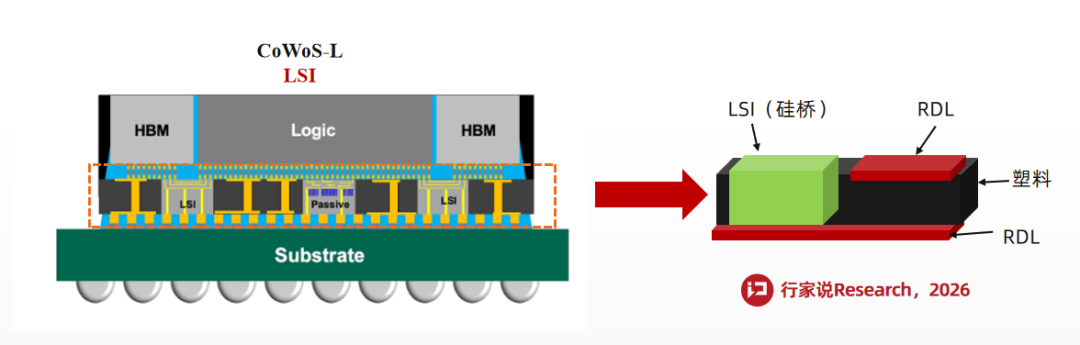

以台积电的CoWoS为例,CoWoS-S的硅中介层,其实是由硅片和再分布层(RDL)组成;CoWoS-R的中介层主要是由聚合物RDL组成;而CoWoS-L的中介层则由硅桥小芯片(LSI)、RDL和塑料构成。

台积电CoWoS的不同中介层材料 来源:行家说三代半

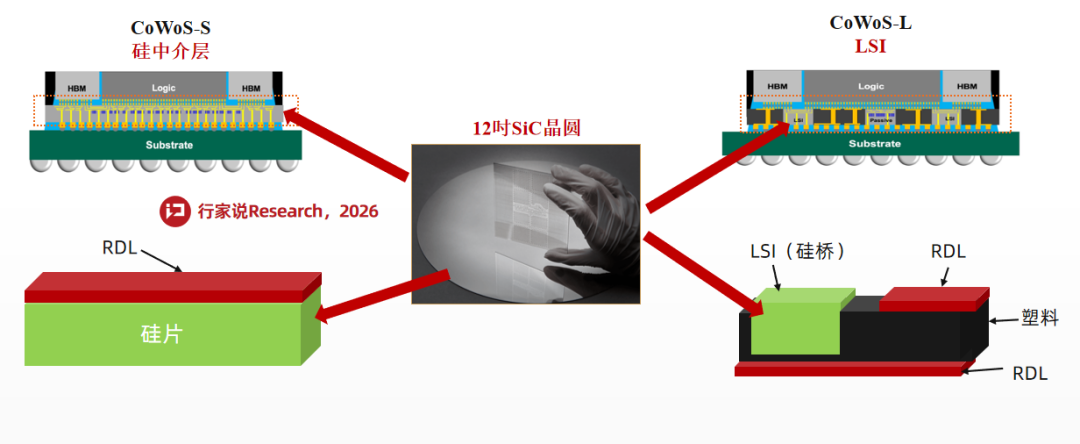

众所周知,SiC衬底可以在CoWoS-S中替代硅中介层。同时,在CoWoS-L中,SiC也可以做成小芯片,替代硅桥(LSI)。

SiC衬底在CoWoS封装中的应用 来源:行家说三代半

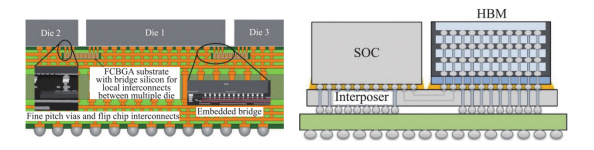

事实上,除了台积电,其他科技巨头的HPC芯片也采用硅桥(LSI)芯片,所以理论上,SiC也有机会被英特尔、三星等企业所采用。

英特尔EMIB(左)和三星I-Cube (右)的中介层都采用硅桥(LSI)

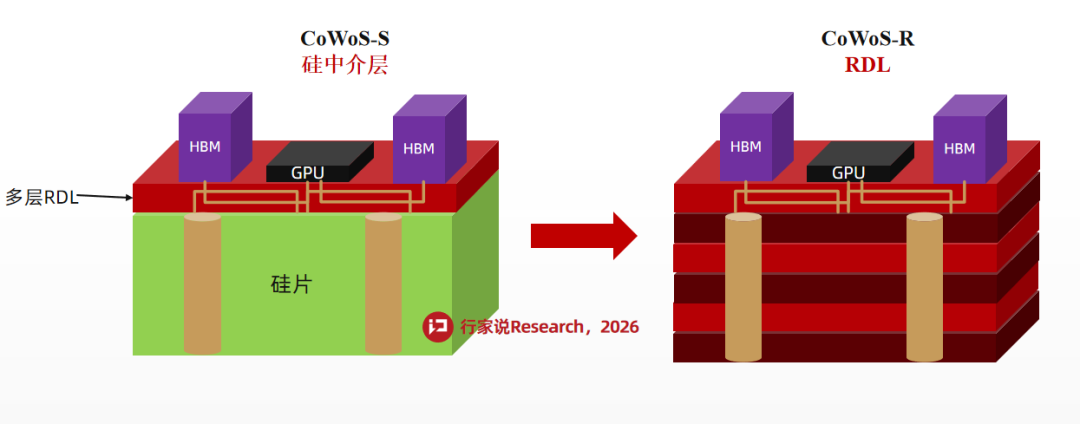

而CoWoS-R则不会采用SiC,因为CoWoS-R的中介层结构取消了硅片,改用有机聚合物。

台积电CoWoS-S与CoWoS-R的中介层材料变化

前面提到,台积电CoWoS的封装,从CoWoS-S发展到CoWoS-R和CoWoS-L,未来还可能走向CoPoS封装。那么,台积电为什么要进行这样的迭代?CoWoS-S遇到了什么问题?

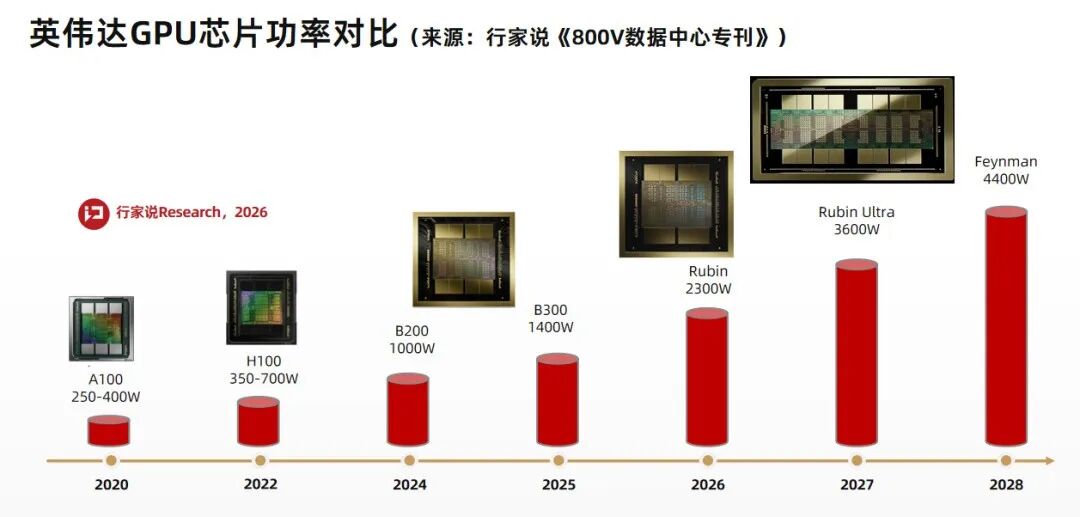

GTC2026大会上,英伟达发布的Rubin和Runbin Ultra等功率分别达到2300W和3600W,未来的费曼架构GPU功率预计将突破4400W。而这对CoWoS封装的散热能力构成极大的挑战。

2025年美国佛罗里达大学对CoWoS和EMIB等高密度2.5D封装进行仿真和实验,其研究表明,当芯片组总功率超过600-700 W时,中介层的热点温度可超过120°C。因此,如果CoWoS封装的散热方案不改变,可以预料Rubin和Runbin Ultra的中介层温度将会更高。

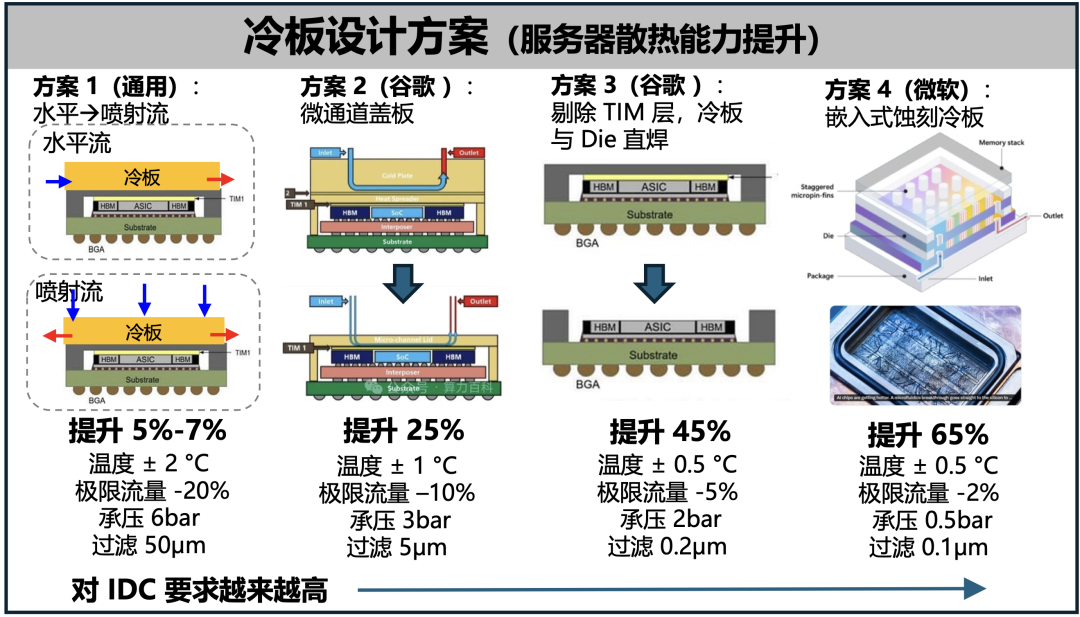

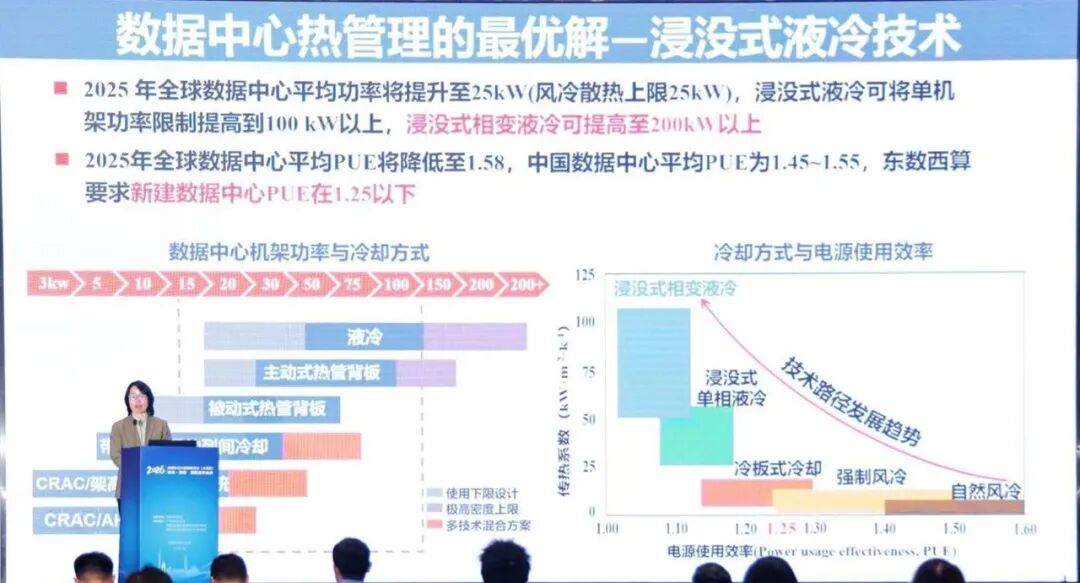

因此,英伟达最新一代GPU通常需要部署芯片级液冷技术,而在机架层面的散热方案正从传统的风冷转向冷板式或浸没式液冷。字节跳动在其下一代数据中心超节点技术构想中也强调了液冷技术。

不同企业的HPC芯片散热方式 来源:腾讯数据中心

调研结果显示,这些新型散热技术的支持功率也是有上限的,而且成本不断翻倍增长。根据中国科学院过程工程研究所数据,风冷散热上限为25kW,浸没式液冷可将单机架功率限制提高到100kW以上,而浸没式相变液冷可提高至200kW以上。

现阶段这些技术还够用,但要如何应对Runbin Ultra和费曼等更高功率GPU的散热要求?

美国佛罗里达大学的研究还提到,在2.5D异构封装系统中,硅中介层的面内导热性是优异的(@600-700W),热导率高达约150W/m/K,但是也存在2个问题:

一是硅中介层的横向热导率显著降低,从而导致AI/HPC加速器的芯片之间的温差达到两位数。

二是硅中介层的热膨胀系数与有机基板不匹配,会导致翘曲和应力,引发封装可靠性问题。

为此,该研究结构提出了2个解决方法,包括:使用具有更高热导率的中介层和基板,例如SiC/AlN等高热导率材料;以及将中介层用作主动热层,在层内添加微流体通道来实现局部冷却。

不同中介层材料的对比 来源:行家说三代半

因此,假设未来12英寸碳化硅成本达到较为合理的位置,它在2.5D先进封装的应用是可以帮助HPC芯片厂商解决散热的大麻烦。

那么散热是不是碳化硅中介层唯一的比较优势呢?事实上,综合多篇论文研究结论显示,它还可以为先进封装提供3个益处。

首先,新加坡A*Star科技局在论文中提到,与传统硅中介层相比,碳化硅不仅可以改善散热性能,还可以提升中介层的机械强度性能。

其次,半绝缘碳化硅可提高HPC芯片组的信号传输完整性。

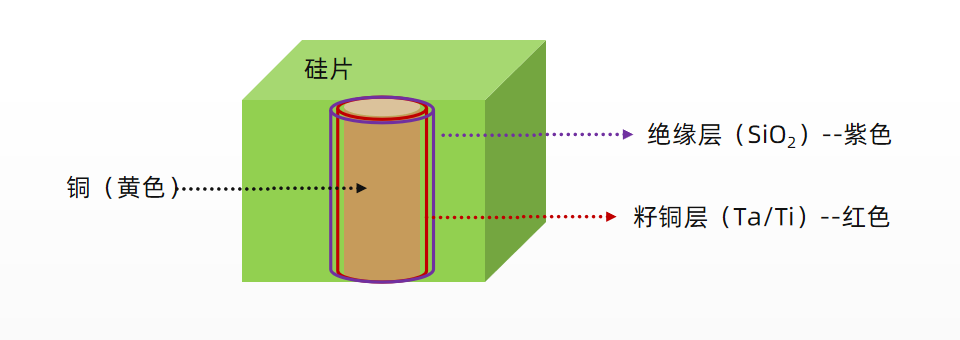

这是因为硅通孔在进行铜填充时,为防止铜向硅衬底扩散,通常需要先沉积绝缘层实现电隔离,再沉积阻挡层/籽铜层阻止铜扩散,从而占用通孔内部空间,使铜填充的有效横截面积减小,从而导致TSV的电阻有所升高,一定程度上会导致GPU与HBM信号的传输延迟。

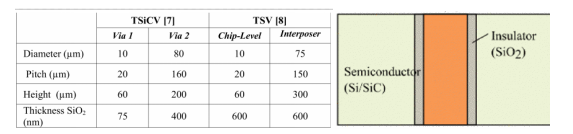

硅通孔与铜填充内部示意图 来源:行家说三代半

而新加坡A*Star科技局的研究表明,碳化硅通孔(TSiCV)技术可以实现更好的垂直信号布线,相比硅通孔的SiO2绝缘层厚度可以减少三分之一,从而降低RC阻抗并提高信号完整性。

碳化硅通孔与硅通孔的对比 来源:新加坡A*Star科技局

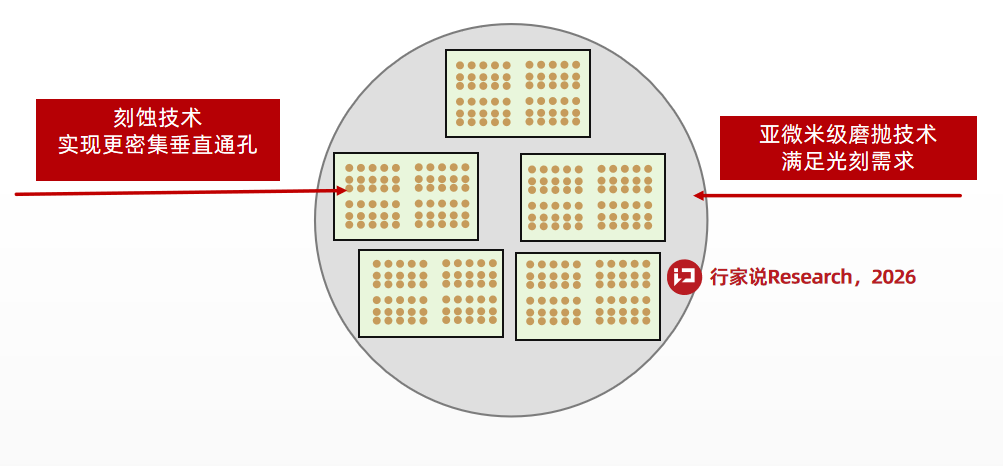

第三,碳化硅中介层还有望帮助进一步缩小先进封装的尺寸。

2024年美国杨百翰大学采用新型光电化学刻蚀方法,将SiC中介层通孔的深宽比提高到109:1(而硅通孔的最高研究水平是25:1)。更高的深宽比,理论上意味着SiC中介层能够在更小的水平面积内,实现更深、更密集的垂直互连——碳化硅通孔刻蚀通常需要通过光刻,因此对SiC衬底的表面粗糙度提出了更高的要求,亚微米级的磨抛技术是实现精细布线的关键步骤。

碳化硅中介层的关键技术 来源:行家说三代半

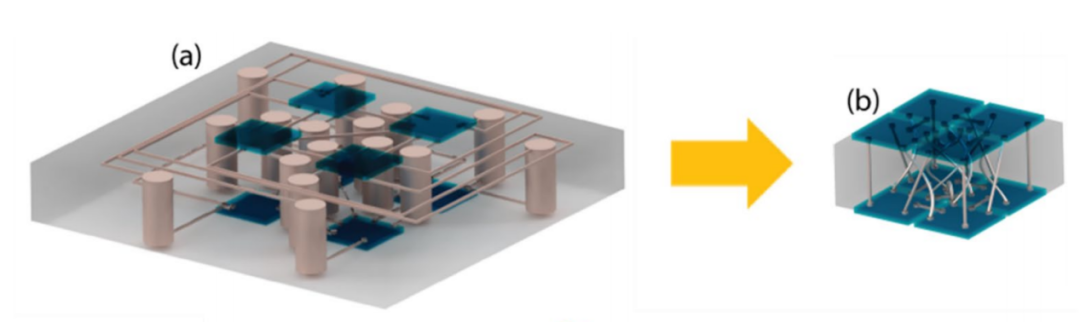

此外,杨百翰大学的研究还实现了非直线的通孔,可为2.5D封装带来更多的可能性,更为难得的是该研究实现了约2μm/分钟的高刻蚀速率,且不受通孔形状与复杂度影响。

碳化硅非直线通孔(右)可缩小中介层尺寸 来源:美国杨百翰大学

小结一下,SiC中介层对于CoWoS封装的价值不只是导热率,还有其他多项“宝藏”功能等待挖掘,当然也需要更多的研究实验去证明。

从调研信息来看,这次英伟达GTC2026发布的Rubin和Runbin Ultra等高端GPU的封装形式已经从CoWoS-S转向了CoWoS-L。而且根据摩根士丹利预测,英伟达CoWoS-L的占比高达85%以上,2025年需求约39万片,2026年将增长至70万片。

而摩根士丹利对CoWoS-S占比的预测呈现下降趋势:2025年占英伟达总需求的11%,2026年预计仅约2.5%。

要了解CoWoS-S份额下降,我们先要了解它的封装工艺流程。

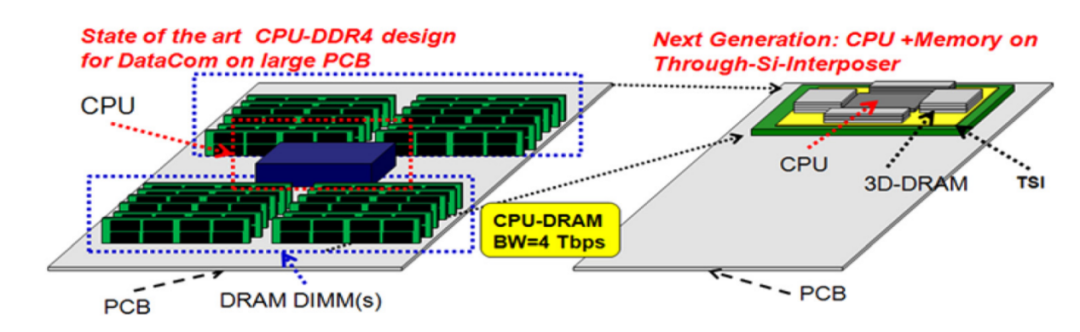

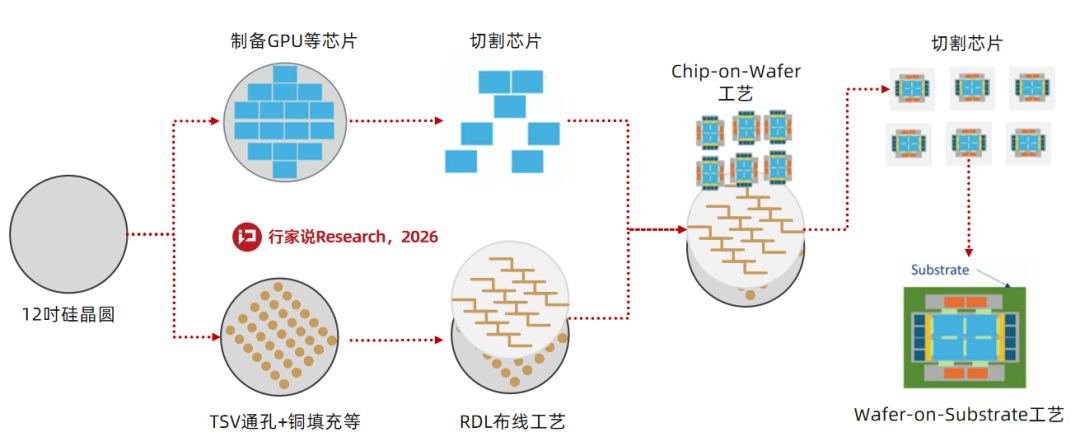

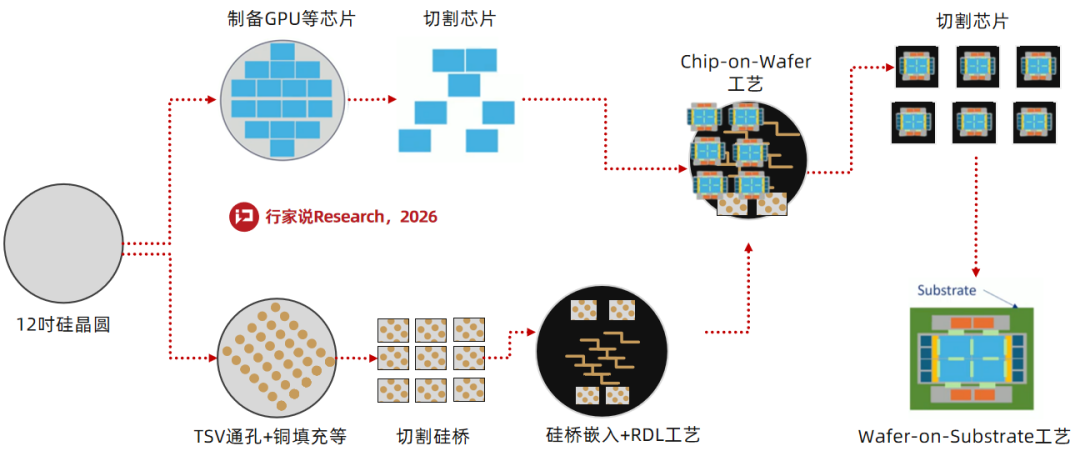

CoWoS-S通常是采用整片12英寸硅晶圆进行中介层的制作(硅通孔、铜填充、RDL布线等),然后将切割好的GPU、HBM等芯片放置在硅中介层上面,再完成后续的CoW和WoW等工艺。

台积电CoWoS-S封装工艺流程示意图 来源:行家说三代半

根据调研,CoWoS-S封装的成本是最高,超过1200元/颗以上,它主要的成本卡点在于硅中介层,有2个因素导致硅中介层的成本居高不下。

三类不同中介层CoWoS封装的对比 来源:行家说三代半

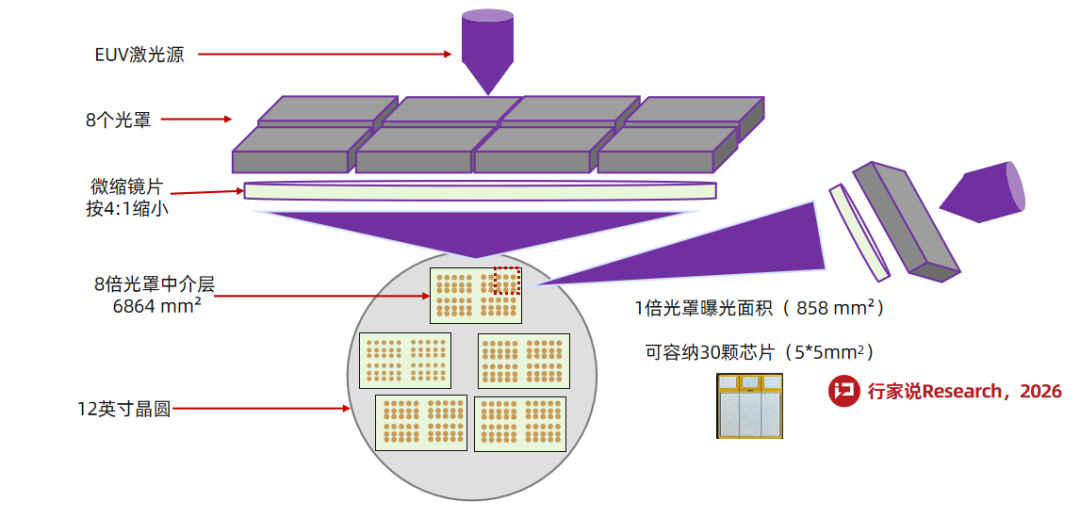

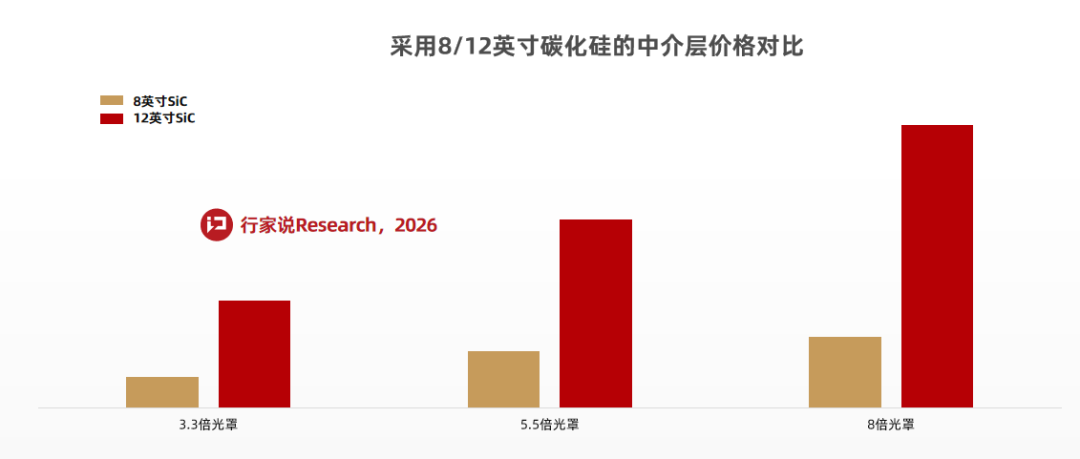

首先,随着GPU芯片组尺寸越来越大,硅中介层的尺寸将大幅提升——从3.3倍光罩迈向5.5倍光罩,甚至8倍以上。

英伟达GPU与中介层尺寸对比 来源:行家说三代半

而由于硅中介层的尺寸越来越大,光刻的难度也越来越高。据台积电论文,其第五代CoWoS-S采用双掩模和四掩模光刻拼接技术,才制备出3倍光罩的硅中介层。论文提到,虽然CoWoS-S可以扩大到4倍光罩(约3300mm2),但生产效率、良率和可靠性方面的挑战也随之而来。因此,硅中介层的成本也是水涨船高的。

一倍光罩与八倍光罩中介层的光刻示意图 来源:行家说三代半

其次,整片12英寸晶圆制备硅中介层,导致晶圆浪费严重。根据日月光研发中心副总经理洪志斌博士的说法,由于硅中介层尺寸变大,每片12吋硅晶圆可切割的硅中介层芯片越来越少(一般少于50颗),导致2.5D封装的制造成本也随之大幅上升。

而CoWoS-L则可以大幅降低中介层的成本,并且解决台积电的产能交付瓶颈问题。我们先回顾一下前面提到的CoWoS-L的中介层结构图。

与CoWoS-S采用整片数倍光罩的硅中介层不同,CoWoS-L是将多颗小尺寸的硅桥(LSI)芯片嵌入到塑料晶圆中。

CoWoS-L的中介层结构示意图 来源:行家说三代半

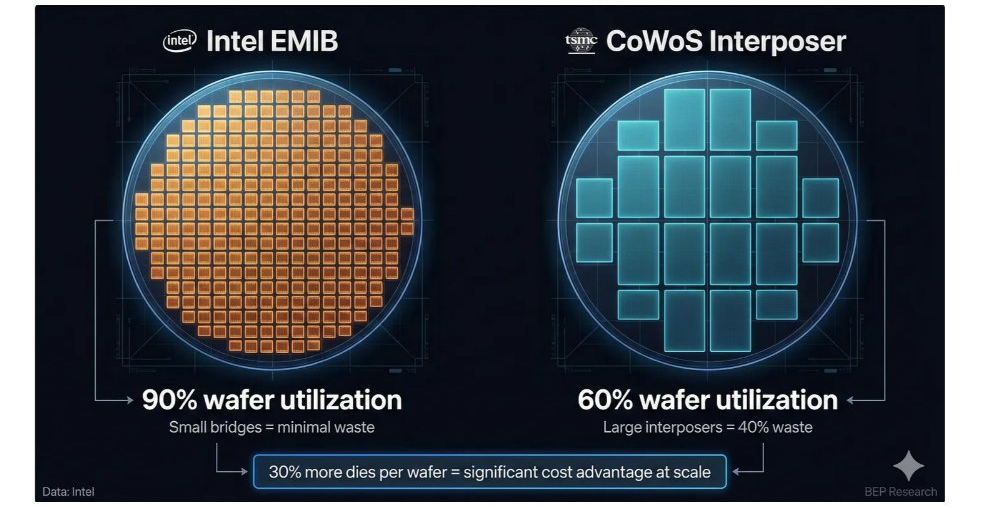

这种“以小换大”的思路,有点类似特斯拉和小鹏等企业将全SiC碳化硅模块换成混合SiC模块,一方面可以减少硅中介层的用量,降低成本,另一方面是可以提升晶圆的利用率。

根据英特尔的分析,小硅桥芯片的晶圆利用率比大尺寸硅中介层高出30%,从而可以转换为成本的节省。

2种中介层的晶圆利用率对比 来源:英特尔

同时,采用小硅桥芯片可以大幅提升CoWoS-L的生产灵活性,我们再来它的工艺流程图。

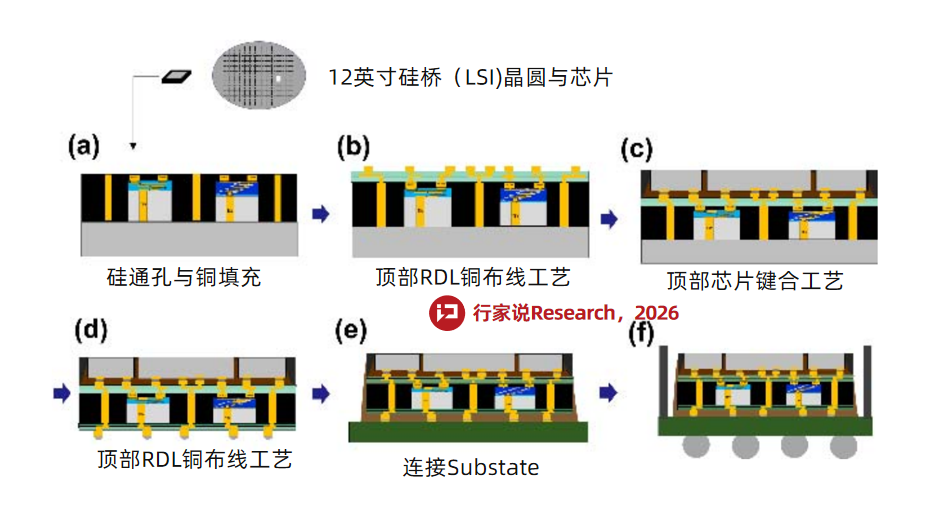

CoWoS-L是先在12吋硅晶圆中制备硅桥(LSI),再切割成小芯片。然后再将芯片嵌入到塑料晶圆或者其他面板上,再完成RDL布线等工艺。

台积电CoWoS-L封装工艺流程示意图 来源:行家说三代半

不同于CoWoS-S,硅中介层受限于晶圆的尺寸,硅桥小芯片则可以转移到不同尺寸的晶圆或者面板上,为后续的提升产能和降低成本奠定了基础。

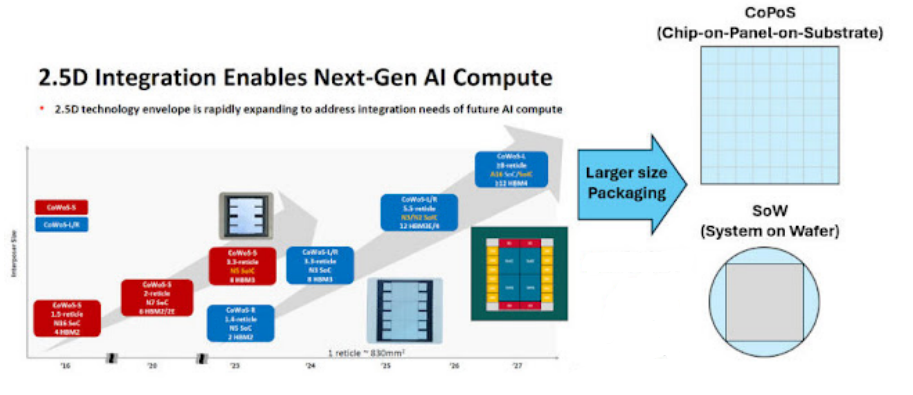

2.5D封装技术路线图 来源:台积电

根据台积电的预测,CoWoS-L的成本比CoWoS-S低15%-20%,而且不影响性能,因为CoWoS-S的硅中介层的性能是过剩。

日月光洪志斌博士曾写道,硅中介层的L/S可以达到0.5μm/0.5μm,而RDL的L/S约为 2μm/2μm(台积电是1.4μm/1.4μm),因此并不影响互连密度。而且并非所有应用都需要一样高的L/S,例如逻辑芯片和HBM等需要高速传输的芯片连接可以用LSI芯片(L/S与硅中介层一样),而其他区域可以采用RDL,这样不仅可以兼顾封装密度和带宽的需求,还能以相对较低的制造成本,为市场提供不同的解决方案。

未来CoWoS-L的份额会越来越高,而它采用的是LSI小芯片,采用碳化硅的可能性会不会发生变化?

事实上,在英伟达Rubin、费曼等更高功率GPU芯片中,可能CoWoS-L的散热挑战会更大。

一方面,CoWoS-S可以通过大面积的硅中介层进行散热,而CoWoS-L只是局部引入硅桥芯片,而RDL等其他区域的散热性能较弱,容易形成局部热点。

另一方面,CoWoS-L采用混合结构,结合了硅桥和RDL。硅、中介层与基板之间的热膨胀系数不匹配会导致封装翘曲(warping),这不仅影响生产良率,还会造成热界面材料(TIM)接触不良,增加热阻。据报道,这种CTE失配问题曾导致CoWoS-L产能爬坡困难。

而从成本角度,如果把碳化硅做成小尺寸的LSI小芯片,再导入到CoWoS-L中,这种方式的成本也比之前的CoWoS-S大尺寸SiC中介层更低,是不是也能提升台积电的导入意愿?

CoWoS-L封装流程示意图 来源:台积电

从碳化硅产业链的角度来看,目前台积电CoWoS-L采用硅桥LSI芯片还有2个降本的可能性:

一是硅桥LSI芯片基于12英寸晶圆制备,12英寸SiC衬底技术也逐步成熟,因此SiC尺寸将不再是短板,而尺寸固定后,更有利于SiC企业集中精力去完善技术工艺和成本优化,后续的供应也更有保障。

二是LSI芯片的制备可能还不用拘泥于12英寸,是否可以采用更便宜更成熟的6-8英寸SiC晶圆?这样成本效益似乎也不差。

现阶段8英寸与12英寸SiC中介层成本对比 来源:行家说三代半

还有一个问题,采用LSI芯片是否会减少碳化硅的需求量?

目前,“行家说三代半”没有检索到英伟达GPU的CoWoS-L硅桥芯片尺寸和用量数据,但英特尔的先进封装将在2026年采用超过20个EMIB硅桥,而未来将增加到38个-200个硅桥以上。

以上是“行家说三代半”的粗浅分析,如果错漏欢迎大家留言交流,帮助我们改正。

文章的结尾,我想引用刘胜院士在2026年2月的采访。在采访中,他是这样说的:

“现在大家都在谈论 Intel(英特尔) 押注的玻璃基板,因为它能做得很大,适合连接很多 HBM 内存。但玻璃有一个致命伤——它的导热性极差,几乎是硅的 1/150。

我们看到英特尔的封装实验室正在开发高密度的TGV(玻璃通孔)铜柱阵列,甚至尝试在底部填充胶里掺入金刚石微粉,试图在绝热的玻璃里开辟出一条‘导热高速公路’。

但如果追求的是极致的散热,SiC中介层有可能是真正的‘贵族方案’。它的导热效率是玻璃的几百倍。未来在那些热流密度极高的核心区域,我认为SiC中介层是重要的解决方案之一。”

本文发自【行家说三代半】,专注第三代半导体(碳化硅和氮化镓)行业观察。