国产破局!中安ZP8破10.5nm,助力半导体量检测设备国产化进阶

在

半导体

量检测领域,灵敏度每前进

1nm,都意味着对光学系统、机械控制与算法架构的极限挑战。最近,国内量测与检测领军企业中安

半导体

发布新一代颗粒检测设备 ZP8 及面向3D集成与衬底制造的两套系统化解决方案,其中ZP8实现了10.5nm极限精度,打破国际厂商长期在该领域的技术垄断。根据SEMI M35,ZP8的实测数据表明:对 10.5nm 颗粒的捕捉率(Capture Rate)已经达到了 95% 以上。

中安

半导体

市场应用

VP 初新堂表示:”通过对10.5nm最佳灵敏度的攻克,中安不仅是在挑战物理极限,更是为了确保当行业跨入3nm及以下节点时,我们的客户已经拥有一套成熟、稳定且高精度的良率监控方案。它的核心使命是面向未来越来越先进的设计节点!”

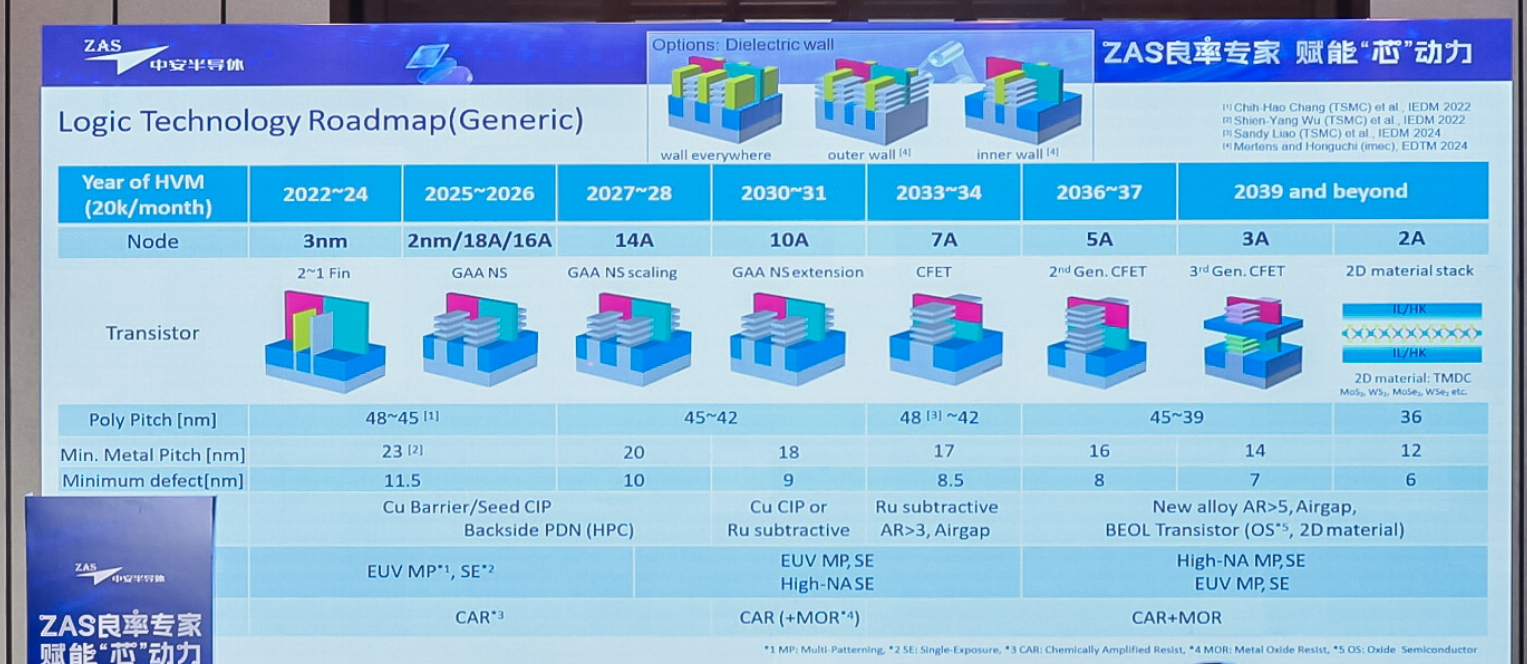

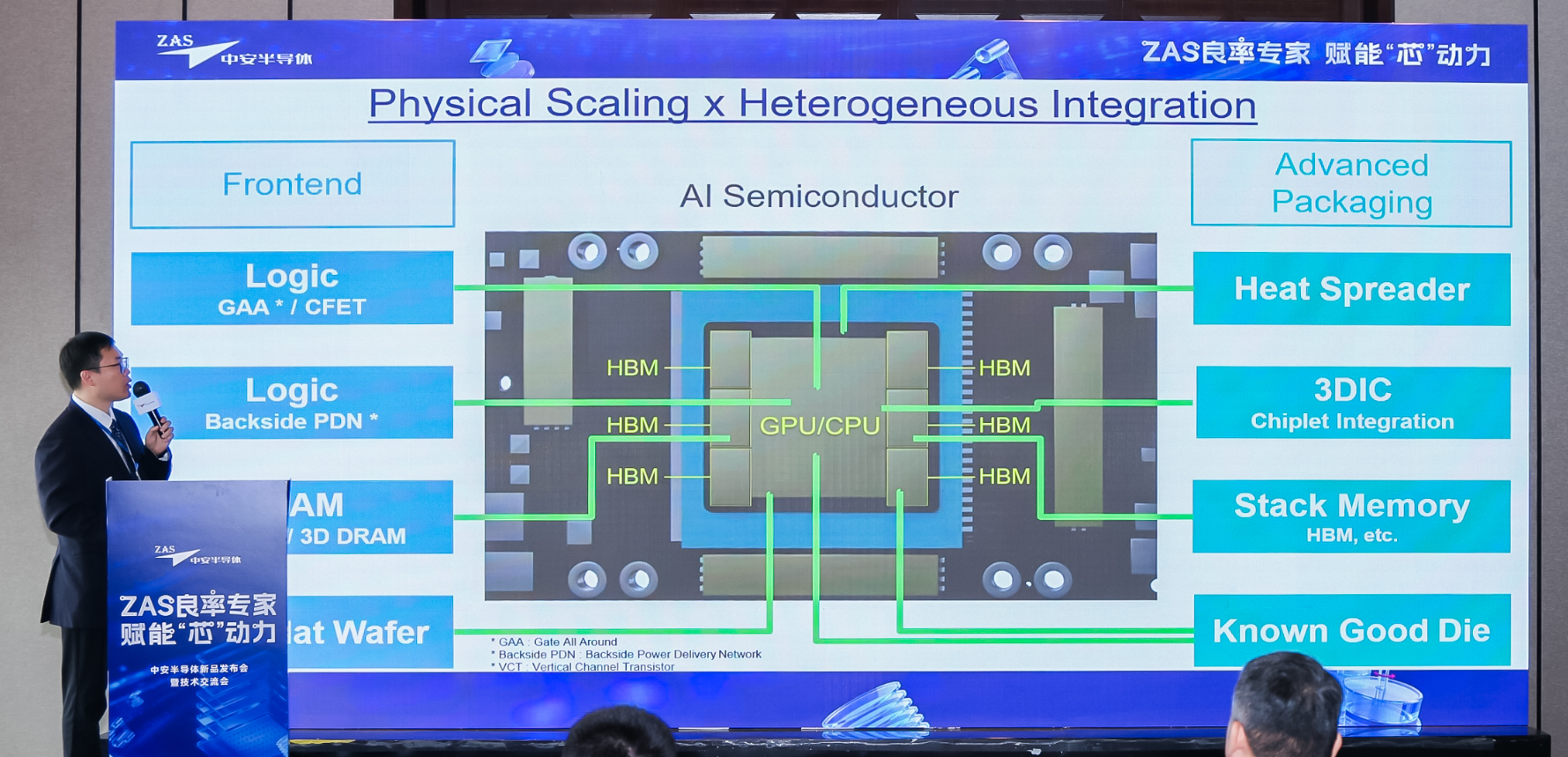

先进制程倒逼精度与范式的双重升级

高性能

AI

芯片

正驱动着

半导体

技术的全方位变革,涵盖了从先进制程逻辑

芯片

到背面供电(BSPDN),再到HBM(高带宽存储器)、先进封装以及3D IC等所有尖端领域。当前,

半导体

工艺向着5nm、3nm及以下尖端节点迈进,同时3D NAND堆叠层数持续攀升、DRAM三维化提速、背面供电与HBM先进封装快速普及,行业工艺复杂度呈指数级增长。微小缺陷、形貌畸变、应力不均等细微问题,都会引发

芯片

失效、良率暴跌,真正应验“失之毫厘,差之千里”的行业定律。这一演进过程,给工艺带来了两大挑战:

l

尺寸微缩的极限挑战:

随着特征尺寸越来越小,对晶圆(

Wafer)表面质量的要求已达到了近乎苛刻的程度。为了保证

芯片

的可靠性,市场对超平整晶圆(Superflat Wafer)的需求正成为主流。

l

堆叠架构的物理挑战:

在

3D IC和层叠技术中,随着堆叠层数的增加,形貌控制与翘曲(Warp)问题愈发凸显。会直接恶化 键合套刻精度(Bonding Overlay),并在后续光刻工艺中引发连锁性的对准误差(Misalignment),最终成为制约 3D 集成良率的核心物理瓶颈。

为什么在逻辑技术的演化路径中,颗粒检测(

Particle Counter)需要“先行一步”?

随着制程工艺的不断下探,逻辑节点每前进一步,对检测设备精度的要求就会随之发生质的飞跃。当行业进入

3nm 技术节点时,工艺对颗粒缺陷的捕捉能力基本需要达到 11.5nm 甚至更高。随着技术节点的更迭,能够被定义的“最小关键缺陷”尺寸正在持续收缩。曾经被视为“非关键”的微小颗粒,现在极易导致电路短路或失效。

“如果我们不能在量检测环节实现更小的突破,就无法为客户的先进制程提供有效的数据支撑。”

初新堂介绍:

“2024至2025年,公司保持半年一代的迭代节奏,检测灵敏度先后实现26nm、17nm、12.5nm的三级跳,此次发布的ZP8设备,更是实现跨越式突破,最佳检测灵敏度达到10.5nm。这种持续的更新迭代,不仅是中安创新能力的体现,更是我们对客户制程演进承诺的兑现”。

先进制程下的高灵敏缺陷检测,一直是国产

量检

测设备难以突破的壁垒,国际厂商长期占据技术高地。

中安

半导体

此次发布的

ZP8能够实现10.5nm的极致检测精度,并非单一技术的单点突破,而是

“光学+机械+算法”的全方位优化方案。

中安

半导体

并未止步于当前的技术突破,而是规划了清晰的迭代路线。据介绍,

ZP8将在今年正式推向市场,后续公司将持续优化升级,计划于明年推出面向15nm大规模量产(HVM)的新一代设备,在保障高精度的基础上,进一步提升设备产能与稳定性,全面适配客户规模化量产的严苛要求,提前卡位下一代制程检测需求。

范式跃迁:从

“事后检测”到“事前预测”的

监控变革

如果说

ZP8 解决了“极限尺度下的缺陷捕捉”,那么面对 3D 堆叠与异构集成,量检测的另一大核心战场在于全局形貌(Global Shape)与应力(Stress)的管理。

晶圆在经历

Edge Trim、研磨、等离子活化及 CMP 等多道工序后,累积的形貌畸变会在键合(Bonding)环节被指数级放大。 当两片晶圆开始接触并实施键合时,物理层面的微观变化极其复杂,其中最核心的挑战在于晶圆畸变(Wafer Distortion)及其他关键工艺参数的实时处理。在良率管理中,“Bonding Overlay(键合套刻精度)”和“Post-bond Litho Overlay(键合后光刻套刻精度)”至关重要。

Bonding Overlay

是

两片晶圆在键合过程中,由于物理接触产生的图形相对位移

;

Post-bond Litho Overlay是键合完成后,对后续光刻工艺产生的影响。

中安

半导体

打破传统事后检测模式,创新性推出

IPD(in plane displacement)算法解决方案,彻底改变“

测量

已发生结果”的被动模式,转向“预判未发生误差”的主动管控。其全流程量测链路:

l

Pre-bonding(键合前):对上下两片硅片进行独立量测与数据预处理。

l

In-process(键合中):通过双面量测数据耦合,极致提升键合时的对准精度。

l

Post-processing(后期处理):在完成边缘减薄(Edge Trim)与减薄磨削(Grinding)后,中安的设备能够对 Post-bonding Overlay 进行最终的闭环检测。

初新堂分享到:

“目前的实测数据显示,中安量测方案得到的数据相关性已超过90%。”从“预知”到“改善”,中安

半导体

通过全量数据量测,为工艺提供最优解。

从衬底的

源头制胜

,到全流程良率控制

纵观中安

半导体

的布局,其野心不止于单一设备的替代

,而是致力于构建一个横跨材料研发、前道制程及先进封装的

“全流程良率控制生态”。在衬底领域,

中安

半导体

将良率管控关口前移至晶圆制造源头,通过自研光学技术,将衬底微粗糙度量测极限稳定控制在

1.5nm以内。同时针对先进制程对超平整晶圆的极致要求,公司已在下一代产品中布局了高精度干涉

测量

、低噪声厚度

测量

模块、抗条纹印迹效应算法等多项革新性技术,为国内大硅片产业的技术升级提供核心设备支撑。

中安

半导体

表示:

“量检测设备的终极目标是服务于产线。我们深知,只有精准发现每一处微小缺陷,才能真正帮助客户提升生产良率,满足严苛的制造需求。”