台积电最新路线图曝光:N2U/A13/A12齐发,无需High-NA EUV!

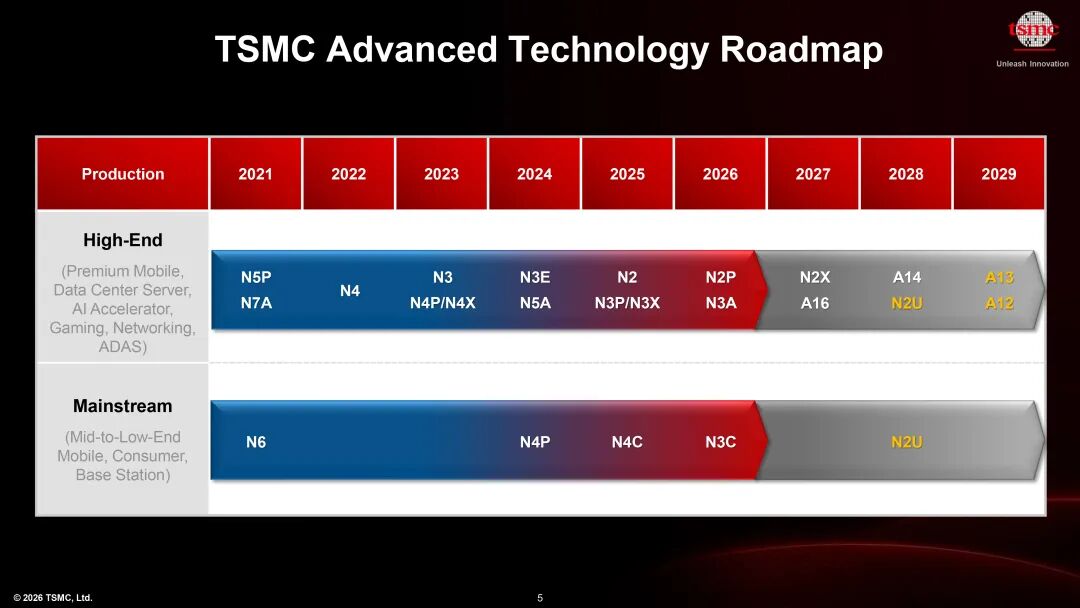

一、台积电工艺路线图概览:客户端与HPC应用走向分化

台积电在2026年北美技术研讨会上公布了至2029年的详细工艺路线图。台积电业务发展及全球销售高级副总裁兼副首席运营官张晓强(Kevin Zhang)博士在会上宣布,台积电正在采取一种刻意分化的战略——根据终端市场需求细分前沿工艺节点,而非采用一刀切的方式。

具体而言,台积电将实施新的工艺技术发布策略:每年为客户端应用推出一款新节点,每两年推出一款面向高负载AI和高性能计算(HPC)应用的新节点。

面向客户端(智能手机、消费电子)的节点:N2、N2P、N2U、A14、A13。这类节点强调成本、能效和IP复用,强大的设计兼容性至关重要,客户可接受渐进式改进。

面向AI/HPC数据中心的节点:A16、A12。这类节点必须提供显著的性能提升以证明技术过渡的合理性,成本相对次要。这些节点集成了Super Power Rail(SPR)背面供电技术,以解决AI数据中心的电源完整性和电流传输限制问题,更新周期为两年。

二、客户端新节点:A13光学微缩版与N2U增强版

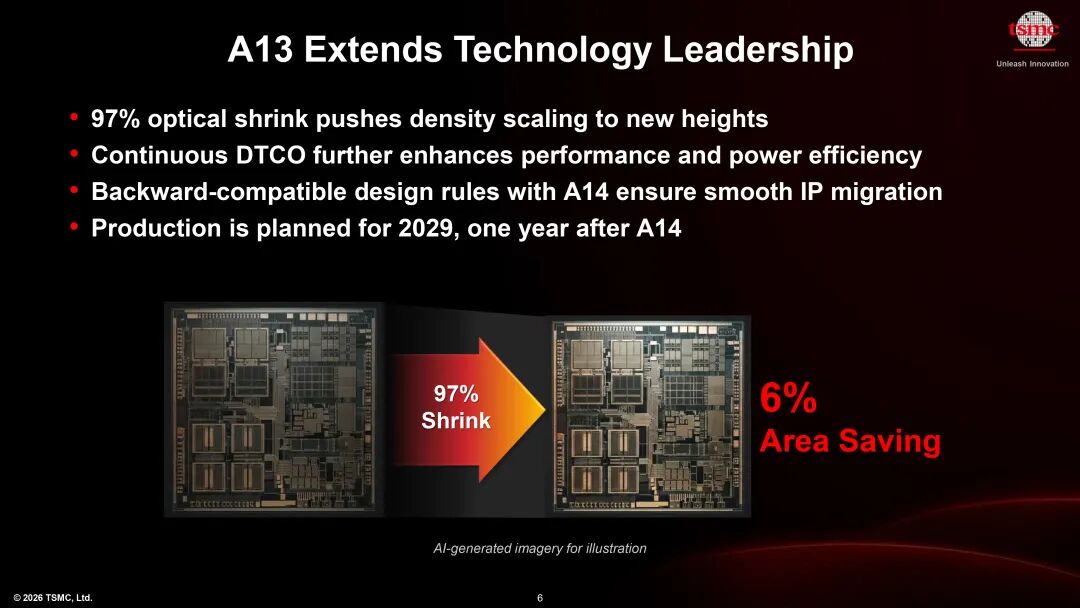

1、A13:A14的光学微缩版

张晓强表示:“去年我们发布了基于最先进的第二代纳米片技术的A14制程,计划于2028年投产。今年,我们将发布A14的衍生版,包括A13和A12,均计划于2029年投产。”

其中,A13是A14的光学微缩版,通过设计-技术协同优化(DTCO)实现。A13将线性尺寸缩小约3%,在保持与A14完全兼容的设计规则和电气特性的前提下,面积缩小约6%,晶体管密度相应提升。

张晓强解释称:“A13是在A14基础上进行改进,主要通过光学尺寸缩小实现,在保持完全符合设计规范和电气兼容性的前提下,使客户只需进行少量重新设计即可受益。”

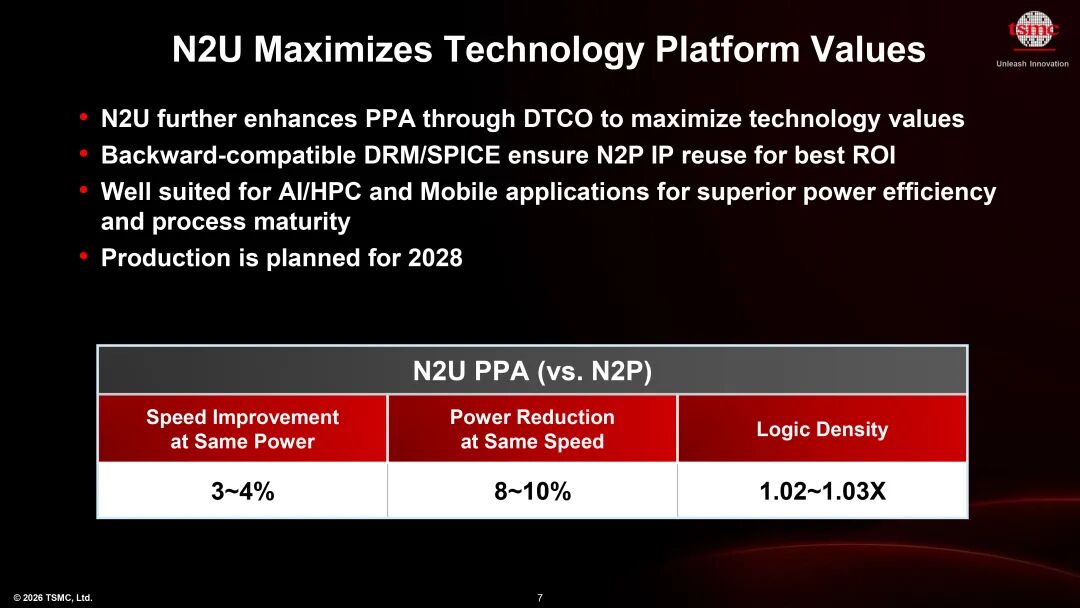

2、N2U:N2平台的第三年延伸

除了A13,台积电还宣布了全新的N2U制程,这是N2平台的第三代延伸版本。N2U同样利用DTCO技术,在N2P的基础上提供进一步优化:在相同功耗下性能提升约3%-4%,或在相同速度下功耗降低8%-10%,逻辑密度提升2%-3%。

N2U将保持与N2P IP的兼容性,使客户无需迁移到全新制程即可构建新产品。例如,使用N2P工艺实现的高端产品IP,可在2028年用N2U制程制造中端产品。张晓强表示:“我们的策略是在推出后不断改进每个节点,使客户能够在最大化设计投资回报的同时,持续获得PPA(性能、功耗、面积)收益。”

三、AI/HPC专用节点:A16推迟至2027年,A12接力2029年

1、A16:首次引入背面供电,量产推迟至2027年

台积电的A16工艺是首款采用Super Power Rail(SPR)背面供电技术的节点,专为高性能数据中心应用定制。本质上,A16是N2P加上背面供电,将使用第一代纳米片GAA晶体管,在功耗、性能和晶体管密度上显著优于N2和N2P。值得注意的是,台积电将A16的量产时间从原定的2026年推迟至2027年。

张晓强解释称:“A16将于2026年准备就绪,但实际量产取决于客户需求,我们预计量产将于2027年开始。这就是我们将其时间表调整到这个时间点的原因。”

与A16并行的还有N2X——N2P的性能增强版本,采用传统正面供电方式,将基于N2的设计时钟频率推至极限。A16的推出并不会取代N2X。

2、A12:第二代背面供电,2029年接棒

A16的接力棒将传递给A12——预计于2029年推出的下一代AI/HPC专用节点。A12将采用台积电第二代纳米片GAA晶体管和NanoFlex Pro技术,并继续使用背面供电(SPR),同时在正面和背面进行微缩以实现整体密度提升。

张晓强表示:“A16是我们第一代拥有超强功率轨(背面供电)的技术。A12是下一代技术,它将继续缩小正面和背面的尺寸,从而实现整体密度提升。”

四、暂无High-NA EUV计划:将持续挖掘现有EUV潜力

台积电路线图最引人注目的特点之一是:A13和A12均无需使用High-NA EUV光刻设备,台积电计划至少到2029年继续使用现有的低数值孔径EUV设备。

这与英特尔的路线图形成鲜明对比——英特尔计划从14A节点(2027-2028年)开始引入High-NA EUV。

张晓强对此表示:“说实话,我对我们的研发团队感到非常钦佩。他们不断探索如何在不使用高数值孔径设备的情况下推动技术规模化发展。或许将来有一天他们不得不使用高数值孔径设备,但就目前而言,我们仍然能够充分利用现有EUV技术的优势,而无需转向高数值孔径设备——要知道,高数值孔径设备的成本非常非常高。”

据路透社报道,High-NA EUV设备单台价格高达4亿美元,约为现有EUV设备的两倍。台积电副共同首席运营官张晓强对路透社表示:“这是我们研发团队做得特别出色的地方——在利用现有EUV技术的同时,制定了积极的技术微缩路线图。这绝对是一个优势。”

五、先进封装:从芯片微缩到系统集成

除了逻辑制程的微缩,台积电在此次研讨会上也强调了先进封装在延续摩尔定律中的关键作用。

据路透社报道,TechInsights副主席Dan Hutcheson表示:“摩尔定律正在从封装中的单片单芯片转变为多芯片封装。这使得性能和功耗的增益得以持续。”

台积电表示,到2028年,将有能力拼接10个大芯片和20个内存堆栈。相比之下,当前的AI产品(如Nvidia即将推出的Vera Rubin)仅包含两个大计算芯片和八个HBM堆栈。

不过,芯片拼接也带来了新的挑战。More Than Moore首席分析师Ian Cutress指出,大尺寸芯片封装在运行时会产生热量,不同材料的热膨胀系数差异可能导致封装弯曲甚至开裂——这些问题曾在Nvidia的Rubin AI处理器中出现,而台积电并未明确说明如何解决这些挑战。

六、其他工艺:N2A和N16HV

除了前沿节点,台积电还宣布了面向车用市场的N2A工艺——这是首款采用GAA晶体管的车规级制程技术。N2A在相同功耗下速度较今年投产的N3A提升15-20%,预计于2028年完成AEC-Q100认证。

在成熟工艺方面,台积电今年将率先将高压技术引入FinFET晶体管技术,推出面向显示驱动芯片(DDIC)的N16HV工艺。该工艺较N28HV栅极密度增加41%,功耗降低35%。

行业交流、合作请加微信:icsmart01

芯智讯官方交流群:221807116