芯片巨头,官宣1.2nm!

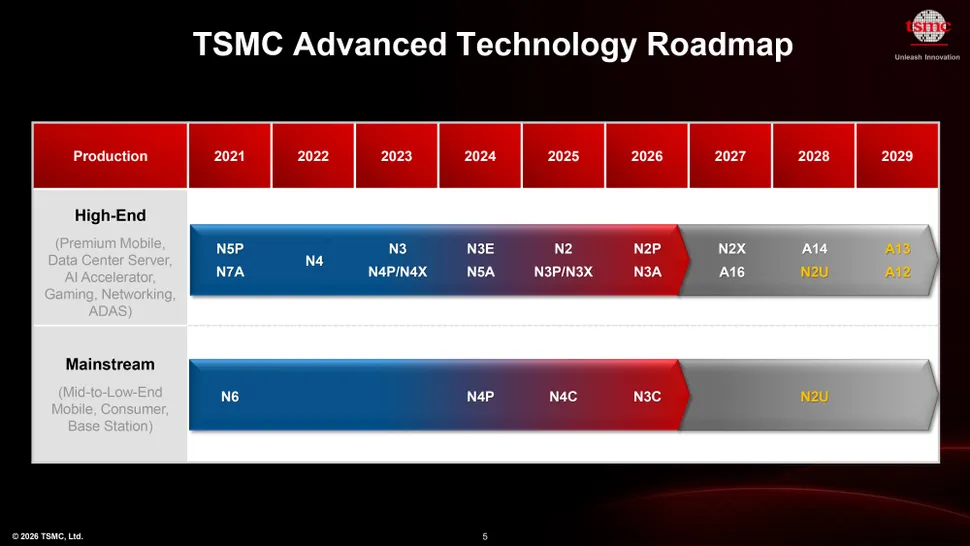

当地时间,4月22日,台积电在北美技术研讨会公布了其2029年之前的通用制造技术路线图。首次介绍了其A12(1.2nm)和A13(1.3nm)制造工艺。

并表示2029年之前,不准备使用 ASML 的高数值孔径极紫外光刻(High-NA EUV)设备。

2025年,台积电官宣了A14技术,预计于2028年投产,A14采用第二代环栅(GAA)纳米片晶体管,并借助NanoFlex Pro技术提供更大的设计灵活性。

A14 在性能、功耗和晶体管密度方面,都将较前代进一步提升,而且台积电判断这一节点在量产时仍不需要 High-NA EUV。

图源:台积电

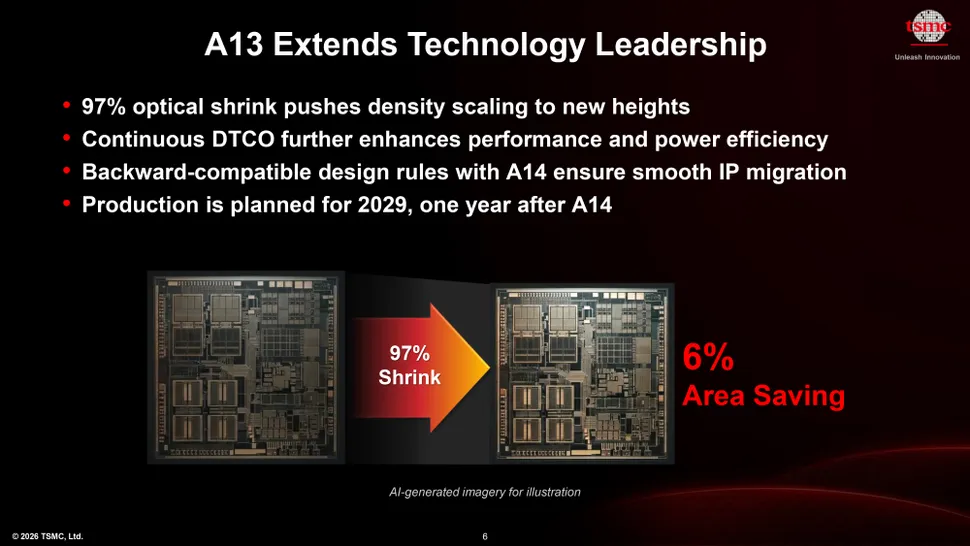

A13 是建立在 A14 之上的演进型节点,目的是以最小的干扰提升效率。

主要通过将线性尺寸缩小约3%(达到约97%的比例),在保持完全符合设计规则和电气兼容性的前提下,面积缩小了约6%。

相比于A14,A13通过设计技术协同优化(DTCO)实现渐进式增益,而无需对现有设计进行任何更改。

A13预计将于2029年投入生产。

图源:台积电

A12为A16的的优化版本,将采用台积电第二代纳米片 GAA 晶体管和 NanoFlex Pro 技术,预计为台积电的数据中心级节点带来全节点优势。

主要面向人工智能和高性能计算 (HPC) 应用的节点,集成了超强电源轨 (SPR) 背面供电技术,以解决人工智能数据中心和高性能计算工作负载的电源完整性和电流传输限制。

在性能、功耗和晶体管密度方面提供切实的提升。

注:台积电公布的芯片密度为“混合”芯片密度,其中逻辑电路占比50%,SRAM占比30%,模拟电路占比20%。

图源:南华早报

准确来说,这次路线图最令人关注的是,台积电再次表示:在 2029 年之前,不准备使用High-NA EUV。2025年,台积电就公开表示 A16 和 A14 都不需要 High-NA EUV。

而这次新路线图进一步说明,至少在未来几代节点上,台积电仍认为通过现有 EUV 平台加上工艺和设计协同优化,依然可以继续把节点往前推进。

相比之下,英特尔已经计划在14A 上导入 High-NA EUV。

消息数据来源:汤姆硬件、路透社

*文章内容仅为分享与讨论,不代表我方赞成或认同。部分图文素材源于网络,侵权请联系删除!

End

文章精选

2大巨头联手,建立全球最大 2nm 晶圆厂?

三星:利润增长近8倍,内存价格再涨30%

中国 AI 芯片厂商崛起,41% 国内市场份额!

又一国产晶圆代工厂递交香港IPO申请!

爆,安世中国将实现芯片全面国产化?

“在看”、“点赞”