台积电的客户该换策略了:每年一个小升级,还是两年一个大跳?

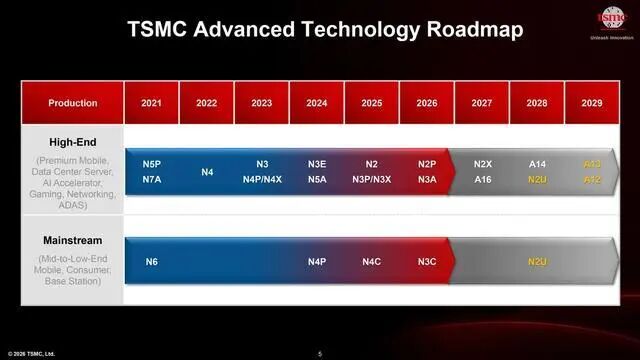

当地时间4月22日,台积电在美国加州举行“2026年北美技术论坛”,正式公布了延伸至2029年的先进制程技术路线图。本次论坛以“领先硅技术拓展AI”(Expanding AI with Leadership Silicon)为主题,系统梳理了从2nm到1.2nm级的完整制程图谱,并首次公开了A13和A12两大尖端工艺节点。

这是台积电年度规模最大的客户活动,北美场次将为未来几个月在全球各地举行的系列技术论坛揭开序幕。从此次披露的信息来看,台积电的制程战略正在发生深刻转变——从“节点竞赛”升级为“平台战争”,以先进逻辑、特殊制程与先进封装三路并进,全面抢占AI、HPC与行动运算市场。

路线图的底层逻辑发生转变

这次路线图最值得关注的,不是某个节点参数有多漂亮,而是台积电首次系统化地公开了“分轨”策略。

业务发展及全球销售高级副总裁兼副COO张晓强(Kevin Zhang)说得直截了当:公司将根据终端市场需求对前沿节点进行分化,不会再对所有客户“一刀切”地推进同一个节点。

两套节奏,泾渭分明:

面向客户端(智能手机、消费电子)路线: 每年推出一款新节点。成本、能效和IP复用是核心,设计兼容性至关重要。客户要的是稳定、可预期的渐进式改进。

面向AI/HPC数据中心路线: 每两年推出一款。这类节点必须拿出显著的性能跃升才值得切换,成本相对次要。关键区别在于,这些节点集成了Super Power Rail(SPR)背面供电技术,专门解决AI数据中心在电源完整性和电流传输上的极限瓶颈。

这个调整不是拍脑袋来的。台积电过去的营收主力是智能手机,但近几年AI和HPC业务的增速已全面超越手机业务。最新路线图把这一结构性趋势摆在了明面上。

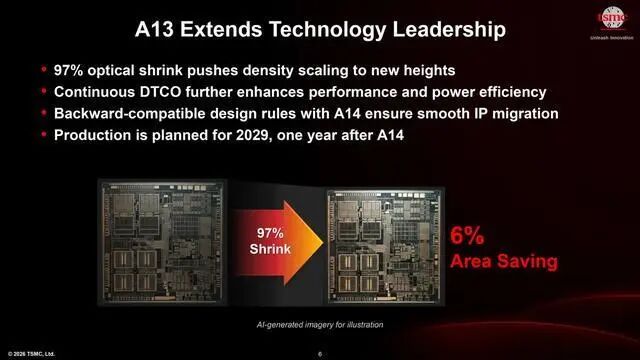

A13:面向客户端的“光学微缩版”

A13是本届论坛的明星节点。

台积电去年发布了基于第二代GAA纳米片晶体管的A14制程,预定2028年投产。今年亮相的A13,本质上就是A14的光学收缩版本(业内称为Optical Shrink)——换句话说,客户无需更换设计,只需切换到新工艺窗口,就能直接吃到密度提升的红利。

实现路径是设计-技术协同优化(DTCO):线性尺寸缩小约3%,芯片面积缩减约6%,晶体管密度相应提升,而设计规则和电气兼容性完全保持不变。客户要做的工作极其有限:重新设计一点点,额外效率增益就到手了。

张晓强介绍:“A13主要通过光学尺寸缩小实现,在保持设计规范和电气兼容性的前提下,使客户只需进行少量重新设计即可受益。”

从技术演进脉络看,这一做法延续了台积电通过光学缩放优化制程的传统,比如过去的N12、N6、N4和N3P。但与完整的节点跃迁不同,A13的增益属于温和的“微升级”:A14本身需要在功耗、性能和密度上完成全面突破,需要全新的工具、IP和设计方法配合;A13则借助DTCO在不变更设计的前提下“挤出”额外密度收益。

A13预计2029年进入量产。

N2U:N2平台的第三年“红利”

在2nm家族这边,台积电还意外公布了N2U——N2平台的第三年延伸版本。

逻辑与A13如出一辙,N2U在N2P的基础上通过DTCO做进一步优化。相同功耗下性能提升约3%-4%,或在相同速度下功耗降低8%-10%,逻辑密度再提升2%-3%。

其核心价值在于IP兼容性:使用N2P工艺打造的高端产品IP,到2028年可以直接用N2U制程来生产中端产品,无需迁移到全新制程就能推新。

张晓强对此总结道:“我们的策略是在推出后不断改进每个节点,使客户能够在最大化设计投资回报的同时,持续获得PPA收益。”

N2U预计2028年开始生产。

先进封装:CoWoS迈向14倍光罩,CPO今年量产

除了制程,先进封装是本届论坛的另一大重头戏。在AI算力需求持续爆炸的驱动下,台积电从CoWoS规格扩张到3D硅堆叠再到光电整合,完整勾勒出下一代AI芯片平台的演进蓝图。

CoWoS:从5.5倍到14倍,再到40倍

台积电目前已量产5.5倍光罩尺寸的CoWoS版本。下一步推进目标直指14倍光罩尺寸,预计2028年开始生产。做个对比更直观:相比当前的5.5倍版本,未来的14倍光罩CoWoS能在单一封装内塞进约10颗大型运算晶粒与20颗HBM堆叠,系统整体效能将迎来质的飞跃。

到2029年,台积电还计划推出超过14倍光罩尺寸的版本,并与同年登场的40倍光罩尺寸系统级晶圆技术(SoW-X)形成互补——晶圆级AI系统整合,已经写在了路线图上。

CPO:今年量产,光互连时代来临

台积电旗下紧凑型通用光子引擎(TSMC-COUPE)即将达成关键里程碑:采用COUPE on substrate的真正共同封装光学(CPO)解决方案预计于2026年开始量产。相比传统电路板上的可插拔光模组,新技术将光子元件直接整合至封装内部,功耗效率提升2倍,传输延迟降低达90%。该技术目前已应用于200Gbps微环调变器。

SoIC:3D堆叠再升级

在3D芯片堆叠方面,台积电规划于2029年导入A14对A14的SoIC 3D堆叠方案。相较现行N2世代的SoIC,晶粒对晶粒I/O密度可提升约1.8倍,芯片间数据传输带宽显著增强。

从整体布局审视,台积电正以“制程+封装”双轮驱动应对AI时代挑战。

写在最后

从A13到CoWoS再到CPO,台积电2026年北美技术论坛勾勒的不仅是一张制程路线图,更是一套完整的AI芯片时代竞争方略。在“领先硅技术拓展AI”的主题下,台积电正在重新定义先进制程的演进规则——速度、兼容性、封装能力与系统整合正成为同样重要的竞争维度。这场始于圣塔克拉拉的年度盛会,已经为全球半导体行业未来三年的技术走向定下了基调。

- END -

推荐关注