光电子芯片突破材料边界:晶圆键合到底解决了什么?

随着光电子芯片向更高集成度、更低功耗、更多功能方向发展,单一材料已无法满足需求。硅、InP、氧化物、新型光电材料各有所长,如何让它们 “协同工作”?答案是:晶圆键合。

它不仅是 “粘合技术”,更是光电子芯片突破性能天花板的核心支撑。

一、行业绕不开的痛点:材料不兼容、集成难度大

不同材料热膨胀系数差异大,易开裂、分层

传统工艺无法实现纳米级对准

键合良率低,难以工程化

加工 — 测试 — 封装链条断裂,研发周期长

晶圆键合通过高精度界面控制与材料适配,从根本上改善这些问题。

光谷实验室单片集成感知验证平台,正是以晶圆键合为核心,打通从材料集成到芯片出货的全链条,让异质集成不再难。

两大键合技术:撑起异质集成的核心骨架

Wafer to wafer 整片键合

适用于大面积、一致性高的集成需求,键合层薄至10~20 nm,良率可达90% 以上。

支持尺寸:2–6 寸晶圆

材料体系:Si、InP、SiO₂、Si₃N₄ 等全系列兼容

键合层厚度:10~20 nm

键合良率:≥90%适合光芯片、探测器阵列、硅光集成等整片流片需求。

Die to wafer 芯片级键合

适用于小芯片、高精度贴装,对准精度可达 ±0.5 μm,满足三五族器件、异质探测器等研发需求。

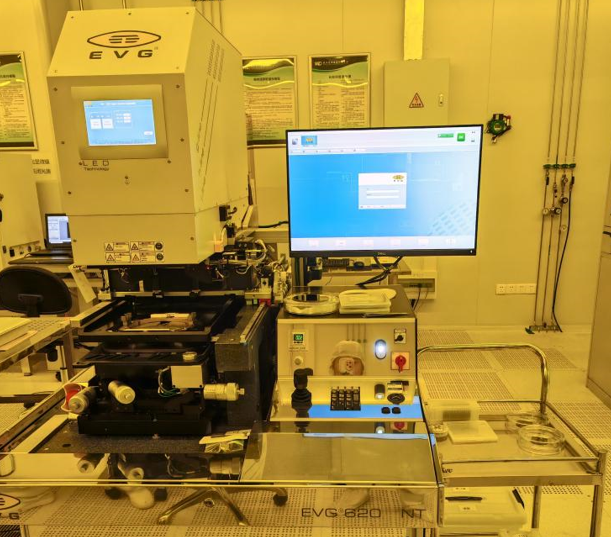

核心设备:FC300 高精度耦合设备

对准误差:±0.5 μm

键合层厚度:10~20 nm

键合良率:≥80%适合三五族器件、异质集成芯片、微型光电模组研发打样。

芯片全流程加工:从键合直接到可测试器件

在键合基础上,完整工艺可实现:硅基无源结构 + Ⅲ‑Ⅴ 有源器件一体化制造最小线宽150 nm,波导粗糙度5 nm,为高性能光电子芯片提供稳定基础。

平台可直接承接异质异构集成芯片全流程加工:

DUV 步进光刻、ICP 刻蚀、LPCVD/PECVD、电子束蒸发

硅基无源波导 + Ⅲ-Ⅴ 有源器件全流程制备

介质层沉积、图形化、金属电极制备

关键指标:

最小线宽:150 nm

套刻精度:±50 nm

波导表面粗糙度:5 nm

侧壁垂直度:89°

有源二极管输出功率:10 mW

完整支撑体系:不止于加工,更在于可验证

1.自主 CMOS 读出电路(ROIC)

640×512 阵列、15μm 像元、低噪声、高电荷收集效率,兼容 InGaAs、量子点、有机薄膜等探测器。

2.高端成像测试

单像素成像、光谱压缩成像、时域压缩成像,覆盖 X 光 / 紫外 / 可见光 / 红外 / 太赫兹全波段。

3.X 射线标准测试

DQE(IEC 62220-1)、闪烁体光产额测试,数据权威可直接发文。

4.封装与可靠性

TCO 制备、激光刻蚀、金线键合、COB/TO/ 气密性封装,-55℃~95℃高低温、85℃/85% RH 1000h 老化,纳米级失效分析,精准定位失效原因。

未来,光电子芯片的竞争,很大程度上是异质集成能力的竞争。而晶圆键合,正是这场竞争的关键入场券。

作为全国首个单片集成感知验证平台,已服务清华、北大等60 + 高校与科研院所,支撑数百篇高水平论文与多项国家级重点项目。

无论你是做光芯片、异质集成、红外探测、医疗影像、硅光、新型感知,都能在这里实现:晶圆键合 → 芯片加工 → 测试验证 → 报告发文 一站式完成。合作联系:梅老师 13618635885