最新成果

氮化镓(GaN)高电子迁移率晶体管(HEMT)已成为推动高功率密度、高转换效率与高频电力电子技术持续发展的核心引擎。目前GaN HEMT在消费类电子领域已经获得广泛应用并充分体现其性能优势,与此同时GaN HEMT也正在逐步切入对器件可靠性要求更为苛刻的车载电子、工业电子等应用领域。随着数据中心、新能源汽车、智能电网等应用领域对大功率电源越发强烈的需求,同步会要求功率芯片的工作结温越来越高。2025年比亚迪推出了基于SiC功率芯片的千伏/兆瓦级电动汽车闪充技术,其中SiC功率芯片的最高工作结温已达到200 oC。虽然,当前GaN功率芯片的最高安全工作结温仍然是150 oC。但在更高温度下,GaN功率芯片的可靠性如何,器件的退化和失效机理又如何?深入剖析和理解相关问题是GaN功率器件迈向更高温度下安全工作的重要基础。

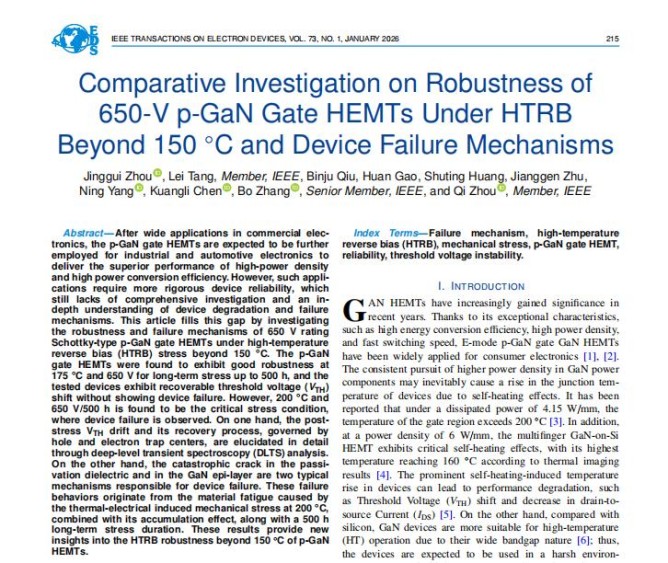

针对这一问题,电子科技大学张波、周琦教授团队对650V肖特基p-GaN栅HEMT功率器件在175 oC及200 oC高温下的器件退化特性及失效机制开展了深入研究,揭示了高温/高电场耦合作用下器件的鲁棒性极限及器件失效物理机制。实验发现,研究对比的两款器件在175℃/168小时的高温反偏应力(HTRB)下表现出良好的鲁棒性,虽然阈值电压(VTH)表现出不同程度的漂移,但器件未出现失效。然而,在200 ℃/500小时/650V的高温反偏应力下,两款器件均出现失效,分析表明200 ℃高温结合500小时的长时间应力积累是触发器件失效的关键因素。

图1 DUT-A和DUT-B在经历了条件分别为(a)175℃和168小时(b)175℃和500小时(c)200℃和168小时(d)200℃和500小时的HTRB应力后VTH的漂移与恢复特性。

陷阱电荷动态充放电与阈值电压漂移:

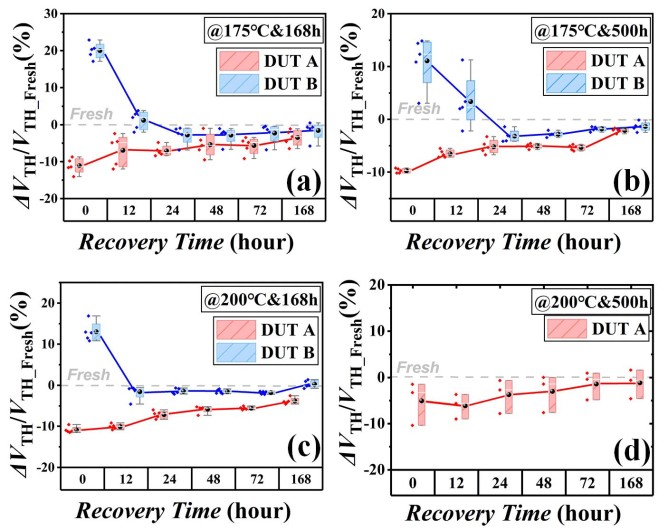

通过深能级瞬态谱(DLTS)分析,发现陷阱电荷在HTRB应力下的动态充电行为是导致阈值电压漂移的本质,但不同类型的陷阱电荷所引起的阈值漂移特性具有显著差别:

模式-A:空穴陷阱诱发的阈值电压负向漂移

通过分析发现HTRB应力下在器件场板边缘的高电场诱生热电子并进一步由热电子触发器件内部发生碰撞电离,碰撞电离过程中产生的空穴被AlGaN势垒层中能级位置为EV+0.6eV的空穴陷阱俘获,最终导致了HTRB应力过后器件阈值电压的负向漂移。

模式-B:电子陷阱诱发的阈值电压正向漂移

与之相反,200 oC/168小时HTRB应力过程中在gate/p-GaN界面产生了高密度的潜能级电子陷阱(1.25x1013 cm-3/EC-0.18 eV)。HTRB高压应力诱生的部分热电子翻越AlGaN势垒,被该电子陷阱俘获,导致了器件阈值电压的正向漂移。

器件在HTRB应力后经过长时间(~168小时)的自然恢复,由于陷阱电荷的本征去俘获效应,上述两类阈值电压的漂移都能恢复到HTRB应力前与本征器件的特性相当。

图2(a)未经受应力、经过(650 V、200℃、168小时)HTRB应力以及经过(650 V、200℃、500小时)HTRB应力后的DUT-A在不同DLTS测试偏压下的DLTS反馈信号;(b)相应的阿伦纽斯曲线;(c)未经受应力、经过(650 V、200℃、168小时)HTRB应力后的DUT-B在不同DLTS测试偏压下的DLTS反馈信号(d)相应的阿伦纽斯曲线。

应力失配及其积累效应与器件失效

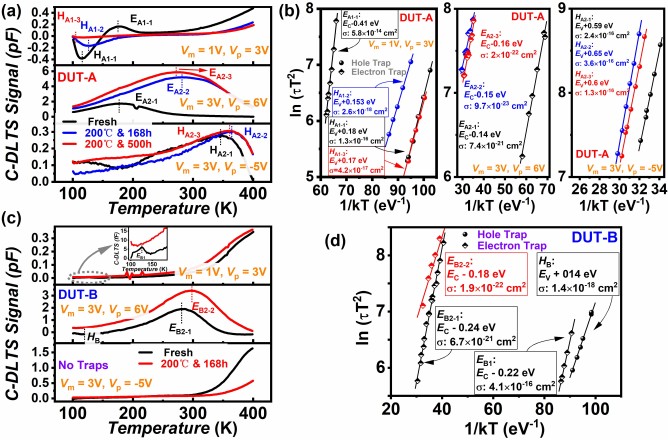

在器件失效机理分析研究方面,通过对在200℃/650V/500小时极端应力下失效器件的电学特性测试、OBIRCH定位、FIB-SEM截面分析以及COMSOL多物理场仿真,发现了两类典型失效模式:

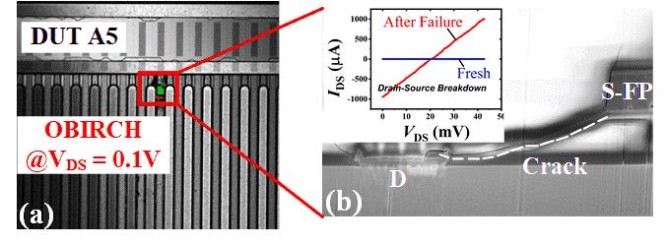

失效模式-I:“热-电”耦合应力导致材料界面应力失配及器件短路

在200°C高温与650V高反偏电压下,器件中不同材料(如SiO2钝化层、金属电极、III-氮化物外延层)因热膨胀系数(CTE)失配,在不同材料界面处产生显著的机械应力。同时,高电场通过逆压电效应在III-氮化物晶体中引入了额外的张应力。两种应力协同作用,经500小时长时间积累引发材料疲劳,最终导致钝化介质层发生横向贯穿性缺陷,造成栅、漏、源三端短路。

图3(a)失效的DUT-A样本去封装俯视图Vdc = 100 V;(b)基于OBIRCH的失效点位置;(c)源极、栅极和漏极之间可见的横向裂缝。

图4另一个失效的DUT-A样本:(a)基于OBIRCH的失效点位置;(b)漏极和源极场板之间钝化层中形成的裂纹。

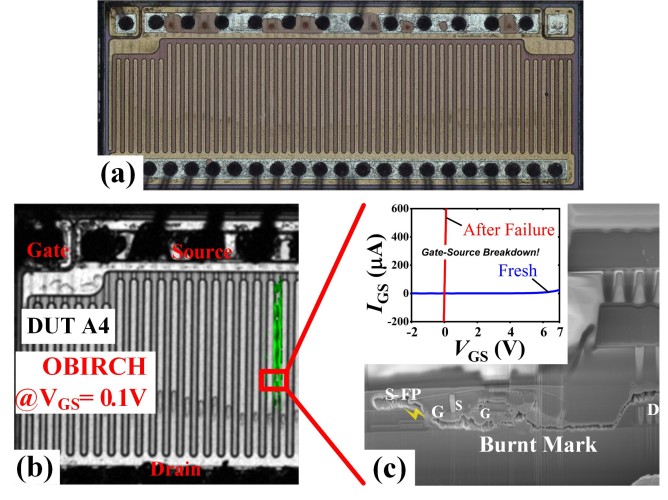

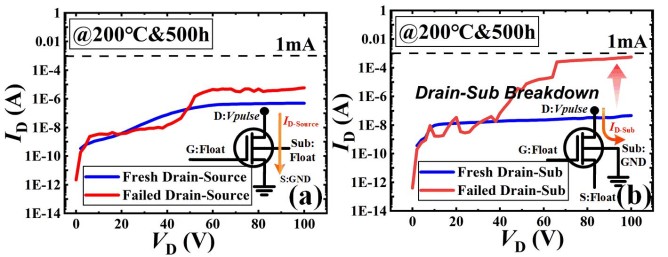

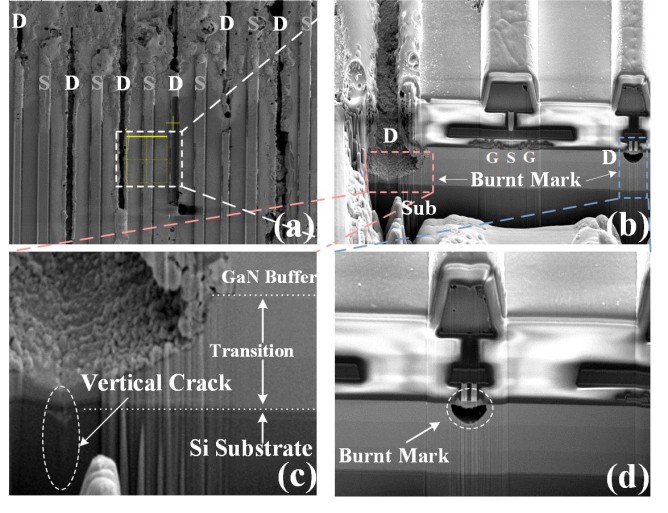

失效模式-II:漏极电应力诱生的GaN外延层纵向缺陷

长期高温高压积累效应导致材料疲劳,当局部应力超过屈服强度时,材料缺陷不再横向扩展,而是沿晶体结构强度较弱路径纵向延伸:从器件漏极向下延伸至硅衬底,形成纵向漏电通道。这导致关态漏电流急剧增大,局部焦耳热最终引发热失控和器件烧毁。与模式I不同的是,器件失效后栅极并未失效,栅极漏电几乎不变。

图5未经受应力的与经过(650 V、200℃、500小时)HTRB应力后的DUT-B的(a)漏-源(b)漏-地之间漏极电流对比。

图6 DUT-B失效分析(a)去封装俯视图;(b)失效器件的SEM横截面图;(c)漏极下方到衬底的垂直裂纹;(d)相邻漏极下的烧毁点。

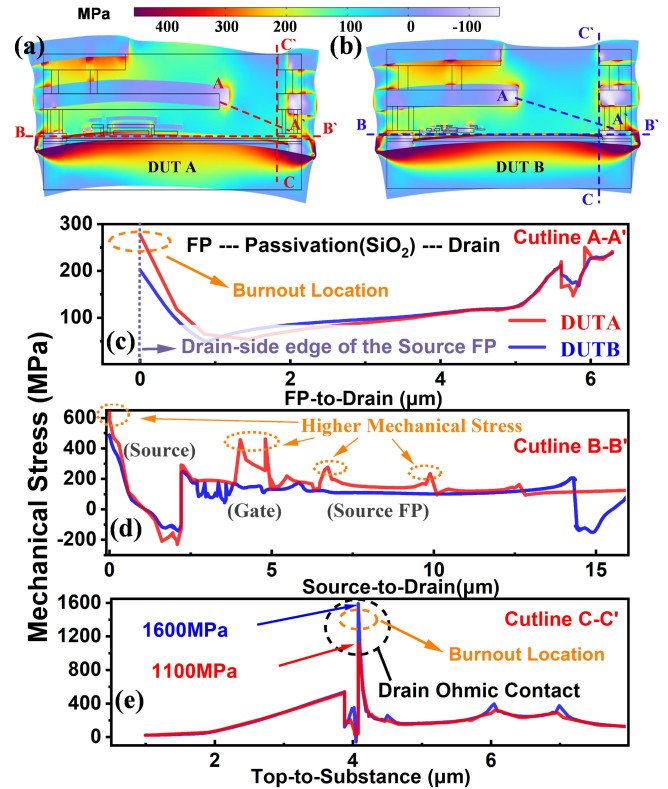

为了从理论上验证上述失效模型,研究团队利用COMSOL建立了包含电势、温度和机械应力的耦合仿真模型。模型参数基于实际器件的 TEM 形貌测量值,并引入了材料的热膨胀系数等关键物理常数。COMSOL仿真结果揭示了器件在200℃、650V条件下机械应力在器件体内的分布规律,与实验观测到的缺陷位置吻合。

图7 HTRB应力下(a)DUT-A与(b)DUT-B在COMSO仿真中的的机械应力分布;DUT-A与DUT-B沿(c)源极场板金属-钝化层-漏极路径(d)源漏间栅金属/p-GaN界面(e)漏极欧姆接触侧从顶部至衬底方向的机械应力分布比较。

该工作首次系统揭示了650V p-GaN栅HEMT在200℃高温/650V高压极端条件下的长期HTRB可靠性行为,明确了高温、高场、长时间应力耦合作用下的器件失效临界条件及其物理机制,为面向工业、汽车电子等高温、高可靠应用的GaN器件设计与工艺优化提供了关键理论依据。

研究成果以“Comparative Investigation on Robustness of 650-V p-GaN Gate HEMTs Under HTRB Beyond 150 °C and Device Failure Mechanisms”为题,发表于微电子器件领域权威期刊《IEEE Transactions on Electron Devices》。

相关工作得到国家科技重大专项、国家自然科学基金、广东基础与应用基础研究项目、中国博士后科学基金的支持。

论文链接:

1. https://ieeexplore.ieee.org/document/11296929